Reverse Engineering of Cache Replacement Policies in Intel Microprocessors and Their Evaluation

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Dual Core Processor Has Two Cores (Essentially, Two Cpus on One Chip)

Faculty of Engineering & Information Technology Al-Azhar University-Gaza Dr. Mohammad Aqel Microprocessors and Interfacing (ITCC 3301) Homework (1) Intel Core is a brand name used for various mid-range to high-end consumer and business microprocessors made by Intel. In general, processors sold as Core are more powerful variants of the same processors marketed as entry-level Celeron and Pentium. Similarly, identical or more capable versions of Core processors are also sold as Xeon processors for the server market. The current lineup of Core processors includes the latest Intel Core i7, Intel Core i5 and Intel Core i3, and the older Intel Core 2 Solo, Intel Core 2 Duo, Intel Core 2 Quad, and Intel Core 2 Extreme lines. 1- The original Core brand refers to Intel's 32-bit dual-core x86 CPUs. 2- Unlike the Intel Core, Intel Core 2 is a 64-bit processor, supporting Intel 64. The Core brand comprised two branches: the Duo (dual-core) and Solo (Duo with one disabled core). A dual core processor has two cores (essentially, two CPUs on one die (piece) silicon chip (IC)). Core2Duo is a specific dual-core processor design. Thus, all Core2Duo CPUs are dual-core CPUs, but not all Intel dual-core CPUs are Core2Duo designs. Core 2 is a brand encompassing a range of Intel's consumer 64-bit x86-64 single-, dual-, and quad-core microprocessors based on the Core microarchitecture. The single- and dual-core models are single-die, whereas the quad-core models comprise two dies, each containing two cores, packaged in a multi-chip module. -

CISC Processor - Intel X86

Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO CISC Processor - Intel x86 This chapter will introduce the CISC processors evolution. We will try to illustrate the history on one typical processor, because the comparison of multiple processors simultaneously would not be clear for readers. But the selection of one typical processor is complicated due to a variety of products and manufactures in the past 30 years. We have decided to describe in this presentation one of the best- known and longest mass-produced processors in existence. We definitely do not want to say that it is the best technology or that these are processors with the highest performance! The Intel x86 processors are the selected product line. Intel 8080 (Year-Technology-Transistors-Frequency-Data bus-Address Bus) Y: 1974 T: NMOS 6μm Tr: 6000 F: 2MHz D: 8b A: 16b This 8 bit processor is not directly the first member of x86 series, but it can not be skipped. It is one of the first commercially successful microprocessors. This microprocessor became the basis for a number of the first single-board computers and its instruction set inspired other manufacturers to develop 8-bit processors. -

Inside Intel® Core™ Microarchitecture and Smart Memory Access an In-Depth Look at Intel Innovations for Accelerating Execution of Memory-Related Instructions

White Paper Inside Intel® Core™ Microarchitecture and Smart Memory Access An In-Depth Look at Intel Innovations for Accelerating Execution of Memory-Related Instructions Jack Doweck Intel Principal Engineer, Merom Lead Architect Intel Corporation Entdecken Sie weitere interessante Artikel und News zum Thema auf all-electronics.de! Hier klicken & informieren! White Paper Intel Smart Memory Access and the Energy-Efficient Performance of the Intel Core Microarchitecture Introduction . 2 The Five Major Ingredients of Intel® Core™ Microarchitecture . 3 Intel® Wide Dynamic Execution . 3 Intel® Advanced Digital Media Boost . 4 Intel® Intelligent Power Capability . 4 Intel® Advanced Smart Cache . 5 Intel® Smart Memory Access . .5 How Intel Smart Memory Access Improves Execution Throughput . .6 Memory Disambiguation . 7 Predictor Lookup . 8 Load Dispatch . 8 Prediction Verification . .8 Watchdog Mechanism . .8 Instruction Pointer-Based (IP) Prefetcher to Level 1 Data Cache . .9 Traffic Control and Resource Allocation . 10 Prefetch Monitor . 10 Summary . .11 Author’s Bio . .11 Learn More . .11 References . .11 2 Intel Smart Memory Access and the Energy-Efficient Performance of the Intel Core Microarchitectures White Paper Introduction The Intel® Core™ microarchitecture is a new foundation for Intel® architecture-based desktop, mobile, and mainstream server multi-core processors. This state-of-the-art, power-efficient multi-core microarchi- tecture delivers increased performance and performance per watt, thus increasing overall energy efficiency. Intel Core microarchitecture extends the energy-efficient philosophy first delivered in Intel's mobile microarchitecture (Intel® Pentium® M processor), and greatly enhances it with many leading edge microarchitectural advancements, as well as some improvements on the best of Intel NetBurst® microarchitecture. -

Intel® Technology Journal the Original 45Nm Intel Core™ Microarchitecture

Volume 12 Issue 03 Published October 2008 ISSN 1535-864X DOI: 10.1535/itj.1203 Intel® Technology Journal The Original 45nm Intel Core™ Microarchitecture Intel Technology Journal Q3’08 (Volume 12, Issue 3) focuses on Intel® Processors Based on the Original 45nm Intel Core™ Microarchitecture: The First Tick in Intel’s new Architecture and Silicon “Tick-Tock” Cadence The Technical Challenges of Transitioning Original 45nm Intel® Core™ 2 Processor Performance Intel® PRO/Wireless Solutions to a Half-Mini Card Power Management Enhancements Greater Mobility Through Lower Power in the 45nm Intel® Core™ Microarchitecture Improvements in the Intel® Core™ 2 Penryn Processor Family Architecture Power Improvements on 2008 Desktop Platforms and Microarchitecture Mobility Thin and Small Form-Factor Packaging for Intel® Processors Based on Original 45nm The First Six-Core Intel® Xeon™ Microprocessor Intel Core™ Microarchitecture More information, including current and past issues of Intel Technology Journal, can be found at: http://developer.intel.com/technology/itj/index.htm Volume 12 Issue 03 Published October 2008 ISSN 1535-864X DOI: 10.1535/itj.1203 Intel® Technology Journal The Original 45nm Intel Core™ Microarchitecture Articles Preface iii Foreword v Technical Reviewers vii Original 45nm Intel® Core™ 2 Processor Performance 157 Power Management Enhancements in the 45nm Intel® Core™ Microarchitecture 169 Improvements in the Intel® Core™ 2 Penryn Processor Family Architecture 179 and Microarchitecture Mobility Thin and Small Form-Factor Packaging -

Intel Roadmap Directions 2006 a Resource Guide for Cios and IT Professionals

Intel Roadmap Directions 2006 A Resource Guide for CIOs and IT Professionals October – December 2006 Continuing its initiatives to constantly increase performance of desktop, mobile and server platforms, Intel now ushers in a path- breaking technology that is sure to change the world of computers. Intel has launched the industry's first Quad-Core processors that provide breakthrough performance and capabilities. Quad-Core Intel® Xeon® processors for the ultimate in powerful, dense and energy efficient servers and Intel® Core™2 Extreme Quad-Core processors for desktop platforms. This edition of the Intel Roadmap Directions gives you more information on the new Multi-Core microarchitecture for servers, desktops and shows you how they will impact the performance of your IT infrastructure. Redefining performance with Multi-Core IT managers are continually faced with providing more Intel multi-core platforms will enhance computing experience services to more users, meeting higher performance by: expectations, storing and managing ever-growing amounts l Improving performance of today’s existing multi-threaded of data, maintaining availability and stability, and improving applications security. To meet many of these challenges, they’ve turned l Boosting overall system performance while remaining to Intel® Itanium® 2 processors and Intel® Xeon® processors. within acceptable power and thermal envelopes And now a transformative technology such as the Intel® multi-core processor-based platform has come along to l Increasing responsiveness of applications in multi-tasking dramatically push performance to a new level, solve pressing environments challenges, and provide new avenues for innovation. Today’s l Enabling new applications and humanlike intelligence in multi-core server processors are a critical industry inflection desktop, laptop, and other small form factors that may point. -

Intel® Core™2 Duo Mobile Processor for Intel® Centrino® Duo Mobile Processor Technology

Intel® Core™2 Duo Mobile Processor for Intel® Centrino® Duo Mobile Processor Technology Datasheet September 2007 Document Number: 314078-004 INFORMATIONLegal Lines and Disclaimers IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. -

TEST REPORT FEBRUARY 2006 System Performance in Common

TEST REPORT NOVEMBER 2006 System performance in common business scenarios that utilize new user interface features in Microsoft Windows Vista Executive summary KEY FINDINGS Intel Corporation (Intel) commissioned Principled Technologies (PT) to compare the performance in common z The Intel® vProTM technology based PC with business scenarios that utilize advanced user interface the Intel® CoreTM 2 Duo processor E6700 features in Microsoft Windows Vista of an Intel vPro yielded significant performance advantages technology based PC with that of three other platforms. We for usersTEST on our sampleREPORT tests that take tested three scenarios that took advantage of various new advantage of some of the new user-interface features of Windows Vista. We made a combination of hard featuresFEBRUARY in Windows Vista. 2006 performance measurements and subjective quality z For example, the Intel vPro technology assessments on the following systems: based PC finished our tasks on average 2.72 times faster than the Intel® Pentium® 4 • Intel Core 2 Duo processor E6700 on an Intel vPro processor 2.8GHz based PC. 965 (DQ965GF) motherboard z These performance improvements translate ® ® • Intel Pentium D processor 930 on an Intel into multi-second time savings that would be D945GTP motherboard noticeable to users. • Intel Pentium 4 processor 630 on an Intel D945GTP z The older system with the Intel Pentium 4 motherboard processor 2.8GHz on the Intel D865GBF • Intel Pentium 4 processor 2.8 GHz on an Intel motherboard did not have the capabilities D865GBF motherboard necessary to support all of the new Windows Vista features the tests utilized. As Figure 1 shows, the Intel vPro technology based PC with the Intel Core 2 Duo processor E6700 significantly outperformed the other PCs in the two scenarios in which we made hard performance measurements. -

Boulder Lake

Overview of Intel® Core 2 Architecture and Software Development Tools Overview of Architecture & Tools We will discuss: What lecture materials are available What labs are available What target courses could be impacted Some high level discussion of underlying technology Objectives After completing this module, you will: Be aware of and have access to several hours worth of MC topics including Architecture, Compiler Technology, Profiling Technology, OpenMP, & Cache Effects Be able create exercises on how to avoid coding common threading hazards associated with some MC systems – such as Poor Cache Utilization, False Sharing and Threading load imbalance Be able create exercises on how to use selected compiler directives & switches to improve behavior on each core Be able create exercises on how to take advantage VTune analyzer to quickly identify load imbalance issues, poor cache reuse and false sharing issues Agenda Multi-core Motivation Tools Overview Taking advantage of Multi-core Taking advantage of parallelism within each core (SSEx) Avoiding Memory/Cache effects Why is the Industry moving to Multi-core? In order to increase performance and reduce power consumption Its is much more efficient to run several cores at a lower frequency than one single core at a much faster frequency Power and Frequency Power vs. Frequency Curve for Single Core Architecture 359 309 259 Dropping Frequency 209 = Large Drop Power 159 Lower Frequency Power (w) Allows Headroom 109 for 2nd Core 59 9 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 2.2 2.4 2.6 -

Intel® Architecture Instruction Set Extensions and Future Features

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference May 2021 319433-044 Intel technologies may require enabled hardware, software or service activation. No product or component can be absolutely secure. Your costs and results may vary. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. All product plans and roadmaps are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not “commercial” names and not intended to function as trademarks. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be ob- tained by calling 1-800-548-4725, or by visiting http://www.intel.com/design/literature.htm. Copyright © 2021, Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. -

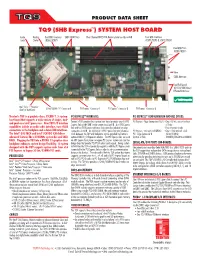

TQ9 (SHB Express™)SYSTEMHOSTBOARD

PRODUCT DATA SHEET TQ9 (SHB Express™)SYSTEMHOSTBOARD Audio Analog Dual USB Interfaces SATA II 300 Ports Dual Channel DDR2-800 Memory Interface Up to 8GB Four USB Interfaces Codec Sound (USB6/USB7) (USB4/USB5 & USB2/USB3) Dual USB Ports (USBO/USB1) Video SXGA Interface Dual Full-Speed 10/100/1000Base-T Ethernet Interfaces ® ™ Intel Core 2 Processor ™ ™ ™ (Dual- or Quad-Core) 32-bit/33MHz PCI Connector D PCI Express Connector C PCI Express Connector B PCI Express Connector A Trenton’s TQ9 is a graphics-class, PICMG® 1.3 system PCI EXPRESSTM INTERFACES: PCI EXPRESSTM CONFIGURATION AND BUS SPEEDS: host board that supports a wide variety of single-, dual- ® Trenton's TQ9 graphics-class system host board provides one x16 PCI PCI Express - Edge Connectors A & B - One x16 link, one x4 or four and quad-core Intel processors. New TQ9 I/O interface Express link on the SHB's edge connectors A and B. A x4 PCI Express x1 links capabilities include an audio codec interface, two eSATA link and five PCI Express reference clocks are also included on edge - Five reference clocks connections to the backplane and a dozen USB interfaces. connectors A and B. An additional x1 PCI Express link and reference PCI Express - (via optional IOB31) - One x1 link and ref. clock The Intel® Q35 MCH and Intel® ICH9DO ICH deliver clock between the TQ9 and backplane can be provided by Trenton's PCI - Edge Connector D - 32-bit/33MHz advanced features like a 1333MHz system bus and SATA optional IOB31 I/O Expansion Module. The PCI Express links are used System or FSB - 1333MHz,1066MHz or 800MHz RAID. -

Introducing the 45Nm Next-Generation Intel® Core™ Microarchitecture White Paper Introducing the 45Nm Next-Generation Intel® Core™ Microarchitecture

White Paper Intel® Core™ Microarchitecture Introducing the 45nm Next-Generation Intel® Core™ Microarchitecture White Paper Introducing the 45nm Next-Generation Intel® Core™ Microarchitecture Contents New Innovations and Enhancements Deliver Higher Performance and Energy Efficiency. ..........................................................3 Intel® Core™ Microarchitecture ........................................................................................................................................................................3 Intel’s 45nm High-k Metal Gate Process Technology ...............................................................................................................................4 Penryn, the Next-Generation Intel® Core™2 Processor Family ..............................................................................................................4 Making Software Run Faster .......................................................................................................................................................................4 New Intel® SSE4 Instructions ......................................................................................................................................................................................................................................................................................4 Larger, Enhanced Intel® Advanced Smart Cache .....................................................................................................................................................................................................................................5 -

Intel's Core 2 Family

Intel’s Core 2 family - TOCK lines References Dezső Sima Vers. 1.0 Januar 2019 Contents (1) • 1. Introduction • 2. The Core 2 line • 3. The Nehalem line • 4. The Sandy Bridge line • 5. The Haswell line • 6. The Skylake line • 7. The Kaby Lake line • 8. The Kaby Lake Refresh line • 9. The Coffee Lake line • 10. The Coffee Lake line Refresh Contents (2) • 11. The Cannon Lake line (outlook) • 12. Sunny Cove • 13. References 13. References 12. References (1) [1]: Singhal R., “Next Generation Intel Microarchitecture (Nehalem) Family: Architecture Insight and Power Management, IDF Taipeh, Oct. 2008, http://intel.wingateweb.com/taiwan08/ published/sessions/TPTS001/FA08%20IDFTaipei_TPTS001_100.pdf [2]: Bryant D., “Intel Hitting on All Cylinders,” UBS Conf., Nov. 2007, http://files.shareholder.com/downloads/INTC/0x0x191011/e2b3bcc5-0a37-4d06- aa5a-0c46e8a1a76d/UBSConfNov2007Bryant.pdf [3]: Fisher S., “Technical Overview of the 45 nm Next Generation Intel Core Microarchitecture (Penryn),” IDF 2007, ITPS001, http://isdlibrary.intel-dispatch.com/isd/89/45nm.pdf [4]:Pabst T., The New Athlon Processor: AMD Is Finally Overtaking Intel, Tom's Hardware, August 9, 1999, http://www.tomshardware.com/reviews/athlon-processor,121-2.html [5]: Carmean D., “Inside the Pentium 4 Processor Micro-architecture,” Aug. 2000, http://people.virginia.edu/~zl4j/CS854/pda_s01_cd.pdf [6]: Shimpi A. L. & Clark J., “AMD Opteron 248 vs. Intel Xeon 2.8: 2-way Web Servers go Head to Head,” AnandTech, Dec. 17 2003, http://www.anandtech.com/showdoc.aspx?i=1935&p=1 [7]: Völkel F., “Duel of the Titans: Opteron vs. Xeon : Hammer Time: AMD On The Attack,” Tom’s Hardware, Apr.