MSCSICMDD/REF1 Application Note 1824 Dual Sic MOSFET Driver Reference Design 10/2016

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AN826 Crystal Oscillator Basics and Crystal Selection for Rfpic™ And

AN826 Crystal Oscillator Basics and Crystal Selection for rfPICTM and PICmicro® Devices • What temperature stability is needed? Author: Steven Bible Microchip Technology Inc. • What temperature range will be required? • Which enclosure (holder) do you desire? INTRODUCTION • What load capacitance (CL) do you require? • What shunt capacitance (C ) do you require? Oscillators are an important component of radio fre- 0 quency (RF) and digital devices. Today, product design • Is pullability required? engineers often do not find themselves designing oscil- • What motional capacitance (C1) do you require? lators because the oscillator circuitry is provided on the • What Equivalent Series Resistance (ESR) is device. However, the circuitry is not complete. Selec- required? tion of the crystal and external capacitors have been • What drive level is required? left to the product design engineer. If the incorrect crys- To the uninitiated, these are overwhelming questions. tal and external capacitors are selected, it can lead to a What effect do these specifications have on the opera- product that does not operate properly, fails prema- tion of the oscillator? What do they mean? It becomes turely, or will not operate over the intended temperature apparent to the product design engineer that the only range. For product success it is important that the way to answer these questions is to understand how an designer understand how an oscillator operates in oscillator works. order to select the correct crystal. This Application Note will not make you into an oscilla- Selection of a crystal appears deceivingly simple. Take tor designer. It will only explain the operation of an for example the case of a microcontroller. -

EURO QUARTZ TECHNICAL NOTES Crystal Theory Page 1 of 8

EURO QUARTZ TECHNICAL NOTES Crystal Theory Page 1 of 8 Introduction The Crystal Equivalent Circuit If you are an engineer mainly working with digital devices these notes In the crystal equivalent circuit above, L1, C1 and R1 are the crystal should reacquaint you with a little analogue theory. The treatment is motional parameters and C0 is the capacitance between the crystal non-mathematical, concentrating on practical aspects of circuit design. electrodes, together with capacitances due to its mounting and lead- out arrangement. The current flowing into a load at B as a result of a Various oscillator designs are illustrated that with a little constant-voltage source of variable frequency applied at A is plotted experimentation may be easily modified to suit your requirements. If below. you prefer a more ‘in-depth’ treatment of the subject, the appendix contains formulae and a list of further reading. At low frequencies, the impedance of the motional arm of the crystal is extremely high and current rises with increasing frequency due solely to Series or Parallel? the decreasing reactance of C0. A frequency fr is reached where L1 is resonant with C1, and at which the current rises dramatically, being It can often be confusing as to whether a particular circuit arrangement limited only by RL and crystal motional resistance R1 in series. At only requires a parallel or series resonant crystal. To help clarify this point, it slightly higher frequencies the motional arm exhibits an increasing net is useful to consider both the crystal equivalent circuit and the method inductive reactance, which resonates with C0 at fa, causing the current by which crystal manufacturers calibrate crystal products. -

Reliability Information Analysis Center (RIAC) Electronic Parts Reliability Data (EPRD) Part Category Descriptors

Reliability Information Analysis Center (RIAC) Electronic Parts Reliability Data (EPRD) Part Category Descriptors The following pages contain the descriptors of all part categories covered by the 4-Volume RIAC Publication “Electronic Parts Reliability Data”, Catalog No. EPRD-2014. -

Behemoth: Restoration of an RCA Victor Model 15K-1 – Gerry O'hara

A Mid-1930’s ‘Magic’ Behemoth: Restoration of an RCA Victor Model 15K-1 – Gerry O’Hara Background I recently completed the refurbishment of a Marconi CSR-5 receiver for a friend. Shortly before work on that receiver was completed, he asked if I would be able to restore an RCA Victor 15K-1 receiver as my next project. Quite a different ‘beast’ from the CSR-5, a WWII Canadian communications receiver built for the Canadian Navy, whereas the RCA Victor 15K-1 is a high-end domestic console style set dating from the 1936/37 model year. The cabinet was in poor condition (photo, right), and in need of stripping/re-finishing, but the chassis appeared complete and in reasonable shape from the photos I was sent in advance. To save bringing the large, heavy cabinet over to Victoria from the BC Mainland, and as I don’t have the facility to refinish large cabinets at my house at the moment, it was agreed that I would restore the chassis and the cabinet would be restored by a mutual friend at the SPARC Museum. The RCA ‘K’ series Radios and the ‘Magic Brain’ RCA Victor introduced receivers with a separate RF sub- chassis, marketed as the ‘Magic Brain’, in the mid-1930’s, initially with their models 128, 224, C11-1 and others: “Inside RCA Victor all-wave sets is an uncanny governing unit ... Human in its thinking, we compare it to the human brain. You choose the broadcast - from no matter where in the whole world. Then, watchman-like, it keeps out undesired radio signals. -

Electronic Circuits for the Hobbyist

Circuits for the Hobbyist For your electronics hobby entertainment; ENJOY! It is assumed that you have AT LEAST the equivalent of a Basic Electronics certificate for the electronics projects listed on this page. Other projects require more advanced electronics. A lot of these circuits assume the latter so I will no longer answer the tons of emails in regards to that. If you wish to learn more about electronics there is enough of that available on the internet. Circuits' Message Board Ask your questions here. Someone may answer them. ScanMate Your (Radio) scanner Alternating On-Off Control buddy! 6-20-2002 Audio Pre-Amplifier #1 Simplest R/C Circuit Automatic 9-Volt Nicad Battery Charger Simplest RF Transmitter Basic IC MonoStable Multivibrator Simple Transistor Audio PreAmplifier Basic RF Oscillator #1 Single IC Audio Preamplifier Basic LM3909 Led Flasher Solar Cell NiCad Charger 7-24- Battery Monitor for 12V Lead-Acid 2002 Battery Tester for 1.5 & 9V Solid State Relay Bench Top Powersupply, 0-30V/0-10A, Part 1 Third Brake Light Pulser Bench Top Powersupply, 0-30V/0-10A, Part 2 Toroids, RF/EMI Cores Bench Top Powersupply, 0-30V/0-10A, Part 3 Touch Activated Alarm System Birdie Doorbell Ringer Two-Tone Trainhorn 'Bug' Detector with Beep Universal Flasher Circuit Car Converter for 12V to 9V Variable Power Supply, 1 - 30V @ 1.5A Car NiCad Charger Wailing Alarm DC Motor Reversing Circuit Water-level Sensing and Control DC Motor Control Circuit Waterpump Safety Guard for Fish-pond Gel Cell Charger, I - Off-line Weller WLC100 Electronic Soldering -

MSK 011 Transistor Mixer

MSK 011 Transistor Mixer North Coast Synthesis Ltd. Matthew Skala August 31, 2021 Documentation for the MSK 011 Copyright © 2018, 2020, 2021 Matthew Skala This documentation is free: you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation, version 3. This documentation is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PUR- POSE. See the GNU General Public License for more details. You should have received a copy of the GNU General Public License along with this documentation. If not, see http://www.gnu.org/licenses/. 2 Contents General notes 4 Specifications ................................................ 4 Controls and connections ......................................... 4 Source package ............................................... 5 PCBs and physical design ......................................... 5 Component substitutions ......................................... 5 PNP transistor modification ........................................ 5 Modification for ±15V power ....................................... 6 Use and contact information ........................................ 6 Safety and other warnings 7 Bill of materials 8 Building the module 9 Preliminaries ................................................ 9 Some notes on knobs ............................................ 9 Panel components ............................................. 10 Fixed resistors -

United States Patent (113,573,581 72 Inventors John J

United States Patent (113,573,581 72 Inventors John J. Dutko 3,268,047 8/1966 Grygera, et al............... 1121219 North Plainfield; 3,374,410 3/1968 Cronquist, et al............ 3181138 Richard Beck, Morris Plains; Henry A. 3,435,314 5/1969 Bradley........................ 318/138 Seesselberg, South Plainfield, N.J. 3,443,181 6/1969 Tozol, et al................... 318/138 (21) Appl. No. 836,103 3,466,517 9/1969. Leenhouts.................... 318/138 22 Filed June 24, 1969 45 Patented Apr. 6, 1971 Primary Examiner-Oris L. Rader (73) Assignee The Singer Company Assistant Examiner-K. L. Crosson New York, N.Y. Attorneys-Marshall J. Breen and Chester A. William, Jr. 54 SYSTEM FOR CONTROLLING NEEDLE POSITONING DRIVE AND THREADTRMMING FUNCTIONS OF AN INDUSTRIAL SEWNG ABSTRACT: Solid-state digital logic circuitry with gates, MACHINEDRIVEN BY A CONTNUOUSLY memory flip-flops, delay and sensor elements provide a logic COUPLEDDCMOTOR system for controlling the drive and braking currents to a DC 10 Claims, 9 Drawing Figs. motor continuously coupled in driving relation to a sewing machine. In response to certain input commands, a series of (52) U.S.Ch....................................................... 318/266, events are signaled by the logic circuitry to occur automati 12/219,3181466 cally in a predetermined time sequence resulting in a desired 51 int. Cl............................... ......................... H02p3/06 output sewing related function. Silicon controlled rectifiers 50 Field of Search............................................ 112/219; (SCR's) are used to supply driving current to the motor from a 318/265,266, 466 polyphase voltage supply. A single SCR is used to supply Ref Cited dynamic braking current for the motor. -

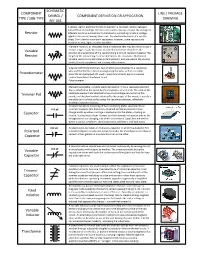

Download Schematic-Symbols-Page-1.Pdf

SCHEMATIC COMPONENT LINE / PACKAGE SYMBOL / COMPONENT DEFINITION OR APPLICATION TYPE / SUB-TYPE DRAWING REF DES A device used in electrical circuits to maintain a constant relation between current flow and voltage. Resistors are used to step up or lower the voltage at Resistor different points in a circuit and to transform a current signal into a voltage signal or vice versa, among other uses. The electrical behavior of a resistor obeys Ohm's law for a constant resistance; however, some resistors are sensitive to heat, light, or other variables. Variable resistors, or rheostats, have a resistance that may be varied across a Variable certain range, usually by means of a mechanical device that alters the position of one terminal of the resistor along a strip of resistant material. The Resistor length of the intervening material determines the resistance. Mechanical variable resistors are also called potentiometers, and are used in the volume knobs of audio equipment and in many other devices. a device with three terminals, two of which are connected to a resistance wire and the third to a brush moving along the wire, so that a variable Potentiometer potential can be tapped off: used in electronic circuits, esp as a volume control Sometimes shortened to pot Potentiometer. Manually adjustable, variable, electrical resistor. It has a resistance element that is attached to the circuit by three contacts, or terminals. The ends of the resistance element are attached to two input voltage conductors of the Trimmer Pot circuit, and the third contact, attached to the output of the circuit, is usually a movable terminal that slides across the resistance element, effectively dividing it into two resistors. -

A Compact 70

© 1967 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. 260 IEEE TRANSACTIONS ON NUCLEAR SCIENCE, JUNE 1967 A COMPACT70MW, 250KV MODULATOR USING THYRATRONS C. Latham H. Menown N.S. Nicholls Vickers Ltd. English Electric Royal Radar Radiation and Nuclear Valve Co. Ltd. Establishment Engineering Division SUMMARY Pulse Repetition Rate Up to 1000 p.p.s. max. (at 0.5nsec flat-top) Pulse A compact oil immersed modulator is described Flatness *0.5% over specified suitable for driving a 30MWoutput klystron and flat-top. Pulse-Pulse using two 70KV 2,500 Amp hydrogen thyratrons as Time Jitter *5ns max. switches. The design is a development of an H.T. Stabilisation Better than f0.28 for earlier modulator using a 70KV triggered spark *3% mains variation. gapa This earlier model was limited to a maximum Response time less than repetition rate of about 250 p.p.s. but the 2 supply cycles. thyratron switches permit operation to over 1000 The modulator p.p.s. and a maximum duty cycle of .OOl. (Fig.11 is contained in a steel tank approximately Complete oil immersion in a single tank results 15ft. long by 3ft.3in. wide by 4ft.8in. high and in compactness, economy, reliability and facil- at one end supports and accomm- odates the klystron, the cathode itates the use of a high charging voltage which, bushing of which in turn, is lowered into the tank. -

Crystal Oscillator Troubleshooting Guide

Freescale Semiconductor AN3208 Application Note Rev. 0, 1/2006 Crystal Oscillator Troubleshooting Guide by: Sergio Garcia de Alba Garcin RTAC Americas 1 Overview Table of Contents 1 Overview . 1 This document is a quick-reference troubleshooting 2 Introduction . 1 guide for solving crystal oscillator problems that might 3 Oscillator Configurations. 2 4 Components in the Colpitts Configuration . 3 be encountered when working with microcontrollers. 5 Components in the Pierce Configuration . 3 A practical explanation of the Pierce and Colpitts 6 Crystal Overdriving . 4 7 Insufficient Loop Gain . 5 oscillators used in Freescale microcontrollers and 8 Long Start-Up Time. 5 recommendations to help solve common problems with 9 Temperature and Voltage Issues . 5 microcontroller crystal oscillators are presented in the 10 Noise Immunity . 6 11 Layout Issues . 6 following sections. Nevertheless, a particular problem 12 Other Problems. 7 might require a different solution from those proposed in 13 Conclusion . 7 this application note. Most of the points discussed will 14 References . 8 help in the design stage to come about with a more reliable oscillator. 2 Introduction Most microcontrollers can use a crystal oscillator as their clock source. Other options include external canned oscillators, resonators, RC oscillators, and internal clocks. The main advantages of a crystal oscillator are frequency accuracy, stability, and low power consumption. However, high reliability is needed to fully benefit from these advantages. © Freescale Semiconductor, Inc., 2006. All rights reserved. Oscillator Configurations To solve common problems with crystal oscillators and to achieve high reliability, it is important to pay attention to the configuration used, the components and their values, and the layout. -

HF/VHF/UHF RF Power N-Channel MOSFET

SD2942 HF/VHF/UHF RF power N-channel MOSFET Datasheet - production data Features Gold metallization Excellent thermal stability Common source push-pull configuration POUT = 350 W min. with 15 dB gain @ 175 MHz Low RDS(on) Description Figure 1: Pin connection The SD2942 is a gold metallized N-channel MOS field-effect RF power transistor. The SD2942 offers 25% lower RDS(ON) than industry standard and 20% higher power saturation than ST SD2932. These characteristics make the SD2942 ideal for 50 V DC very high power applications up to 250 MHz. Table 1: Device summary Order code Marking Package Packing SD2942W SD2942(1) M244 Tube Notes: (1)For more details please refer to Section 6: "Marking, packing and shipping specifications". November 2016 DocID11736 Rev 5 1/17 This is information on a product in full production. www.st.com Contents SD2942 Contents 1 Electrical data .................................................................................. 3 1.1 Maximum ratings ............................................................................... 3 1.2 Thermal data ..................................................................................... 3 2 Electrical characteristics ................................................................ 4 3 Impedance data ............................................................................... 5 4 Typical performance ....................................................................... 6 5 Test circuit (175 MHz) ................................................................... -

Trimmer Potentiometers

!Note Please read rating and !CAUTION (for storage, operating, rating, soldering, mounting and handling) in this PDF catalog to prevent smoking and/or burning, etc. R50E13.pdf 04.6.11 This catalog has only typical specifications. Therefore, you are requested to approve our product specifications or to transact the approval sheet for product specifications before ordering. Trimmer Potentiometers Murata Manufacturing Co., Ltd. Cat.No.R50E-13 !Note •Please Please read read rating rating and and ! !CAUTIONCAUTION (for (for storage, storage, operating, operating, rating, rating, soldering, soldering, mounting mounting and and handling) handling) in in this this PDF catalog catalog to prevent to prevent smoking smoking and/or and/or burning, burnin etc.g, etc. R50E13.pdf 04.6.11 •This This catalog catalog has has only only typical typical specifications. specifications Therefore, because there you are is no requested space for to detailed approve specifications. our product specifications Therefore, please or to transact approve the our approval product sheet specifications for product or specificationstransact the approval before ordering. sheet for product specifications before ordering. CONTENTS 1 Part Numbering 2 Selection Guide of Trimmer Potentiometers 4 2 1 SMD Open Type 2mm Size PVZ2 Series 5 PVZ2 Series Notice 7 2 SMD Open Type 3mm Size PVZ3/PVS3/PVA3 Series 9 3 PVZ3/PVS3/PVA3 Series Notice 16 3 SMD Sealed Type 2mm Size PVF2 Series 19 PVF2 Series Notice 21 4 4 SMD Sealed Type 3mm Size PVG3 Series 23 PVG3 Series Notice 26 5 SMD Sealed