Final Report Title

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lab 4: Using the Digital-To-Analog Converter

ECE2049 – Embedded Computing in Engineering Design Lab 4: Using the Digital-to-Analog Converter In this lab, you will gain experience with SPI by using the MSP430 and the MSP4921 DAC to create a simple function generator. Specifically, your function generator will be capable of generating different DC values as well as a square wave, a sawtooth wave, and a triangle wave. Pre-lab Assignment There is no pre-lab for this lab, yay! Instead, you will use some of the topics covered in recent lectures and HW 5. Lab Requirements To implement this lab, you are required to complete each of the following tasks. You do not need to complete the tasks in the order listed. Be sure to answer all questions fully where indicated. As always, if you have conceptual questions about the requirements or about specific C please feel free to as us—we are happy to help! Note: There is no report for this lab! Instead, take notes on the answers to the questions and save screenshots where indicated—have these ready when you ask for a signoff. When you are done, you will submit your code as well as your answers and screenshots online as usual. System Requirements 1. Start this lab by downloading the template on the course website and importing it into CCS—this lab has a slightly different template than previous labs to include the functionality for the DAC. Look over the example code to see how to use the DAC functions. 2. Your function generator will support at least four types of waveforms: DC (a constant voltage), a square wave, sawtooth wave, and a triangle wave, as described in the requirements below. -

Tracking of High-Speed, Non-Smooth and Microscale-Amplitude Wave Trajectories

Tracking of High-speed, Non-smooth and Microscale-amplitude Wave Trajectories Jiradech Kongthon Department of Mechatronics Engineering, Assumption University, Suvarnabhumi Campus, Samuthprakarn, Thailand Keywords: High-speed Tracking, Inversion-based Control, Microscale Positioning, Reduced-order Inverse, Tracking. Abstract: In this article, an inversion-based control approach is proposed and presented for tracking desired trajectories with high-speed (100Hz), non-smooth (triangle and sawtooth waves), and microscale-amplitude (10 micron) wave forms. The interesting challenge is that the tracking involves the trajectories that possess a high frequency, a microscale amplitude, sharp turnarounds at the corners. Two different types of wave trajectories, which are triangle and sawtooth waves, are investigated. The model, or the transfer function of a piezoactuator is obtained experimentally from the frequency response by using a dynamic signal analyzer. Under the inversion-based control scheme and the model obtained, the tracking is simulated in MATLAB. The main contributions of this work are to show that (1) the model and the controller achieve a good tracking performance measured by the root mean square error (RMSE) and the maximum error (Emax), (2) the maximum error occurs at the sharp corner of the trajectories, (3) tracking the sawtooth wave yields larger RMSE and Emax values,compared to tracking the triangle wave, and (4) in terms of robustness to modeling error or unmodeled dynamics, Emax is still less than 10% of the peak to peak amplitude of 20 micron if the increases in the natural frequency and the damping ratio are less than 5% for the triangle trajectory and Emax is still less than 10% of the peak to peak amplitude of 20 micron if the increases in the natural frequency and the damping ratio are less than 3.2 % for the sawtooth trajectory. -

Verified Design Analog Pulse Width Modulation

John Caldwell TI Precision Designs: Verified Design Analog Pulse Width Modulation TI Precision Designs Circuit Description TI Precision Designs are analog solutions created by This circuit utilizes a triangle wave generator and TI’s analog experts. Verified Designs offer the theory, comparator to generate a pulse-width-modulated component selection, simulation, complete PCB (PWM) waveform with a duty cycle that is inversely schematic & layout, bill of materials, and measured proportional to the input voltage. An op amp and performance of useful circuits. Circuit modifications comparator generate a triangular waveform which is that help to meet alternate design goals are also passed to the inverting input of a second comparator. discussed. By passing the input voltage to the non-inverting comparator input, a PWM waveform is produced. Negative feedback of the PWM waveform to an error amplifier is utilized to ensure high accuracy and linearity of the output Design Resources Ask The Analog Experts Design Archive All Design files WEBENCH® Design Center TINA-TI™ SPICE Simulator TI Precision Designs Library OPA2365 Product Folder TLV3502 Product Folder REF3325 Product Folder R4 C1 VCC R3 - VPWM + VIN VREF R1 + ++ + U1A - U2A V R2 C2 CC VTRI C3 R7 - ++ U1B VREF VCC VREF - ++ U2B VCC R6 R5 An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information. TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments SLAU508-June 2013-Revised June 2013 Analog Pulse Width Modulation 1 Copyright © 2013, Texas Instruments Incorporated www.ti.com 1 Design Summary The design requirements are as follows: Supply voltage: 5 Vdc Input voltage: -2 V to +2 V, dc coupled Output: 5 V, 500 kHz PWM Ideal transfer function: V The design goals and performance are summarized in Table 1. -

Fourier Series

Chapter 10 Fourier Series 10.1 Periodic Functions and Orthogonality Relations The differential equation ′′ y + 2y = F cos !t models a mass-spring system with natural frequency with a pure cosine forcing function of frequency !. If 2 = !2 a particular solution is easily found by undetermined coefficients (or by∕ using Laplace transforms) to be F y = cos !t. p 2 !2 − If the forcing function is a linear combination of simple cosine functions, so that the differential equation is N ′′ 2 y + y = Fn cos !nt n=1 X 2 2 where = !n for any n, then, by linearity, a particular solution is obtained as a sum ∕ N F y (t)= n cos ! t. p 2 !2 n n=1 n X − This simple procedure can be extended to any function that can be repre- sented as a sum of cosine (and sine) functions, even if that summation is not a finite sum. It turns out that the functions that can be represented as sums in this form are very general, and include most of the periodic functions that are usually encountered in applications. 723 724 10 Fourier Series Periodic Functions A function f is said to be periodic with period p> 0 if f(t + p)= f(t) for all t in the domain of f. This means that the graph of f repeats in successive intervals of length p, as can be seen in the graph in Figure 10.1. y p 2p 3p 4p 5p Fig. 10.1 An example of a periodic function with period p. -

The Oscilloscope and the Function Generator: Some Introductory Exercises for Students in the Advanced Labs

The Oscilloscope and the Function Generator: Some introductory exercises for students in the advanced labs Introduction So many of the experiments in the advanced labs make use of oscilloscopes and function generators that it is useful to learn their general operation. Function generators are signal sources which provide a specifiable voltage applied over a specifiable time, such as a \sine wave" or \triangle wave" signal. These signals are used to control other apparatus to, for example, vary a magnetic field (superconductivity and NMR experiments) send a radioactive source back and forth (M¨ossbauer effect experiment), or act as a timing signal, i.e., \clock" (phase-sensitive detection experiment). Oscilloscopes are a type of signal analyzer|they show the experimenter a picture of the signal, usually in the form of a voltage versus time graph. The user can then study this picture to learn the amplitude, frequency, and overall shape of the signal which may depend on the physics being explored in the experiment. Both function generators and oscilloscopes are highly sophisticated and technologically mature devices. The oldest forms of them date back to the beginnings of electronic engineering, and their modern descendants are often digitally based, multifunction devices costing thousands of dollars. This collection of exercises is intended to get you started on some of the basics of operating 'scopes and generators, but it takes a good deal of experience to learn how to operate them well and take full advantage of their capabilities. Function generator basics Function generators, whether the old analog type or the newer digital type, have a few common features: A way to select a waveform type: sine, square, and triangle are most common, but some will • give ramps, pulses, \noise", or allow you to program a particular arbitrary shape. -

The Differential Pair As a Triangle-Sine Wave Converter V - ROBERT G

418 IEEE JOURNAL OF SOLID-STATE CIRCUITS, JUNE 1976 Correspondence The Differential Pair as a Triangle-Sine Wave Converter v - ROBERT G. MEYER, WILLY M. C. SANSEN, SIK LUI, AND STEFAN PEETERS R~ R~ 1 / Abstract–The performance of a differential pair with emitter degen- eration as a triangle-sine wave converter is analyzed. Equations describ- ing the circuit operation are derived and solved both analytically and by computer. This allows selection of operating conditions for optimum performance such that total harmonic distortion as low as 0.2 percent “- has been measured. -vEE (a) I. INTRODUCTION The conversion of ttiangle waves to sine waves is a function I ---- I- often required in waveshaping circuits. For example, the oscil- lators used in function generators usually generate triangular output waveforms [ 1] because of the ease with which such oscillators can operate over a wide frequency range including very low frequencies. This situation is also common in mono- r v, Zr t lithic oscillators [2] . Sinusoidal outputs are commonly de- sired in such oscillators and can be achieved by use of a non- linear circuit which produces an output sine wave from an input triangle wave. — — — — The above circuit function has been realized in the past by -I -I ----- means of a piecewise linear approximation using diode shaping J ‘“b ‘M VI networks [ 1] . However, a simpler approach and one well M suited to monolithic realization has been suggested by Grebene [3] . This is shown in Fig. 1 and consists simply of a differen- 77 tial pair with an appropriate value of emitter resistance R. -

Tektronix Signal Generator

Signal Generator Fundamentals Signal Generator Fundamentals Table of Contents The Complete Measurement System · · · · · · · · · · · · · · · 5 Complex Waves · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 15 The Signal Generator · · · · · · · · · · · · · · · · · · · · · · · · · · · · 6 Signal Modulation · · · · · · · · · · · · · · · · · · · · · · · · · · · 15 Analog or Digital? · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 7 Analog Modulation · · · · · · · · · · · · · · · · · · · · · · · · · 15 Basic Signal Generator Applications· · · · · · · · · · · · · · · · 8 Digital Modulation · · · · · · · · · · · · · · · · · · · · · · · · · · 15 Verification · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 8 Frequency Sweep · · · · · · · · · · · · · · · · · · · · · · · · · · · 16 Testing Digital Modulator Transmitters and Receivers · · 8 Quadrature Modulation · · · · · · · · · · · · · · · · · · · · · 16 Characterization · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 8 Digital Patterns and Formats · · · · · · · · · · · · · · · · · · · 16 Testing D/A and A/D Converters · · · · · · · · · · · · · · · · · 8 Bit Streams · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 17 Stress/Margin Testing · · · · · · · · · · · · · · · · · · · · · · · · · · · 9 Types of Signal Generators · · · · · · · · · · · · · · · · · · · · · · 17 Stressing Communication Receivers · · · · · · · · · · · · · · 9 Analog and Mixed Signal Generators · · · · · · · · · · · · · · 18 Signal Generation Techniques -

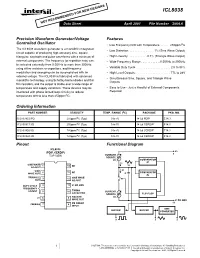

ICL8038 TM D FO NDE MME ECO OT R N Data Sheet April 2001 File Number 2864.4

NS ESIG W D R NE ICL8038 TM D FO NDE MME ECO OT R N Data Sheet April 2001 File Number 2864.4 Precision Waveform Generator/Voltage Features Controlled Oscillator • Low Frequency Drift with Temperature...... 250ppm/oC The ICL8038 waveform generator is a monolithic integrated • LowDistortion...............1%(SineWaveOutput) tle circuit capable of producing high accuracy sine, square, 80 triangular, sawtooth and pulse waveforms with a minimum of • HighLinearity ...........0.1%(Triangle Wave Output) external components. The frequency (or repetition rate) can • Wide Frequency Range ............0.001Hzto300kHz - be selected externally from 0.001Hz to more than 300kHz using either resistors or capacitors, and frequency • VariableDutyCycle.....................2%to98% modulation and sweeping can be accomplished with an • HighLevelOutputs......................TTLto28V ci- external voltage. The ICL8038 is fabricated with advanced • Simultaneous Sine, Square, and Triangle Wave monolithic technology, using Schottky barrier diodes and thin Outputs e- film resistors, and the output is stable over a wide range of temperature and supply variations. These devices may be • Easy to Use - Just a Handful of External Components er- interfaced with phase locked loop circuitry to reduce Required o /Vo temperature drift to less than 250ppm/ C. e - Ordering Information ed PART NUMBER STABILITY TEMP. RANGE (oC) PACKAGE PKG. NO. il- o r) ICL8038CCPD 250ppm/ C(Typ) 0to70 14LdPDIP E14.3 tho ICL8038CCJD 250ppm/oC(Typ) 0to70 14LdCERDIP F14.3 ICL8038BCJD 180ppm/oC(Typ) -

Oscilators Simplified

SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN TAB BOOKS Inc. Blue Ridge Summit. PA 172 14 FIRST EDITION FIRST PRINTING Copyright O 1987 by TAB BOOKS Inc. Printed in the United States of America Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein. Library of Cangress Cataloging in Publication Data Horn, Delton T. Oscillators simplified, wtth 61 projects. Includes index. 1. Oscillators, Electric. 2, Electronic circuits. I. Title. TK7872.07H67 1987 621.381 5'33 87-13882 ISBN 0-8306-03751 ISBN 0-830628754 (pbk.) Questions regarding the content of this book should be addressed to: Reader Inquiry Branch Editorial Department TAB BOOKS Inc. P.O. Box 40 Blue Ridge Summit, PA 17214 Contents Introduction vii List of Projects viii 1 Oscillators and Signal Generators 1 What Is an Oscillator? - Waveforms - Signal Generators - Relaxatton Oscillators-Feedback Oscillators-Resonance- Applications--Test Equipment 2 Sine Wave Oscillators 32 LC Parallel Resonant Tanks-The Hartfey Oscillator-The Coipltts Oscillator-The Armstrong Oscillator-The TITO Oscillator-The Crystal Oscillator 3 Other Transistor-Based Signal Generators 62 Triangle Wave Generators-Rectangle Wave Generators- Sawtooth Wave Generators-Unusual Waveform Generators 4 UJTS 81 How a UJT Works-The Basic UJT Relaxation Oscillator-Typical Design Exampl&wtooth Wave Generators-Unusual Wave- form Generator 5 Op Amp Circuits -

Fourier Transforms

Fourier Transforms Mark Handley Fourier Series Any periodic function can be expressed as the sum of a series of sines and cosines (or varying amplitides) 1 Square Wave Frequencies: f Frequencies: f + 3f Frequencies: f + 3f + 5f Frequencies: f + 3f + 5f + … + 15f Sawtooth Wave Frequencies: f Frequencies: f + 2f Frequencies: f + 2f + 3f Frequencies: f + 2f + 3f + … + 8f 2 Fourier Series A function f(x) can be expressed as a series of sines and cosines: where: Fourier Transform Fourier Series can be generalized to complex numbers, and further generalized to derive the Fourier Transform. Forward Fourier Transform: Inverse Fourier Transform: Note: 3 Fourier Transform Fourier Transform maps a time series (eg audio samples) into the series of frequencies (their amplitudes and phases) that composed the time series. Inverse Fourier Transform maps the series of frequencies (their amplitudes and phases) back into the corresponding time series. The two functions are inverses of each other. Discrete Fourier Transform If we wish to find the frequency spectrum of a function that we have sampled, the continuous Fourier Transform is not so useful. We need a discrete version: Discrete Fourier Transform 4 Discrete Fourier Transform Forward DFT: The complex numbers f0 … fN are transformed into complex numbers F0 … Fn Inverse DFT: The complex numbers F0 … Fn are transformed into complex numbers f0 … fN DFT Example Interpreting a DFT can be slightly difficult, because the DFT of real data includes complex numbers. Basically: The magnitude of the complex number for a DFT component is the power at that frequency. The phase θ of the waveform can be determined from the relative values of the real and imaginary coefficents. -

Tooth Wave Supplied to One Deflection Axis of 50 Field of Search

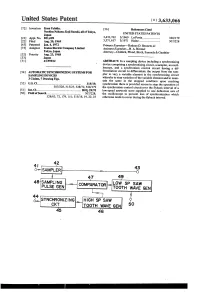

United States Patent (11) 3,633,066 72) Inventors Kozo Uchida; Naohisa Nakaya; Koji Suzuki, all of Tokyo, 56 References Cited Japan UNITED STATES PATENTS (21) Appl. No. 851,609 3,432,762 3/1969 La Porta....................... 328/179 22) Fied Aug. 20, 1969 3,571,617 3/1971 Hainz........................... 307/228 45) Patented Jan. 4, 1972 Primary Examiner-Rodney D. Bennett, Jr. 73 Assignee Iwatsu Electric Company Limited Assistant Examiner-H. A. Birmiel Tokyo, Japan Attorney-Chittick, Pfund, Birch, Samuels & Gauthier 32) Priority Aug. 23, 1968 33 Japan 31) 43/59922 ABSTRACT: In a sampling device including a synchronizing device comprising a synchronizing circuit, a sampler, an oscil loscope, and a synchronism control circuit having a dif 54) AUTOMATICSYNCHRONIZING SYSTEMSFOR ferentiation circuit to differentiate the output from the sam SAMPLNG EDEVICES pler to vary a variable element in the synchronizing circuit whereby to stop variation of the variable element and to main 3 Claims, 7 Drawing Figs. tain the same in the stopped condition upon reaching 52) U.S.C........................................................ 315/19, synchronism there is provided means to stop the operation of 307/228, 315125,328/72,328/179 the synchronism control circuit over the flyback interval of a (51) Int. Cl......................................................... H01j29/70 low-speed sawtooth wave supplied to one deflection axis of 50 Field of Search............................................ 307/228; the oscilloscope to prevent loss of synchronization which 328/63, 72, 179, 151; 315/18, 19, 22, 25 otherwise tends to occur during the flyback interval. LOW SP SAW 48SAMPLNGPULSE GEN COMPARATOR TOOTH WAVE GEN SYNCHRONIZING HGH SP SAW CKT TOOTH WAVE GEN 46 PATENTEDIAN 4972 3,633,066 SHEET 1 OF 2 - - - - - - - - - - was - - - - - - - - - - - - - -- a-- - - - F. -

Chapter 9. Fourier Series A. the Fourier Sine Series

Vector Spaces in Physics 8/6/2015 Chapter 9. Fourier Series A. The Fourier Sine Series The general solution. In Chapter 8 we found solutions to the wave equation for a string fixed at both ends, of length L, and with wave velocity v, yn x, t A n sin k n x cos n t k n n L 1 n 2L , n = 1, 2, 3, . (9-1) n v n n L v fn n 2L We are now going to proceed to describe an arbitrary motion of the string with both ends fixed in terms of a linear superposition of normal modes: nx general solution, string , (9-2) y x, t Ann sin cos t n1 L fixed at both ends nv where and the coefficients An are to be determined. Here are some things to be noted: n L (1) We are assuming for the moment that this equation is true - that is, in the limit where we include an infinite number of terms, that the infinite series is an arbitrarily good approximation to the solution y x, t . (2) Each term in the series is separately a solution to the wave equation satisfying the boundary conditions, and so the series sum itself is such a solution. (3) This series is sort of like an expansion of a vector in terms of a set of basis vectors. In this picture the coefficients An are the coordinates of the function . (4) We still have to specify initial conditions and find a method to ensure that they are satisfied.