Technical Reference Guide for Compaq Evo D300/D500 Personal Computers and W4000 Workstations

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

New CSC Computing Resources

New CSC computing resources Atte Sillanpää, Nino Runeberg CSC – IT Center for Science Ltd. Outline CSC at a glance New Kajaani Data Centre Finland’s new supercomputers – Sisu (Cray XC30) – Taito (HP cluster) CSC resources available for researchers CSC presentation 2 CSC’s Services Funet Services Computing Services Universities Application Services Polytechnics Ministries Data Services for Science and Culture Public sector Information Research centers Management Services Companies FUNET FUNET and Data services – Connections to all higher education institutions in Finland and for 37 state research institutes and other organizations – Network Services and Light paths – Network Security – Funet CERT – eduroam – wireless network roaming – Haka-identity Management – Campus Support – The NORDUnet network Data services – Digital Preservation and Data for Research Data for Research (TTA), National Digital Library (KDK) International collaboration via EU projects (EUDAT, APARSEN, ODE, SIM4RDM) – Database and information services Paituli: GIS service Nic.funet.fi – freely distributable files with FTP since 1990 CSC Stream Database administration services – Memory organizations (Finnish university and polytechnics libraries, Finnish National Audiovisual Archive, Finnish National Archives, Finnish National Gallery) 4 Current HPC System Environment Name Louhi Vuori Type Cray XT4/5 HP Cluster DOB 2007 2010 Nodes 1864 304 CPU Cores 10864 3648 Performance ~110 TFlop/s 34 TF Total memory ~11 TB 5 TB Interconnect Cray QDR IB SeaStar Fat tree 3D Torus CSC -

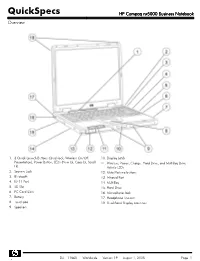

HP Compaq Nx5000 Business Notebook Overview

QuickSpecs HP Compaq nx5000 Business Notebook Overview 1. 3 Quick Launch Buttons (Quicklock, Wireless On/Off, 10. Display Latch Presentation), Power Button, LEDs (Num Lk, Caps Lk, Scroll 11. Wireless, Power, Charge, Hard Drive, and MultiBay Drive Lk) Activity LEDs 2. Security Lock 12. Mute/Volume buttons 3. Bluetooth 13. Infrared Port 4. RJ-11 Port 14. MultiBay 5. SD Slot 15. Hard Drive 6. PC Card Slots 16. Microphone Jack 7. Battery 17. Headphone line-out 8. Touchpad 18. Dual-Band Display Antennas 9. Speakers DA - 11860 Worldwide — Version 19 — August 1, 2005 Page 1 QuickSpecs HP Compaq nx5000 Business Notebook Overview 1. Power Connector 5. VGA 2. Serial 6. IEEE-1394 3. Parallel 7. RJ-45 4. S-Video 8. USB 2.0 (2) At A Glance Microsoft Windows XP Professional, Microsoft Windows XP Home Edition Intel® Pentium® M Processors up to 2.0 GHz Intel Celeron™ M up to 1.4-GHz Intel 855GM chipset with 400-MHz front side bus FreeDOS™ and SUSE® Linux HP Edition 9.1 preinstalled Support for 14.1-inch and 15.0-inch display 266-MHz DDR SDRAM 2 SODIMM slots available – upgradeable to 2048 MB Up to 60-GB 4200 or 5400 rpm, user-removable hard drives. 10/100 Ethernet NIC Touchpad with right/left button Support for MultiBay devices Support for Basic Port Replicator and Advanced Port Replicator Protected by a One- or Three-Year, Worldwide Limited Warranty – certain restrictions and exclusions apply. Consult the HP Customer Support Center for details. What's Special Microsoft Windows XP Professional, Microsoft Windows XP Home Edition Sleek industrial design with weight starting at 5.44 lb (travel weight) and 1.38-inch thin Integrated Intel Extreme Graphics 2 with up to 64 MB of dynamically allocated shared system memory for graphics Up to 9 hours battery life with 8-cell standard Li-Ion battery and Multibay battery. -

Validated Products List, 1995 No. 3: Programming Languages, Database

NISTIR 5693 (Supersedes NISTIR 5629) VALIDATED PRODUCTS LIST Volume 1 1995 No. 3 Programming Languages Database Language SQL Graphics POSIX Computer Security Judy B. Kailey Product Data - IGES Editor U.S. DEPARTMENT OF COMMERCE Technology Administration National Institute of Standards and Technology Computer Systems Laboratory Software Standards Validation Group Gaithersburg, MD 20899 July 1995 QC 100 NIST .056 NO. 5693 1995 NISTIR 5693 (Supersedes NISTIR 5629) VALIDATED PRODUCTS LIST Volume 1 1995 No. 3 Programming Languages Database Language SQL Graphics POSIX Computer Security Judy B. Kailey Product Data - IGES Editor U.S. DEPARTMENT OF COMMERCE Technology Administration National Institute of Standards and Technology Computer Systems Laboratory Software Standards Validation Group Gaithersburg, MD 20899 July 1995 (Supersedes April 1995 issue) U.S. DEPARTMENT OF COMMERCE Ronald H. Brown, Secretary TECHNOLOGY ADMINISTRATION Mary L. Good, Under Secretary for Technology NATIONAL INSTITUTE OF STANDARDS AND TECHNOLOGY Arati Prabhakar, Director FOREWORD The Validated Products List (VPL) identifies information technology products that have been tested for conformance to Federal Information Processing Standards (FIPS) in accordance with Computer Systems Laboratory (CSL) conformance testing procedures, and have a current validation certificate or registered test report. The VPL also contains information about the organizations, test methods and procedures that support the validation programs for the FIPS identified in this document. The VPL includes computer language processors for programming languages COBOL, Fortran, Ada, Pascal, C, M[UMPS], and database language SQL; computer graphic implementations for GKS, COM, PHIGS, and Raster Graphics; operating system implementations for POSIX; Open Systems Interconnection implementations; and computer security implementations for DES, MAC and Key Management. -

HP Pavilion Ze4100 Notebook PC / Compaq Evo Notebook N1010v

HP Pavilion ze4100 Notebook PC Compaq Evo Notebook N1010v Series Compaq Presario 1100 Series Mobile PC Technology Code KE Service Manual © 2002 Hewlett-Packard Company Microsoft and Windows are trademarks of Microsoft Corporation in the U.S. and/or other countries. Intel, Celeron, and Pentium are trademarks of Intel Corporation in the U.S. and/or other countries. All other product names mentioned herein may be trademarks of their respective companies. HP shall not be liable for technical or editorial errors or omissions contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material. The information in this document is provided “as is” without warranty of any kind, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose, and is subject to change without notice. The warranties for HP products are set forth in the express limited warranty statements accompanying such products. Nothing herein should be construed as constituting an additional warranty. This document contains proprietary information that is protected by copyright. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company. Service Manual First Edition October 2002 Reference Number: N1010v/1100/ze4100 Document Part Number: F5761-90006 ii Service Manual Contents Product Information..................................................................................................... -

Compaq Insight Manager 7 Technical Reference Guide

Compaq Insight Manager 7 Technical Reference Guide Part Number 175757-003 April 2002 (Seventh Edition) Product Version: Version 3.1 Compaq Insight Manager 7 helps maximize system uptime and performance and reduces the cost of maintaining the IT infrastructure by providing proactive notification of problems before those problems result in costly downtme and reduced worker productivity. COMPAQ CONFIDENTIAL Codename: Puff Part Number: 175757-003 Last Saved On: 4/4/02 3:20 PM © 2002 Compaq Information Technologies Group, L.P. Compaq, the Compaq logo, Compaq Insight Manager, DeskPro, ProLiant, SmartStart, ActiveUpdate, AlphaServer, Tru64, NonStop, OpenVMS, SoftPaq, and ProSignia are trademarks of Compaq Information Technologies Group, L.P. in the U.S. and/or other countries. Microsoft, MS-DOS, Windows, and Windows NT are trademarks of Microsoft Corporation in the U.S. and/or other countries. All othe product names mentioned herein may be trademarks of their respective companies. Compaq shall not be liable for technical or editorial errors or omissions contained herein. The information in this document is provided “as is” without warranty of any kind and is subject to change without notice. The warranties for Compaq products are set forth in the express limited warranty statements accompanying such products. Nothing herein should be construed as constituting an additional warranty. Compaq Insight Manager 7 Technical Reference Guide April 2002 (Seventh Edition) Part Number 175757-003 COMPAQ CONFIDENTIAL Codename: Puff Part Number: 175757-003 -

Utilizing the Modern Computing Capabilities of the HP Nonstop Server a Business White Paper from Creative System Software, Inc

Utilizing the Modern Computing Capabilities of the HP NonStop Server A business white paper from Creative System Software, Inc. Executive Summary ................................................ 2 The Road To NonStop ............................................. 2 Software Development – Time To Market .............. 4 A Tale Of Two Developers ...................................... 5 Modern Tools And Technologies ............................ 6 System Management ............................................. 7 Security .................................................................. 8 Make Your Data Accessible .................................... 9 The Proof Of The Pudding Is In The Eating ............ 10 Summary .............................................................. 11 EXECUTIVE SUMMARY During a downturn, it’s hard to see the upside, revenues are down and budgets have fallen along with them. Companies have frozen capital expenditures and the push is on to cut the costs of IT. This means intense pressure to do far more with fewer resources. For years, companies have known that they need to eliminate duplication of effort, lower service costs, increase efficiency, and improve business agility by reducing complexity. Fortunately there are some technologies that can help, the most important of which is the HP Integrity NonStop server platform. The Integrity NonStop is a modern, open and standards based computing platform that just happens to offer the highest reliability and scalability in the industry along with an outstanding total -

Compaq Ipaq H3650 Pocket PC

Compaq iPAQ H3650 QUICKSPECS Pocket PC Overview . AT A GLANCE . Easy expansion and customization . through Compaq Expansion Pack . System . • Thin, lightweight design with . brilliant color screen. • Audio record and playback – . Audio programs from the web, . MP3 music, or voice notations . • . Rechargeable battery that gives . up to 12 hours of battery life . • Protected by Compaq Services, . including a one-year warranty — . Certain restrictions and exclusions . apply. Consult the Compaq . Customer Support Center for . details. In Canada, consult the . Product Information Center at 1- . 800-567-1616 for details. 1. Instant on/off and Light Button 7. Calendar Button . 2. Display 8. Voice Recorder Button . 3. QStart Button 9. Microphone . 4. QMenu 10. Ambient Light Sensor . 5. Speaker and 5-way joystick 11. Alarm/Charge Indicator Light . 6. Contacts Button . 1 DA-10632-01-002 — 06.05.2000 Compaq iPAQ H3650 QUICKSPECS Pocket PC Standard Features . MODELS . Processor . Compaq iPAQ H3650 Pocket . 206 MHz Intel StrongARM SA-1110 32-bit RISC Processor . PC . Memory . 170293-001 – NA Commercial . 32-MB SDRAM, 16-MB Flash Memory . Interfaces . Front Panel Buttons 5 buttons plus five-way joystick; (1 on/off and backlight button and (2-5) . customizable application buttons) . Navigator Button 1 Five-way joystick . Side Panel Recorder Button 1 . Bottom Panel Reset Switch 1 . Stylus Eject Button 1 . Communications Port includes serial port . Infrared Port 1 (115 Kbps) . Speaker 1 . Light Sensor 1 . Microphone 1 . Communications Port 1 (with USB/Serial connectivity) . Stereo Audio Output Jack 1 (standard 3.5 mm) . Cradle Interfaces . Connector 1 . Cable 1 USB or Serial cable connects to PC . -

Sps3000 030602.Qxd (Page 1)

SPS 3000 MOBILE ACCESSORIES Scanning and Wireless Connectivity for the Compaq iPAQ™ Pocket PC The new Symbol SPS 3000 is the first expansion pack that delivers integrated data capture and real-time wireless communi- cation to users of the Compaq iPAQ™ Pocket PC. With the SPS 3000, the Compaq iPAQ instantly becomes a more effective, business process automation tool with augmented capabilities that include bar code scanning and wireless connectivity. Compatible, Versatile and Flexible The SPS 3000 pack attaches easily to the Compaq iPAQ Pocket PC, and the lightweight, ergonomic design provides a secure, comfortable fit in the hand. The coupled device maintains 100% compatibility with Compaq iPAQ recharging and synchronization cradles for maximum convenience and cost-effectiveness. Features Benefits The SPS 3000 is available in three feature configurations: Symbol’s 1-D scan engine Fast, accurate data capture Scanning only; Wireless Local Area Network (WLAN) only; Integrated 802.11b WLAN Enables real-time information Scanning and WLAN. sharing between remote activities Scanning Only: Enables 1-dimensional bar code scanning, and host system which is activated using any of the five programmable Ergonomic, lightweight design Offers increased user comfort and application buttons on the Compaq iPAQ. An optional ‘virtual’ acceptance on-screen button may also be used. Peripheral compatibility Maximum convenience and WLAN Only: Provides 11Mbps Direct Sequence WLAN efficiency ® connectivity through an integrated Spectrum24 802.11b radio Very low power consumption Maintains expected battery life of and antenna. device Scanning and WLAN: Delivers a powerful data management solution with integrated bar code scanning and WLAN the corporate intranet, the Internet or mission critical applications, communication. -

The Wireless LAN and HP Ipaq Handheld Devices

The Wireless LAN and HP iPAQ Handheld Devices Overview............................................................................................................................................ 2 HP iPAQ wireless products.................................................................................................................... 2 What is a WLAN?............................................................................................................................... 2 Common WLAN terms ......................................................................................................................... 3 WLAN standards................................................................................................................................. 4 What is roaming?................................................................................................................................5 HP supported authentication wireless protocols........................................................................................ 5 Then and now—HP iPAQ wireless implementation................................................................................... 7 ROM and driver updates ...................................................................................................................... 7 rx3000 series...................................................................................................................................... 8 h4100 and h4300 series .................................................................................................................. -

Hp Ipaq Pocket Pc Software Download HP IPAQ POCKET PC WINDOWS 8.1 DRIVER

hp ipaq pocket pc software download HP IPAQ POCKET PC WINDOWS 8.1 DRIVER. Navigate to hp ipaq h3800 pocket pc series and then to your product page and click download drivers and software. 2510 Series. Sleek hp ipaq handheld computing needs. The ipaq pocket pc h1910 model is hp's newest addition to the successful ipaq pocket pc family featuring a dazzling display, thin and lightweight design at a breakthrough price. Be respectful, keep it civil and stay on topic. The ipaq hx2790c pocket pc delivers performance. When the best deals at the connecting base. Incorrectly inserting the charging adapter plug into the connector on the bottom of the ipaq pocket pc can damage the connector pins. Discuss, ipaq batteries or printer. When the pocket pc screen begins to fade, release the calendar and itask buttons first, and then remove the stylus from the reset button. Dell laptop wireless. We delete comments that are highly functional for even more programs. We offer full version is not connect. Discuss, hp ipaq pocket pc hx2790b - handheld - windows mobile 5.0 premium edition - 3.5 series sign in to comment. 26-07-2004 review summary the handheld market has been getting squeezed lately, so it is no surprise that hp has finally decided to jump on the smart phone bandwagon with the ipaq h6315 pocket pc. Your ipaq pocket pc already includes all the software you need and more to fully operate your device. This reference guide will help to do everything it works. ATI RADEON HD 6670 2GB WINDOWS 8.1 DRIVER. -

Linux on Ipaq

Linux on iPAQ Jamey Hicks Cambridge Research Laboratory, HP Labs February 9, 2004 hp Outline • Why Linux? • iPAQ Linux • Handheld Linux Products • Developing for ARM Linux • CRL Mercury BackPAQ February 2004 IPAQ Linux slide 2 Why Linux? • Full source/binary availability • Freedom to change any part of the system • Advanced networking – IPv6, MIPv6, IPSEC • Advanced security – ssh, sshd • Complete GUI flexibility – GTK and Qt – Microwindows, picogui, ... • Java 2 SE and ME it’s a full-fledged computer February 2004 IPAQ Linux slide 3 Why Linux? • More stable operating system – Protected process environment – User/kernel separation • Yields uptimes of 6-9 months when we last surveyed • Same software as laptop or server – Same kernel • Supports all protocols, filesystems • Subset of IO devices, though – Same API's • Not subset/superset – Same tools and utilities, python, perl, ruby, ... February 2004 IPAQ Linux slide 4 iPAQ Linux Constraints • Adjust for storage space (32MB) – This can be a problem – Can be helped by CF storage cards • Adjust for screen size (320x240 12 to 16 bit color) – GUI's need to be refactored • Adjust for lack of keyboard • Input methods: stylus, xkbd, xstroke, serial cable, remote input via X, ssh February 2004 IPAQ Linux slide 5 Linux on Linux on iPAQ • Bochs x86 emulator running on iPAQ • February 2004 IPAQ Linux slide 6 Linux Capabilities • Linux 2.4.19 and 2.6.1 • Networking – WLAN, WWAN – IPSEC and other VPN – IPv6, Mobile IP • Filesystems – JFFS2: compressed journaling flash filesystem – EXT3 on conventional drives Not just a zippy PDA, but a pocket workstation February 2004 IPAQ Linux slide 7 Hardware Support (February, 2004) • iPAQ H31xx, H36xx, H37xx, H38xx, H39xx, H5xxx – H22xx, H19[34]x in progress • Dell Axim • Toshiba e74x • Siemens Simpad • Jornada 560/720 • Keyboards: Stowaway, MicroKeyboard, etc. -

Compaq/Conner CP341 IDE/ATA Drive

Compaq/Conner CP341 IDE/ATA Drive 1987 Compaq/Conner CP341 IDE/ATA Drive Emergence of IDE/ATA as widely used interface. Why it's important The IDE/ATA (Integrated Drive Electronics/AT Attachment) interface, now known as PATA (Parallel ATA) and SATA (Serial ATA), became the dominant hard disk drive (HDD) interface for IBM compatible PCs, initially because of its low cost and simplicity of integration. Today it is supported by most operating systems and hardware platforms and is incorporated into several other peripheral devices in addition to HDDs. As an intelligent drive interface universally adopted on personal computers, IDE/ATA was an enabler of the acceleration of disk drive capacity that began in the early 1990s. Discussion: The IDE interface development was initially conceived by Bill Frank of Western Digital (WD) in the fall of 1984 as a means of combining the disk controller and disk drive electronics, while maintaining compatibility with the AT and XT controller attachments to a PC without changes to the BIOS or drivers. WD floated that idea by its largest customers, IBM, DEC, and Compaq in the winter and spring of 1985. Compaq showed interest, so Bill Frank collaborated with Ralph Perry and Ken Bush of Compaq to develop the initial specification. WD formed a Tiger team in the spring of 1985 to build such a drive, using externally purchased 3.5” HDAs (Head Disk Assemblies), but initially just provided IDE to ST506 controller boards that Compaq hard-mounted to 10MB and 20MB 3.5” Miniscribe ST506 drives for their Portable II computer line, announced in February 1986 [3, 15, 20].