Setup and Use of the Multimedia Card and Secure Digital Host Controller

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Multimediacard Product Manual

MultiMediaCard Product Manual This manual covers the SanDisk MultiMediaCard which was developed by SanDisk’s Design Center located in Tefen, Israel. The MultiMediaCard supports version 1.4 of the MultiMediaCard Specification. ® CORPORATE HEADQUARTERS 140 Caspian Court Sunnyvale, CA 94089-1000 408-542-0500 FAX: 408-542-0503 URL: http://www.sandisk.com SanDisk® Corporation general policy does not recommend the use of its products in life support applications where in a failure or malfunction of the product may directly threaten life or injury. Per SanDisk Terms and Conditions of Sale, the user of SanDisk products in life support applications assumes all risk of such use and indemnifies SanDisk against all damages. The information in this manual is subject to change without notice. SanDisk Corporation shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or consequential damages resulting from the furnishing, performance, or use of this material. All parts of the SanDisk MultiMediaCard documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form without prior consent, in writing, from SanDisk Corporation. SanDisk and the SanDisk logo are registered trademarks of SanDisk Corporation. Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies. © 2000 SanDisk Corporation. All rights reserved. SanDisk products are covered or licensed under one or more of the following U.S. Patent Nos. 5,070,032; 5,095,344; 5,168,465; 5,172,338; 5,198,380; 5,200,959; 5,268,318; 5,268,870; 5,272,669; 5,418,752; 5,602,987. -

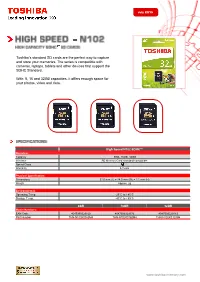

Toshiba's Standard SD Cards Are the Perfect Way to Capture and Store Your Memories. the Series Is Compatible with Cameras

July 2015 Toshiba’s standard SD cards are the perfect way to capture and store your memories. The series is compatible with cameras, laptops, tablets and other devices that support the SDHC Standard. With 8, 16 and 32GB capacities, it offers enough space for your photos, video and data. High Speed N102 SDHC™ Overview: Capacity 8GB, 16GB, 32GB Interface SD Memory Card standard compatible Speed Class * Warranty 5 Years Physical Specification: Dimensions 32.0 mm (L) × 24.0 mm (W) × 2.1 mm (H) Weight Approx. 2g Environmental: Operating Temp. -25°C to +85°C Storage Temp. -40°C to +85°C 8GB 16GB 32GB Model Numbers: EAN Code 4047999329169 4047999329176 4047999329183 Part Number THN-N102K0080M4 THN-N102K0160M4 THN-N102K0320M4 www.toshiba-memory.com In 1984, Toshiba developed a new type of semiconductor memory called flash memory, leading the industry into the next generation ahead of its competitors. Some time later in 1987, NAND flash memory was developed, and this has since been used in a variety of memory cards and electronic equipments. The NAND flash market has grown rapidly, with flash memory becoming an internationally standardized memory device. Toshiba, the inventor of flash memory, has carved out a path to a new era in which we are all able to carry videos, music and data with us wherever we go. History of Flash Memory 1984 Developed NOR-type Flash Memory 1987 Developed NAND-type Flash Memory Jul. 2000 Released SD™ Memory Card Jun. 2003 Released miniSD™ Memory Card Dec. 2003 Released USB Flash Memory Jul. 2006 Released microSD™ Memory Card Oct. -

SDC420T Memory Card

SDC420T memory card Description Features Transcend’s 3D flash technology combines the Transcend’s 3D NAND flash technology advantages of high performance and exceptional Excellent endurance endurance. The industrial memory cards can endure Compatible with SD Specification Ver. 5.1 operating temperatures ranging from -25°C to 85°C; UHS-I with Video Speed Class V10 setting a new standard in consistent, long-term Application Performance Class1 (A1) performance even in the harshest conditions. Early move and Read Retry Built-in ECC and Wear leveling RoHS compliant product. Support ESD IEC 61000-4-2 Architecture Pin Definition SD Mode SPI Mode Pin No. Name Description Name Description 1 CD/DAT3 Card Detect/ Data Line [Bit3] CS Chip Select (neg true) 2 CMD Command/ Response DI Data In 3 VSS1 Supply voltage ground VSS Supply voltage ground 4 VDD Supply voltage VDD Supply voltage 5 CLK Clock SCLK Clock 6 VSS2 Supply voltage ground VSS2 Supply voltage ground 7 DAT0 Data Line [Bit0] DO Data out 8 DAT1 Data Line [Bit1] RSV Reserved 9 DAT2 Data Line [ Bit2 ] RSV Reserved Specifications Physical Specification Form Factor SD SD specification SD5.1 (32GB and larger capacity),SD3.01 (16GB) Length 32.00 ± 0.1 Dimensions (mm) Width 24.00 ± 0.1 Height 2.10 ± 0.15 Data Transfer Specification Application Model P/N SD Type Interface* Speed Class Performance Class TS16GSDC420T SDHC UHS-I SDR104 C10/U1 N/A TS32GSDC420T SDHC UHS-I SDR104 V10/U1 A1 TS64GSDC420T SDHC UHS-I SDR104 V10/U1 A1 TS128GSDC420T SDHC UHS-I SDR104 V10/U1 A1 TS256GSDC420T SDHC UHS-I -

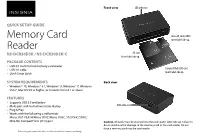

Memory Card Reader • USB 3.0 Cable Compactflash (CF) Card • Quick Setup Guide Insert Label Side Up

Front view LED indicator QUICK SETUP GUIDE Memory Card microSD, microSDXC Reader Insert label side up. NS-DCR30D3K / NS-DCR30D3K-C SD card Insert label side up. PACKAGE CONTENTS • USB 3.0 multi-format memory card reader • USB 3.0 cable CompactFlash (CF) card • Quick Setup Guide Insert label side up. SYSTEM REQUIREMENTS Back view • Windows® 10, Windows® 8.1, Windows® 8, Windows® 7, Windows Vista®, Mac OS 9.0 or higher, or Linux Kernal 2.4.1 or above FEATURES • Supports USB 3.0 and below • Multi-port and multi-driver letter display USB cable port • Plug & Play • Works with the following card formats: Micro SD/T-FLASH/Micro SDXC/Micro SDHC, SD/SDHC/SDXC/ Mini-SD, CompactFlash (CF) type I Caution: All cards must be inserted into the card reader label side up. Failure to do so could result in damage to the memory card or the card reader. Do not force a memory card into the card reader. Before using your new product, please read these instructions to prevent any damage. CONNECTING THE CARD READER 5 Do not remove your card from the card reader until the data LED Plug one end of a USB cable into the USB port of the card reader and stops blinking and the name of your card disappears from the Finder the other end into an available USB port on your computer. Your window. computer loads the drivers automatically. SPECIFICATIONS USING THE CARD READER • Dimensions: 2.87 × 1.98 × .68 in. (7.3 × 5.05 × 1.75 cm) Cautions: • Transmission port: USB 3.0 • Insert a card, label side up, into the appropriate slot. -

All-In-One Photo Printer

MP980 All-In-One Photo Printer Ultimate Wireless1 All-In-One Photo Printer with 3.5" LCD. • Six individual ink system featuring gray ink provides professional color and monochrome photos • ChromaLife100+ system delivers vibrant photos that last up to 300 years2 • Maximum 9600 x 2400 color dpi3 with microscopic droplets as small as 1 picoliter using FINE technology Special Gray Ink • 4800 dpi high resolution CCD scanner for documents and films The six ink system features a Canon exclusive gray ink that gives you professional quality black & white photos. • White LED eliminates warm-up time4 for document scanning Speed & Quality Ease of Use Connectivity 20 2 1 6 7 3 5 MP980 All-In-One Photo Printer Technical Information8 PRINT Print Features Auto Duplex Print, Auto Photo Fix, Borderless Printing,9 Calendar Print, Direct Print, Document Printing, Grayscale Printing, ID Photo Print, Photo Index Sheet, Photo Printing, Template Print Print Speed5 Black Up to 26 ppm (As fast as 2.3 seconds per page) Color Up to 21 ppm (As fast as 2.9 seconds per page) 4” x 6” Borderless Photo Approx. 20 seconds Number of Nozzles Color: 5,632, Black: 512, Total: 6,144 Picoliter Size (Color) 1, 2 and 5 Print Resolution3 Color Up to 9600 x 2400 dpi Black Up to 600 x 600 dpi Paper Sizes 4" x 6," 5" x 7," 8" x 10," Letter, Legal, U.S. #10 Envelopes Paper Tray Capacity Auto Sheet Feeder: 150 Pages, Cassette: 150 Pages (Plain Paper) COPY Copy Features 4 in 1 / 2 in 1, Auto Duplex Copy, Auto Exposure/Intensity Copy, Continuous Copy, Face Brightener/Fading Correction, Film Copy, Fit-to-Page, Image Repeat, Manual Color Adjustment, Masking Copy, Multiple Copy: 1-99 Pages, Photo Reprint, Preset Copy Ratios, Trimming Copy, Zoom 5 Copy Speed Black Up to 24 cpm (As fast as 2.5 seconds per page) Ordering Information Color Up to 19 cpm (As fast as 3.2 seconds per page) Model No. -

Capturemovemanipulates

CAPTUREMOVEMANIPULATESTORE Flash Memory Cards from Simpletech CompactFlash Secure Digital MultiMediaCard RS-MMC miniSD Flash Memory Cards from SimpleTech Capture your digital photos, music, and files with SimpleTech high-speed flash FLASHMEMORYCARDS memory cards. CompactFlash CompactFlash (CF) flash memory cards are the most popular form factor of flash storage used in consumer devices today. CF cards are ideal storage solutions for digital cameras, MP3 players, PDAs, palmtops, and handheld PCs. Features • Low power consumption • Compatible with all CF devices • Hot Swappable • CFA and PCMCIA Compliant • Highest Capacity Available using IC TowerTM Chip Stacking Capacities 32MB-4GB Dimension 1.69" (w) x 1.43" (l) x 0.13" (t) Weight 11.4g Interface ATA True IDE Operating Temperature 0o - 70o C Power 3.3V or 5V Operation Warranty Lifetime Secure Digital Secure Digital (SD) flash memory cards are next generation memory devices that offer a combination of high storage capacity, fast data transfer rates, great flexibility and excellent security. Features • Copyrights protection function • SD and SPI interface supported • Nonvolatile solid-state storage • Mechanical write protect switch Capacities 32MB - 1GB Dimension 0.94" (w) x 1.26" (l) x 0.08" (t) Weight 1g Interface Secure Digital Mode SPI Mode miniSD card adapter can be use in SD card socket Operating Temperature 0o - 70o C Power 2.7V - 3.6V Warranty Lifetime MultiMediaCard MultiMediaCards (MMC) flash memory cards are highly integrated flash products which let you carry more music, images, data, and voice recordings. MMC cards are small but rugged. They are great for MP3 players, digital cameras, voice recorders, smart phones and digital camcorders. -

In-Desk Hub 3 Port USB 3.0 + 2 Slot SD Card Reader

In-Desk Hub 3 Port USB 3.0 + 2 Slot SD Card Reader Description This hub by Delock can be installed into an existing cut-out of the desk with a diameter of 60 mm or 80 mm to lead through the cables for the monitor, keyboard and mouse. At the same time, the hub offers three USB Type-A female ports and one SD Card Reader with two slots. The data transfer and power supply is guaranteed through one USB 3.0 Type-A male and one USB 2.0 Type-A male. The distance between the free connectors can be maximum 20 cm, because the two cables are connected with each other. Specification Item no. 62869 • Connectors: EAN: 4043619628698 top side: 3 x USB 3.0 Type-A female Country of origin: China 1 x SD slot 1 x Micro SD slot Package: Retail Box bottom side: 1 x USB 3.0 Type-A male 1 x USB 2.0 Type-A male (power supply) • Chipset: VL813, GL3233 • Data transfer rate up to: SuperSpeed USB 5 Gbps, Hi-Speed 480 Mbps, Full-Speed 12 Mbps, Low-Speed 1.5 Mbps • The Card Reader supports following memory cards: 1. Slot Secure Digital SD, SD Pro, SD High Capacity (SDHC), SD Ultra, SDHC Ultra, SDXC, SDXC Ultra, MMC-I, MMC-II, MMC 4.0, Mini SD, Mini SDHC, MMCmobile, RS-MMC, RS-MMC 4.0 2. Slot Micro Secure Digital Micro SD, Micro SDHC, Micro SDHC Ultra, T-Flash, MMCmicro • Mounting diameter: 60 mm / 80 mm • Mounting depth: 35 mm • Cable length: ca. -

Card Reader 00200128 "All in One" USB Card Reader, USB-A, USB 3.0

Card Reader 00200128 "All in One" USB Card Reader, USB-A, USB 3.0 Highlightstext: - For connecting a PC, notebook or MacBook to all common memory cards for direct data exchange in both directions - Super speed data transfer rates of up to 5 Gbps - Detachable USB cable for connection to a PC / notebook - Flexible materials guarantee optimum kink protection and prevent cable breakage - High-quality materials and workmanship guarantee excellent transmission quality - Allows fast data transfer between the card and the PC when used with a UDMA capable CF card - Allows fast data transfer between the card and the PC when used with a UHS-I capable SD card - Card reader for reading and writing inserted memory cards - Suitable and tested for USB 3.0, backwards compatible with USB 2.0 - Plug & Play, no manual software / driver installation required - Power supply via USB Memory Cards: - SD/SDHC/SDXC - MicroSD/microSDHC/microSDXC - MMC/MMC Plus/MMC 4.0 - MS/MS Duo/MS PRO Duo/MS PRO-HG - CompactFlash I & II - xD picture card System Requirements: - Operating system: Windows 10/8/7 and Mac OS 10.8 upwards Technical characteristics: - Connection: USB-A Plug - Data Transfer Rate: Up to 5 Gbit/s - USB Standard: USB 3.0 - Memory Card Type 1: CompactFlash Type I, CompactFlash Type II, Memory Stick (TM), Memory Stick Duo (TM), Memory Stick Pro (TM), Memory Stick Pro Duo (TM), Microdrive, MultiMediaCard, SD Card, SDHC Memory Card, SDXC Memory Card, microSD, microSDHC, microSDXC, xD-Card - Type: Cardreader Extern - Width x Depth x Height: 58 x 99 x 17 mm - Colour: Black - Product Division: PC & Notebook - Shade of colour: Black Delivery: - 1 "All in One" USB card reader - 1 USB cable Seite 1 von 2 Hama GmbH & Co KG • Sitz der Gesellschaft: Dresdner Straße 9 • 86653 Monheim/Bayern • GERMANY • Tel. -

USB 3.0 Front Panel Hub + Card Reader Combo Let You Get the Fastest Way to Connect up to USB 3.0 Devices Quickly and Easily

USB 3.0 Front Panel Hub + Card Reader Combo User Manual Ver. 2.00 All brand names and trademarks are properties of their respective owners. Contents: Chapter 1: Introduction ...................................................... 3 1.1 Product Introduction .................................................... 3 1.2 Features ........................................................................ 4 1.3 System Requirements .................................................. 5 1.4 Package Contents ......................................................... 5 Chapter 2: Getting Started ................................................. 5 2.1 Hardware Layout ......................................................... 5 2.2 Hardware Installation .................................................. 7 2.3 Driver Installation ...................................................... 11 MN3000000087 Page 2 Chapter 1: Introduction 1.1 Product Introduction This USB 3.0 Front Panel Hub + Card Reader Combo let you get the fastest way to connect up to USB 3.0 devices quickly and easily. It built-in three USB 3.0 Super-Speed ports, and it is also integrated with one slot card reader. This internal USB 3.0 Front Panel Hub + Card Reader Combo device fits into 3.5’’ or 5.25’’ drive bay to save the desktop space, and it works seamlessly with all USB 1.1 and USB 2.0 devices. With 10 times faster throughput than USB 2.0 standard and backward compatible with current USB device features, you can enjoy fast access for high-bandwidth device such as External hard drives, High -

SD / SDHC / SDIO Card Reader)

EC230 (SD / SDHC / SDIO Card Reader) SD card to Expresscard adapter design for high speed SD cards. You can easily add SD card to your notebook with 34/54mm ExpressCard slot. Specification: Compliant with ExpressCard 1.0 specification Compliant with PCI Express Base Specification rev 1.1 Compliant with SD Memory Card Specification Version 2.0 Support SD High Capacity (SDHC) Compliant with SD Input / Output (SDIO) Card Specification Version 2.0 Compliant with SD Host Controller Standard Specification Version 2.0 Compliant with MMC MultiMediaCard Specification Version 4.1 Supports MMC Plus and MMC Mobile. (4bit only) Dimensions: 34 x 75 x 5mm Weight: 35 g Box Contents: ExpressCard/34 SD Card adapter System Requirements: Notebook or desktop PC with an available ExpressCard slot. Windows 7 (32-/64-bit) / Vista (32-/64-bit) SP2 or later/ XP (32-/64-bit) SP3 or later Special design: ○1 RICOH R5U230 PCIe bridge controller ○2 Serial EEPROM for code upgradeable 3 Hi quality SD push-push connecter ○ Driver download ○4 Expresscard 26PIN connecter Notice To use SD / SDHC Cards on Windows XP/VISTA/7 your system requires install RICOH private driver for more compatibility (download here). Otherwise your SD cards can’t work properly. To use SDIO wireless Cards on Windows 7, your system requires choose Microsoft SDA host inbox driver. And SP1 Update or Windows 7 (KB983177) hotfix update. To use SD / SDHC Memory Card Formatting Software, Please download file from SDCARD.org web-site as below: http://www.sdcard.org/consumers/formatter_3/ Please backup your data before using the formatting program. -

Sandisk Multimediacard and Reduced-Size Multimediacard

SanDisk MultiMediaCard and Reduced-Size MultiMediaCard Product Manual Version 1.3 Document No. 80-36-00320 April 2005 SanDisk Corporation Corporate Headquarters • 140 Caspian Court • Sunnyvale, CA 94089 Phone (408) 542-0500 • Fax (408) 542-0503 www.sandisk.com Revision 1.3 MultiMediaCard/RS-MultiMediaCard Product Manual SanDisk® Corporation general policy does not recommend the use of its products in life support applications where in a failure or malfunction of the product may directly threaten life or injury. Per SanDisk Terms and Conditions of Sale, the user of SanDisk products in life support applications assumes all risk of such use and indemnifies SanDisk against all damages. See “Disclaimer of Liability.” This document is for information use only and is subject to change without prior notice. SanDisk Corporation assumes no responsibility for any errors that may appear in this document, nor for incidental or consequential damages resulting from the furnishing, performance or use of this material. No part of this document may be reproduced, transmitted, transcribed, stored in a retrievable manner or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written consent of an officer of SanDisk Corporation. All parts of the SanDisk documentation are protected by copyright law and all rights are reserved. SanDisk and the SanDisk logo are registered trademarks of SanDisk Corporation. CompactFlash is a U.S. registered trademark of SanDisk Corporation. Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies. -

Download Your FREE Comprehensive Parts Catalog Today!

520 CONNECTORS MEDIA & MEDIA ACCESSORIES NEUTRIK ETHERCON - RJ45 TYPE MAXELL / TDK AUDIO CASSETTES ITEM TYPE ITEM LENGTH DESCRIPTION NE8FDV-Y110 Nickel panel, vertical PCB mount, accepts NE8MC, punch down terminals MAXELL NE8FDP Nickel panel, D-shape, feedthrough receptacle, latch lock, accepts NE8MC MX-COM30 30 Normal bias NE8FDP-B As NE8FDP, but w/black D-series metal flange MX-COM45 45 Normal bias NE8MC RJ45 carrier for RJ45 plugs - shell, fixing disk, chuck, bush & boot MX-COM60 60 Normal bias NE8MC-B As NE8MC but with black chromium shell MX-COM90 90 Normal bias NE8MC-B-1 NE8MC-B version with X series Neutrik black shell MX-COM120 120 Normal bias NE8FF Feedthrough RJ45 coupler for cable extensions BSE-XX Boot accessory for Ethercon series - XX - specify color NE8MC BULK RECORDABLE CD-R ITEM DESCRIPTION CRIMP-ON MODULAR RJ45 JVC (TAIYO YUDEN) – CD-R, 80 min, 52X, sold per spindle ITEM TYPE JCDR-WPY-SB Silver print, thermal, 100/spindle BTX JCDR-ZZP-SB Silver printable, thermal, 100/spindle CD-CAT6M Cat6 plug JCDR-TWY-SB White printable, thermal, 100/spindle PLATINUM TOOLS JCDR-SPT-SK Silver printable, thermal, 100-disc tape wrap 100003B EZ-RJ45 plug for Cat5e (bag of 100) JCDR-WPT-SK White printable, thermal, 100-disc tape wrap JCDR-SPY-SB Silver printable, inkjet, 100/spindle 100026C EZ-RJ11/12 plug (bag of 50) CD-CAT6M JCDR-WPP-SK White printable, inkjet, hub printable, 100-disc tape wrap 100020 EZ-RJ45 shielded cat5e connector (bag of 50) JCDR-ZZ-SB 100-pack spindle, silver 100035 EZ-RJ45 Cat5e snagless boot (bag of 50) JCDR-SPP-SK