Logic Gates Logic: Logic Is Defined As the Science of Reasoning

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Dialetheists' Lies About the Liar

PRINCIPIA 22(1): 59–85 (2018) doi: 10.5007/1808-1711.2018v22n1p59 Published by NEL — Epistemology and Logic Research Group, Federal University of Santa Catarina (UFSC), Brazil. DIALETHEISTS’LIES ABOUT THE LIAR JONAS R. BECKER ARENHART Departamento de Filosofia, Universidade Federal de Santa Catarina, BRAZIL [email protected] EDERSON SAFRA MELO Departamento de Filosofia, Universidade Federal do Maranhão, BRAZIL [email protected] Abstract. Liar-like paradoxes are typically arguments that, by using very intuitive resources of natural language, end up in contradiction. Consistent solutions to those paradoxes usually have difficulties either because they restrict the expressive power of the language, orelse because they fall prey to extended versions of the paradox. Dialetheists, like Graham Priest, propose that we should take the Liar at face value and accept the contradictory conclusion as true. A logical treatment of such contradictions is also put forward, with the Logic of Para- dox (LP), which should account for the manifestations of the Liar. In this paper we shall argue that such a formal approach, as advanced by Priest, is unsatisfactory. In order to make contradictions acceptable, Priest has to distinguish between two kinds of contradictions, in- ternal and external, corresponding, respectively, to the conclusions of the simple and of the extended Liar. Given that, we argue that while the natural interpretation of LP was intended to account for true and false sentences, dealing with internal contradictions, it lacks the re- sources to tame external contradictions. Also, the negation sign of LP is unable to represent internal contradictions adequately, precisely because of its allowance of sentences that may be true and false. -

Automated Unbounded Verification of Stateful Cryptographic Protocols

Automated Unbounded Verification of Stateful Cryptographic Protocols with Exclusive OR Jannik Dreier Lucca Hirschi Sasaˇ Radomirovic´ Ralf Sasse Universite´ de Lorraine Department of School of Department of CNRS, Inria, LORIA Computer Science Science and Engineering Computer Science F-54000 Nancy ETH Zurich University of Dundee ETH Zurich France Switzerland UK Switzerland [email protected] [email protected] [email protected] [email protected] Abstract—Exclusive-or (XOR) operations are common in cryp- on widening the scope of automated protocol verification tographic protocols, in particular in RFID protocols and elec- by extending the class of properties that can be verified to tronic payment protocols. Although there are numerous appli- include, e.g., equivalence properties [19], [24], [27], [51], cations, due to the inherent complexity of faithful models of XOR, there is only limited tool support for the verification of [14], extending the adversary model with complex forms of cryptographic protocols using XOR. compromise [13], or extending the expressiveness of protocols, The TAMARIN prover is a state-of-the-art verification tool e.g., by allowing different sessions to update a global, mutable for cryptographic protocols in the symbolic model. In this state [6], [43]. paper, we improve the underlying theory and the tool to deal with an equational theory modeling XOR operations. The XOR Perhaps most significant is the support for user-specified theory can be freely combined with all equational theories equational theories allowing for the modeling of particular previously supported, including user-defined equational theories. cryptographic primitives [21], [37], [48], [24], [35]. -

ECE 546 Lecture -20 Power Distribution Networks

ECE 546 Lecture ‐20 Power Distribution Networks Spring 2020 Jose E. Schutt-Aine Electrical & Computer Engineering University of Illinois [email protected] ECE 546 – Jose Schutt‐Aine 1 IC on Package ECE 546 – Jose Schutt‐Aine 2 IC on Package ECE 546 – Jose Schutt‐Aine 3 Power-Supply Noise - Power-supply-level fluctuations - Delta-I noise - Simultaneous switching noise (SSN) - Ground bounce VOH Ideal Actual VOL Vout Vout Time 4 ECE 546 – Jose Schutt‐Aine 4 Voltage Fluctuations • Voltage fluctuations can cause the following Reduction in voltage across power supply terminals. May prevent devices from switching Increase in voltage across power supply terminalsreliability problems Leakage of the voltage fluctuation into transistors Timing errors, power supply noise, delta‐I noise, simultaneous switching noise (SSN) ECE 546 – Jose Schutt‐Aine 5 Power-Supply-Level Fluctuations • Total capacitive load associated with an IC increases as minimum feature size shrinks • Average current needed to charge capacitance increases • Rate of change of current (dI/dt) also increases • Total chip current may change by large amounts within short periods of time • Fluctuation at the power supply level due to self inductance in distribution lines ECE 546 – Jose Schutt‐Aine 6 Reducing Power-Supply-Level Fluctuations Minimize dI/dt noise • Decoupling capacitors • Multiple power & ground pins • Taylored driver turn-on characteristics Decoupling capacitors • Large capacitor charges up during steady state • Assumes role of power supply during current switching • Leads -

CS 50010 Module 1

CS 50010 Module 1 Ben Harsha Apr 12, 2017 Course details ● Course is split into 2 modules ○ Module 1 (this one): Covers basic data structures and algorithms, along with math review. ○ Module 2: Probability, Statistics, Crypto ● Goal for module 1: Review basics needed for CS and specifically Information Security ○ Review topics you may not have seen in awhile ○ Cover relevant topics you may not have seen before IMPORTANT This course cannot be used on a plan of study except for the IS Professional Masters program Administrative details ● Office: HAAS G60 ● Office Hours: 1:00-2:00pm in my office ○ Can also email for an appointment, I’ll be in there often ● Course website ○ cs.purdue.edu/homes/bharsha/cs50010.html ○ Contains syllabus, homeworks, and projects Grading ● Module 1 and module are each 50% of the grade for CS 50010 ● Module 1 ○ 55% final ○ 20% projects ○ 20% assignments ○ 5% participation Boolean Logic ● Variables/Symbols: Can only be used to represent 1 or 0 ● Operations: ○ Negation ○ Conjunction (AND) ○ Disjunction (OR) ○ Exclusive or (XOR) ○ Implication ○ Double Implication ● Truth Tables: Can be defined for all of these functions Operations ● Negation (¬p, p, pC, not p) - inverts the symbol. 1 becomes 0, 0 becomes 1 ● Conjunction (p ∧ q, p && q, p and q) - true when both p and q are true. False otherwise ● Disjunction (p v q, p || q, p or q) - True if at least one of p or q is true ● Exclusive Or (p xor q, p ⊻ q, p ⊕ q) - True if exactly one of p or q is true ● Implication (p → q) - True if p is false or q is true (q v ¬p) ● -

Application: Digital Logic Circuits

SECTION 2.4 Application: Digital Logic Circuits Copyright © Cengage Learning. All rights reserved. Application: Digital Logic Circuits Switches “in series” Switches “in parallel” Change closed and on are replaced by T, open and off are replaced by F? Application: Digital Logic Circuits • More complicated circuits correspond to more complicated logical expressions. • This correspondence has been used extensively in design and study of circuits. • Electrical engineers use language of logic when refer to values of signals produced by an electronic switch as being “true” or “false.” • Only that symbols 1 and 0 are used • symbols 0 and 1 are called bits, short for binary digits. • This terminology was introduced in 1946 by the statistician John Tukey. Black Boxes and Gates Black Boxes and Gates • Circuits: transform combinations of signal bits (1’s and 0’s) into other combinations of signal bits (1’s and 0’s). • Computer engineers and digital system designers treat basic circuits as black boxes. • Ignore inside of a black box (detailed implementation of circuit) • focused on the relation between the input and the output signals. • Operation of a black box is completely specified by constructing an input/output table that lists all its possible input signals together with their corresponding output signals. Black Boxes and Gates One possible correspondence of input to output signals is as follows: An Input/Output Table Black Boxes and Gates An efficient method for designing more complicated circuits is to build them by connecting less complicated black box circuits. Gates can be combined into circuits in a variety of ways. If the rules shown on the next page are obeyed, the result is a combinational circuit, one whose output at any time is determined entirely by its input at that time without regard to previous inputs. -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

Shalack V.I. Semiotic Foundations of Logic

Semiotic foundations of logic Vladimir I. Shalack abstract. The article offers a look at the combinatorial logic as the logic of signs operating in the most general sense. For this it is proposed slightly reformulate it in terms of introducing and replacement of the definitions. Keywords: combinatory logic, semiotics, definition, logic founda- tions 1 Language selection Let’s imagine for a moment what would be like the classical logic, if we had not studied it in the language of negation, conjunction, dis- junction and implication, but in the language of the Sheffer stroke. I recall that it can be defined with help of negation and conjunction as follows A j B =Df :(A ^ B): In turn, all connectives can be defined with help of the Sheffer stroke in following manner :A =Df (A j A) A ^ B =Df (A j B) j (A j B) A _ B =Df (A j A) j (B j B) A ⊃ B =Df A j (B j B): Modus ponens rule takes the following form A; A j (B j B) . B 226 Vladimir I. Shalack We can go further and following the ideas of M. Sch¨onfinkel to define two-argument infix quantifier ‘jx’ x A j B =Df 8x(A j B): Now we can use it to define Sheffer stroke and quantifiers. x A j B =Df A j B where the variable x is not free in the formulas A and B; y x y 8xA =Df (A j A) j (A j A) where the variable y is not free in the formula A; x y x 9xA =Df (A j A) j (A j A) where the variable y is not free in the formula A. -

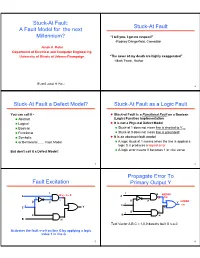

Stuck-At Fault As a Logic Fault

Stuck-At Fault: Stuck-At Fault A Fault Model for the next Millennium? “I tell you, I get no respect!” -Rodney Dangerfield, Comedian Janak H. Patel Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign “The news of my death are highly exaggerated” -Mark Twain, Author © 2005 Janak H. Patel 2 Stuck-At Fault a Defect Model? Stuck-At Fault as a Logic Fault You can call it - z Stuck-at Fault is a Functional Fault on a Boolean Abstract (Logic) Function Implementation Logical z It is not a Physical Defect Model Boolean Stuck-at 1 does not mean line is shorted to VDD Functional Stuck-at 0 does not mean line is grounded! Symbolic z It is an abstract fault model or Behavioral …... Fault Model A logic stuck-at 1 means when the line is applied a logic 0, it produces a logical error But don’t call it a Defect Model! A logic error means 0 becomes 1 or vice versa 3 4 Propagate Error To Fault Excitation Primary Output Y 1 1 G ERROR A G s - a - 0 A 0 1 x X 1/0 D 1 D F ERROR F 0 Y 0 C 1/0 C Y 0 0 0 E E B H B H Test Vector A,B,C = 1,0,0 detects fault G s-a-0 Activates the fault s-a-0 on line G by applying a logic value 1 in line G 5 6 Unmodeled Defect Detection Defect Sites z Internal to a Logic Gate or Cell Other Logic Transistor Defects – Stuck-On, Stuck-Open, Leakage, Shorts between treminals ERROR Defect G ERROR z External to a Gate or Cell Interconnect Defects – Shorts and Opens D 1 F 0 Y ERROR C 0 0 0 E B H G I 7 8 Defects in Physical Cells Fault Modeling z Physical z Electrical Physical Cells such as NAND, NOR, XNOR, AOI, OAI, MUX2, etc. -

CS 173: Discrete Structures, Spring 2012 Homework 1 Solutions

CS 173: Discrete Structures, Spring 2012 Homework 1 Solutions This homework contains 3 problems worth a total of 25 points. 1. [1 point] Finding information on Piazza How many pet rats does Margaret’s family have? (Hint: see Piazza.) Solution: Margaret’s family has six pet rats. 2. [4 points] Demographic Survey 3. [20 points] Logic operators The late 19th century philosopher Charles Peirce (rhymes with ‘hearse,’ not ‘fierce’) wrote about a set of logically dual operators and, in his writings, coined the term ‘Ampheck’ to describe them. The two most common Ampheck operators, the Peirce arrow (written ↓ or ⊥ or ∨ by different people) and the Sheffer stroke (written ↑ or | or ∧ by different people), are defined by the following truth table: p q p ↑ q p ↓ q T T F F T F T F F T T F F F T T (a) (4 points) The set of operators {∧, ∨, ¬} is functionally complete, which means that every logical statement can be expressed using only these three operators. Is the smaller set of operators {∨, ¬} also functionally complete? Explain why or why not. Solution: By De Morgan’s laws, ¬(¬p∨¬q) ≡ ¬¬p∧¬¬q ≡ p∧q So every logical statement using the ∧ operator can be rewritten in terms of the ∨ and ¬ operators. Since every logical statement can be expressed in terms of the ∧, ∨, and ¬ operators, this implies that every logical statement can be expressed in terms of the ∨ and ¬ operators, and so {∨, ¬} is functionally complete. (b) (4 points) Express ¬p using only the Sheffer stroke operation ↑. Solution: Note that ¬p is true if and only if p is false. -

Least Sensitive (Most Robust) Fuzzy “Exclusive Or” Operations

Need for Fuzzy . A Crisp \Exclusive Or" . Need for the Least . Least Sensitive For t-Norms and t- . Definition of a Fuzzy . (Most Robust) Main Result Interpretation of the . Fuzzy \Exclusive Or" Fuzzy \Exclusive Or" . Operations Home Page Title Page 1 2 Jesus E. Hernandez and Jaime Nava JJ II 1Department of Electrical and J I Computer Engineering 2Department of Computer Science Page1 of 13 University of Texas at El Paso Go Back El Paso, TX 79968 [email protected] Full Screen [email protected] Close Quit Need for Fuzzy . 1. Need for Fuzzy \Exclusive Or" Operations A Crisp \Exclusive Or" . Need for the Least . • One of the main objectives of fuzzy logic is to formalize For t-Norms and t- . commonsense and expert reasoning. Definition of a Fuzzy . • People use logical connectives like \and" and \or". Main Result • Commonsense \or" can mean both \inclusive or" and Interpretation of the . \exclusive or". Fuzzy \Exclusive Or" . Home Page • Example: A vending machine can produce either a coke or a diet coke, but not both. Title Page • In mathematics and computer science, \inclusive or" JJ II is the one most frequently used as a basic operation. J I • Fact: \Exclusive or" is also used in commonsense and Page2 of 13 expert reasoning. Go Back • Thus: There is a practical need for a fuzzy version. Full Screen • Comment: \exclusive or" is actively used in computer Close design and in quantum computing algorithms Quit Need for Fuzzy . 2. A Crisp \Exclusive Or" Operation: A Reminder A Crisp \Exclusive Or" . Need for the Least . -

Boolean Logic

Boolean logic Lecture 12 Contents . Propositions . Logical connectives and truth tables . Compound propositions . Disjunctive normal form (DNF) . Logical equivalence . Laws of logic . Predicate logic . Post's Functional Completeness Theorem Propositions . A proposition is a statement that is either true or false. Whichever of these (true or false) is the case is called the truth value of the proposition. ‘Canberra is the capital of Australia’ ‘There are 8 day in a week.’ . The first and third of these propositions are true, and the second and fourth are false. The following sentences are not propositions: ‘Where are you going?’ ‘Come here.’ ‘This sentence is false.’ Propositions . Propositions are conventionally symbolized using the letters Any of these may be used to symbolize specific propositions, e.g. :, Manchester, , … . is in Scotland, : Mammoths are extinct. The previous propositions are simple propositions since they make only a single statement. Logical connectives and truth tables . Simple propositions can be combined to form more complicated propositions called compound propositions. .The devices which are used to link pairs of propositions are called logical connectives and the truth value of any compound proposition is completely determined by the truth values of its component simple propositions, and the particular connective, or connectives, used to link them. ‘If Brian and Angela are not both happy, then either Brian is not happy or Angela is not happy.’ .The sentence about Brian and Angela is an example of a compound proposition. It is built up from the atomic propositions ‘Brian is happy’ and ‘Angela is happy’ using the words and, or, not and if-then. -

Logic, Proofs

CHAPTER 1 Logic, Proofs 1.1. Propositions A proposition is a declarative sentence that is either true or false (but not both). For instance, the following are propositions: “Paris is in France” (true), “London is in Denmark” (false), “2 < 4” (true), “4 = 7 (false)”. However the following are not propositions: “what is your name?” (this is a question), “do your homework” (this is a command), “this sentence is false” (neither true nor false), “x is an even number” (it depends on what x represents), “Socrates” (it is not even a sentence). The truth or falsehood of a proposition is called its truth value. 1.1.1. Connectives, Truth Tables. Connectives are used for making compound propositions. The main ones are the following (p and q represent given propositions): Name Represented Meaning Negation p “not p” Conjunction p¬ q “p and q” Disjunction p ∧ q “p or q (or both)” Exclusive Or p ∨ q “either p or q, but not both” Implication p ⊕ q “if p then q” Biconditional p → q “p if and only if q” ↔ The truth value of a compound proposition depends only on the value of its components. Writing F for “false” and T for “true”, we can summarize the meaning of the connectives in the following way: 6 1.1. PROPOSITIONS 7 p q p p q p q p q p q p q T T ¬F T∧ T∨ ⊕F →T ↔T T F F F T T F F F T T F T T T F F F T F F F T T Note that represents a non-exclusive or, i.e., p q is true when any of p, q is true∨ and also when both are true.