ISL8024DEMO2Z User Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Airships Over Lincolnshire

Airships over Lincolnshire AIRSHIPS Over Lincolnshire explore • discover • experience explore Cranwell Aviation Heritage Museum 2 Airships over Lincolnshire INTRODUCTION This file contains material and images which are intended to complement the displays and presentations in Cranwell Aviation Heritage Museum’s exhibition areas. This file looks at the history of military and civilian balloons and airships, in Lincolnshire and elsewhere, and how those balloons developed from a smoke filled bag to the high-tech hybrid airship of today. This file could not have been created without the help and guidance of a number of organisations and subject matter experts. Three individuals undoubtedly deserve special mention: Mr Mike Credland and Mr Mike Hodgson who have both contributed information and images for you, the visitor to enjoy. Last, but certainly not least, is Mr Brian J. Turpin whose enduring support has added flesh to what were the bare bones of the story we are endeavouring to tell. These gentlemen and all those who have assisted with ‘Airships over Lincolnshire’ have the grateful thanks of the staff and volunteers of Cranwell Aviation Heritage Museum. Airships over Lincolnshire 3 CONTENTS Early History of Ballooning 4 Balloons – Early Military Usage 6 Airship Types 7 Cranwell’s Lighter than Air section 8 Cranwell’s Airships 11 Balloons and Airships at Cranwell 16 Airship Pioneer – CM Waterlow 27 Airship Crews 30 Attack from the Air 32 Zeppelin Raids on Lincolnshire 34 The Zeppelin Raid on Cleethorpes 35 Airships during the inter-war years -

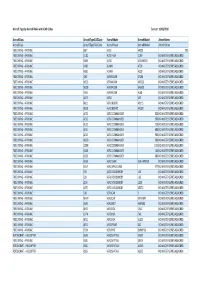

Aircraft Type by Aircraft Make with ICAO Codes Current 10/08/2016

Aircraft Type by Aircraft Make with ICAO Codes Current 10/08/2016 AircraftClass AircraftTypeICAOCode AircraftMake AircraftModel AircraftSeries AircraftClass AircraftTypeICAOCode AircraftMake AircraftModel AircraftSeries FIXED WING ‐ AIRPLANE AJ27 ACAC ARJ21 700 FIXED WING ‐ AIRPLANE CUB2 ACES HIGH CUBY NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE SACR ACRO ADVANCED NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE A700 ADAM A700 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE A500 ADAM A500 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE F26T AERMACCHI SF260 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE M326 AERMACCHI MB326 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE M308 AERMACCHI MB308 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE LA60 AERMACCHI AL60 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AAT3 AERO AT3 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AB11 AERO BOERO AB115 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AB18 AERO BOERO AB180 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AC52 AERO COMMANDER 520 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AC50 AERO COMMANDER 500 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AC72 AERO COMMANDER 720 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AC6L AERO COMMANDER 680 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE AC56 AERO COMMANDER 560 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE M200 AERO COMMANDER 200 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE JCOM AERO COMMANDER 1121 NO MASTER SERIES ASSIGNED FIXED WING ‐ AIRPLANE VO10 AERO COMMANDER 100 NO MASTER -

Ballooning Collection, the Cuthbert-Hodgson Collection, Which Is Probably One of the fi Nest of Its Kind in the World

SOCIETY NEWS qÜÉ=pçÅáÉíóÛë=iáÄê~êó b~êäó=_~ääççåáåÖ iáíÜçÖê~éÜë=~åÇ=mêáåíë ÜÉ=oçó~ä=^Éêçå~ìíáÅ~ä=pçÅáÉíó áãéçêí~åí=îáëì~ä=êÉÅçêÇ=çÑ=ã~åÛë qiáÄê~êó= ÜçìëÉë= çåÉ= çÑ= íÜÉ É~êäó= ~ëÅÉåíë= áåíç= íÜÉ= ~áê= ~í= íÜÉ ïçêäÇÛë=ÑáåÉëí=ÅçääÉÅíáçåë=çÑ=É~êäó îÉêó= Ç~ïå= çÑ= ~îá~íáçå= ~ë Ä~ääççåáåÖ= ã~íÉêá~ä= EÄççâëI éçêíê~óÉÇ= Äó= áääìëíê~íçêë= ~åÇ é~ãéÜäÉíëI= åÉïëé~éÉê= ÅìííáåÖëI ÉåÖê~îÉêë=çÑ=íÜÉ=íáãÉK éêáåíë= ~åÇ= äáíÜçÖê~éÜë= ~åÇ qÜÉ= Ä~ääççå= ï~ë= Äçêå= áå ÅçããÉãçê~íáîÉ= ãÉÇ~äëF= ïÜáÅÜ cê~åÅÉ= áå= NTUP= ÇìêáåÖ= íÜÉ= ä~íÉJ Ü~ë= ÄÉÉå= ìëÉÇ= Äó= êÉëÉ~êÅÜÉêë NUíÜ= ÅÉåíìêó= båäáÖÜíÉåãÉåí Ñêçã= dÉêã~åóI= cê~åÅÉ= ~åÇ= íÜÉ éìêëìáí= çÑ= ëÅáÉåíáÑáÅ= âåçïäÉÇÖÉX råáíÉÇ=pí~íÉëK íÜÉ=~Äáäáíó=íç=íê~îÉä=íÜêçìÖÜ=íÜÉ `çãéäÉãÉåíáåÖ= íÜÉ= ÑáåÉ ~áê=çéÉåÉÇ=ìé=éÉçéäÉëÛ=ãáåÇë=íç ÅçääÉÅíáçå= çÑ= É~êäó= Ä~ääççåáåÖ íÜÉ= éçëëáÄáäáíáÉë= çÑ= ~Éêá~ä ~åÇ= ~Éêçå~ìíáÅ~ä= Äççâë= áë= ~ å~îáÖ~íáçå=~åÇ=åÉïë=çÑ=íÜÉ=É~êäó ã~àçê= ÅçääÉÅíáçå= çÑ= ~êçìåÇ= TMM ~ëÅÉåíë= ï~ë= íê~åëãáííÉÇ= ê~éáÇäó É~êäó= Ä~ääççåáåÖ= äáíÜçÖê~éÜëL ~Åêçëë= bìêçéÉK= ^= é~êí= çÑ= íÜáë éêáåíëLéçëíÉêëK= qÜáë= ÅçääÉÅíáçå= Ô éêçÅÉëë= ï~ë= íÜÉ= éêçÇìÅíáçå= çÑ ïÜáÅÜ= áë= Ä~ëÉÇ= ã~áåäó= çå= íÜÉ åìãÉêçìë= äáíÜçÖê~éÜëLéêáåíë ÜçäÇáåÖë= çÑ= íÜÉ= `ìíÜÄÉêíJ ÅçããÉãçê~íáåÖ= é~êíáÅìä~ê eçÇÖëçå= `çääÉÅíáçå= EïÜáÅÜ= ï~ë ~ëÅÉåíë= çê= ~Éêá~ä= îçó~ÖÉëI= ~åÇ áå=NVQT=éìêÅÜ~ëÉÇ=áå=áíë=ÉåíáêÉíó íÜÉ= iáÄê~êó= ÜçäÇë= Éñ~ãéäÉë= çÑ Äó= páê= cêÉÇÉêáÅâ= e~åÇäÉó= m~ÖÉ ã~åó= îáÉïë= çÑ= ~ëÅÉåíë= ~Åêçëë o^Ép=iáÄê~êó=éÜçíçëK ~åÇ= éêÉëÉåíÉÇ= íç= íÜÉ= pçÅáÉíóI _êáí~áåI= cê~åÅÉ= ~åÇ= çíÜÉê dÉçêÖÉ=`êìáÅâëÜ~åâ=Úq~ñá=_~ääççåëÛ=Ô Ú^=ëÅÉåÉ=áå=íÜÉ=c~êÅÉ=çÑ=içÑíó -

Brooklands Aerodrome & Motor

BROOKLANDS AERODROME & MOTOR RACING CIRCUIT TIMELINE OF HERITAGE ASSETS Brooklands Heritage Partnership CONSULTATION COPY (June 2017) Radley House Partnership BROOKLANDS AERODROME & MOTOR RACING CIRCUIT TIMELINE OF HERITAGE ASSETS CONTENTS Aerodrome Road 2 The 1907 BARC Clubhouse 8 Bellman Hangar 22 The Brooklands Memorial (1957) 33 Brooklands Motoring History 36 Byfleet Banking 41 The Campbell Road Circuit (1937) 46 Extreme Weather 50 The Finishing Straight 54 Fuel Facilities 65 Members’ Hill, Test Hill & Restaurant Buildings 69 Members’ Hill Grandstands 77 The Railway Straight Hangar 79 The Stratosphere Chamber & Supersonic Wind Tunnel 82 Vickers Aviation Ltd 86 Cover Photographs: Aerial photographs over Brooklands (16 July 2014) © reproduced courtesy of Ian Haskell Brooklands Heritage Partnership CONSULTATION COPY Radley House Partnership Timelines: June 2017 Page 1 of 93 ‘AERODROME ROAD’ AT BROOKLANDS, SURREY 1904: Britain’s first tarmacadam road constructed (location?) – recorded by TRL Ltd’s Library (ref. Francis, 2001/2). June 1907: Brooklands Motor Circuit completed for Hugh & Ethel Locke King and first opened; construction work included diverting the River Wey in two places. Although the secondary use of the site as an aerodrome was not yet anticipated, the Brooklands Automobile Racing Club soon encouraged flying there by offering a £2,500 prize for the first powered flight around the Circuit by the end of 1907! February 1908: Colonel Lindsay Lloyd (Brooklands’ new Clerk of the Course) elected a member of the Aero Club of Great Britain. 29/06/1908: First known air photos of Brooklands taken from a hot air balloon – no sign of any existing route along the future Aerodrome Road (A/R) and the River Wey still meandered across the road’s future path although a footbridge(?) carried a rough track to Hollicks Farm (ref. -

A 9 7 A96 A920

B 9 0 R76 0 R77 S S 1 43 6 C 4 C R177 S 7 4 C88S B992 C R176 S 85 C C 5 8 C S 8 7 S 5 1 C 9 C 8 6 A C 4 S C87S R71 C 8 3S 20 R154 9 R160 A C C 5 8 R163 R138 9 2 R184 S S R156 R161 R210 R164 R165 A R66 96 R159 R157 R214 R62 R63 R25 R212 S 0 R211 6 R68 C R60 R166 R40 R151 C 7 9 R31 S S R 8 6 C C 66S 002 B9 S 2 6 C Route Option Air Quality Features Proje c t N am e ! Cyan Affe c te d Re c e ptors A947 A96 Dualling East of Huntly to Abe rd e e n Pink Affe c te d Road N e twork Map Title Old m e ld rum Figure 10.1 !( First Issue Air Quality Affe c te d Road N e twork and Huntly 2 C01 DTU C MMAT DMON LW AR N HAC !( W orst Case Re c e ptors – C-P-V Option Inve rurie 16/11/20 16/11/20 18/11/20 19/11/20 20/11/20 1 !( A96 A97 Kintore Re vision Cre ate d Che c ke d Re vie we d Approve d Authorise d She e t 1 of 3 !( 3 !( Kilom e tre s Map N um be r Insc h | Proje c t | Originator | V olum e | !( Ke m nay 0 1 2 3 4 A96PEA - AMAR - EAQ - Rhynie Sc ale @ A3: 1:50,000 Proje c t Re f. -

View Figure 10.13-10.24 Air Quality Red-Pink

B 9 0 R76 0 R77 S S 1 43 6 C 4 C R177 S 7 4 C88S B992 C R176 S 85 C C 5 8 C S 8 7 S 5 1 9 C 8 A C C87S R71 C 6 4 S C 8 3S 20 R154 9 R160 A C C 5 8 R163 R138 9 2 R184 S S R156 R161 R164 R158 R165 A9 R66 6 R185 R159 R157 R214 R155 R62 R63 R25 R212 R153 S 0 R211 6 R68 C R60 R152 R166 R40 R151 C 7 9 R31 S S R 8 6 C C 66S 002 B9 S 2 6 C Route Option Air Quality Features Proje c t N am e ! Re d Affe c te d Re c e ptors A947 A96 Dualling East of Huntly to Abe rd e e n Pink Affe c te d Road N e twork Map Title Old m e ld rum Figure 10.13 !( First Issue Air Quality Affe c te d Road N e twork and Huntly 2 C01 DTU C MMAT DMON LW AR N HAC !( W orst Case Re c e ptors – R-P-V Option Inve rurie 16/11/20 16/11/20 18/11/20 19/11/20 20/11/20 1 !( A96 A97 Kintore Re vision Cre ate d Che c ke d Re vie we d Approve d Authorise d She e t 1 of 3 !( 3 !( Kilom e tre s Map N um be r Insc h | Proje c t | Originator | V olum e | !( Ke m nay 0 1 2 3 4 A96PEA - AMAR - EAQ - Rhynie Sc ale @ A3: 1:50,000 Proje c t Re f. -

2020 Call for Papers

THE AIRSHIP ASSOCIATION Limited by guarantee th 12 International Airship Convention and Regatta RETROSPECTION AND RESURGENCE Bedford, England : 30th September – 3rd October 2020 Invitation to Participate Major subject areas for consideration are: You are hereby cordially invited to attend the 1. Current Projects and Technology Airship Association’s 12th International Convention 2. History and Learning from the Past and Model Regatta, which is to be held, jointly in 3. Flight Operations and Potential Growth Areas collaboration with the Airship Heritage Trust, from 4. Infrastructure and Ground Handling Wednesday 30th September to Saturday 3rd October 5. Loading and Unloading Payloads 2020 at the Mercure Bedford Centre Hotel, 2 St 6. Management/Regulation and Safety Mary’s Street, Bedford MK42 0AR United Kingdom 7. Market Finance/Leasing/Insurance (formerly Radisson Park Inn). 8. Innovation/R&D/Environmental Impact 9. Education/Training/Skills and Simulations Bedford is a cosmopolitan town with a rich airship 10. Fun, Fantasy and Futuristic Concepts heritage. Centrally located between London, Oxford and Cambridge it is close to the village of Interested contributors should submit an Abstract of Cardington, which was home to Britain’s Royal 250-words maximum (no figures or references) to: Airship Works some 90 years ago. The giant sheds [email protected] that housed the great rigid airships R100 and R101 Abstract submission deadline: 30th June 2020 still exist today, but they are currently in use as film st studios and consequently closed to public access. Paper selection decision by: 31 July 2020 Paper ready for publication: 2nd October 2020 Convention delegates will be able to participate in a full two-day technical conference as well as Abstracts should include indication of their author’s enjoying the opportunity to network with the world’s preferred subject areas from those listed above. -

Productivity and Costs: Second Quarter 2009, Preliminary

Transmission of this material is embargoed until USDL-09-0933 8:30 a.m. (EDT) Tuesday, August 11, 2009 Technical information: (202) 691-5606 • [email protected] • www.bls.gov/lpc Media contact: (202) 691-5902 • [email protected] This release was reissued on the afternoon of Tuesday, August 11, 2009, to correct information on compensation per hour, real compensation per hour, unit labor costs, and unit non-labor payments in Tables 1 through 5 and Appendix tables 1 and 2. In the tables, all index levels for these data series were corrected; as a result, percent changes derived from the corrected index levels were changed slightly in a few cases. No other portions of the news release were affected. PRODUCTIVITY AND COSTS Second Quarter 2009, Preliminary The Bureau of Labor Statistics of the U.S. Department of Labor today reported preliminary productivity data—as measured by output per hour of all persons—for the second quarter of 2009. The seasonally adjusted annual rates of productivity change in the second quarter were: 6.3 percent in the business sector and 6.4 percent in the nonfarm business sector. Productivity gains in both sectors were the largest since the third quarter of 2003, and were due to hours worked declining faster than output. In manufacturing, the preliminary productivity changes in the second quarter were: 5.3 percent in manufacturing, 3.9 percent in durable goods manufacturing, and 2.0 percent in nondurable goods manufacturing. The increases in productivity in all manufacturing sectors were the result of hours falling faster than output. -

Airships in International Affairs, 1890–1940 Also by John Duggan

Airships in International Affairs, 1890–1940 Also by John Duggan LZ 130 GRAF ZEPPELIN AND THE END OF COMMERCIAL AIRSHIP TRAVEL (with Manfred Bauer) COMMERCIAL ZEPPELIN FLIGHTS TO SOUTH AMERICA (with Jim Graue) ZEPPELINPOST LZ 130 (with Gisela Woodward) GRAF ZEPPELIN FLIGHTS TO ENGLAND GRAF ZEPPELIN FLIGHTS TO THE BALKANS GRAF ZEPPELIN POLAR POST (with Gisela Woodward) Also by Henry Cord Meyer COUNT ZEPPELIN: A Psychological Portrait AIRSHIPMEN, BUSINESSMEN AND POLITICS, 1890–1940 THE LONG GENERATION: Germany from Empire to Ruin, 1913–1946 FIVE IMAGES OF GERMANY: Half a Century of American Views on German History MITTELEUROPA IN GERMAN THOUGHT AND ACTION, 1815–1945 Airships in International Affairs, 1890–1940 John Duggan Management Consultant specializing in Oil Industry Economics and Henry Cord Meyer Research Professor Emeritus University of California Irvine © John Duggan and Henry Cord Meyer 2001 Softcover reprint of the hardcover 1st edition 2001 978-0-333-75128-2 All rights reserved. No reproduction, copy or transmission of this publication may be made without written permission. No paragraph of this publication may be reproduced, copied or transmitted save with written permission or in accordance with the provisions of the Copyright, Designs and Patents Act 1988, or under the terms of any licence permitting limited copying issued by the Copyright Licensing Agency, 90 Tottenham Court Road, London W1P 0LP. Any person who does any unauthorised act in relation to this publication may be liable to criminal prosecution and civil claims for damages. The authors have asserted their rights to be identified as the authors of this work in accordance with the Copyright, Designs and Patents Act 1988. -

Shute-R-100 Article

The R 100 Century of Flight Launched on 19th July 1921, the R80 was the first truly streamlined British airship. Statistics: Length 719.5ft Diameter 133.5ft Speed 64mph Engines 6 x 650hp Volume 5, 156, 000cft www.century-of-flight.net 1 The R 100 Century of Flight Following the completion of the R101, the R100 followed closely on being a innovative and modern ship when compared to it's counterparts at the time. The daring decision to move way from the more traditional Zeppelin design lines were shown in the more oval, streamlined and aerodynamic shape of both the R100 and R101. With the decision to construct two ships, one by the Royal Airship Works and the other by a commercial contractor, the contract for the R100 had been awarded to Vickers, who were seen as one of the best airship constructors considering their history with lighter than air craft. A new subsidiary, the Airship Guarantee Company was set up purely for the construction of the ship. It was seen by the government that having 2 prototypes built would lead to twice the amount of new ideas and innovation over traditional lines. Both the R100 and R101 teams were the first to build the more aerodynamic airships than the traditional Zeppelin designs. The British designers had always tried to add in the aerodynamic shape to add efficiency, in to the design of the craft compared to contemporary ships. The R 80 being the case in point, being the most aerodynamic ship constructed to date. With Barnes Wallis using new design techniques assisted by Neville Shute-Norway as his chief calculator, the R100 designed as a unique and efficient craft. -

February 7, 1995 PR

Internet address: http://www.bls.gov/lpc/ USDL 04-119 Historical, technical TRANSMISSION OF THIS information: (202) 691-5606 MATERIAL IS EMBARGOED Current data: (202) 691-5200 UNTIL 8:30 A.M. EST, Media contact: (202) 691-5902 THURSDAY, FEBRUARY 5, 2004 PRODUCTIVITY AND COSTS Preliminary Fourth Quarter and Annual Averages for 2003 The Bureau of Labor Statistics of the U.S. Department of Labor today reported preliminary productivity data—as measured by output per hour of all persons—for the fourth quarter and for the full year 2003. The seasonally adjusted annual rates of productivity change in the fourth quarter and the annual average changes were: Fourth Annual averages quarter 2002-2003 Business sector 1.8 4.3 Nonfarm business sector 2.7 4.2 In the fourth quarter, productivity increased 1.8 percent in the business sector following an 8.7-percent increase (as revised) one quarter earlier (seasonally adjusted annual rates). In nonfarm businesses, productivity also grew more slowly in the fourth quarter, 2.7 percent, than it had one quarter earlier, when it rose 9.5 percent. On an annual average basis, productivity rose 4.3 percent in the business sector and 4.2 percent in the nonfarm business sector. Fourth-quarter productivity and related measures are summarized in table A and annual average data in table B. Detailed information is presented in tables 1 through 5. In the manufacturing sector, increases in productivity were: Fourth Annual averages quarter 2002-2003 Manufacturing sector 4.8 4.3 Durable goods manufacturing 6.4 6.7 Nondurable goods manufacturing 3.8 1.2 Productivity and cost measures for the manufacturing sector are now reported using the 2002 North American Industry Classification System (NAICS). -

Leedslines the Newsletter of the Leeds Society of Model & Experimental Engineers

LEEDSLINES THE NEWSLETTER OF THE LEEDS SOCIETY OF MODEL & EXPERIMENTAL ENGINEERS Volume 16 Issue 3 July 2014 Leeds SMEE web site may be found at: http://leeds.smee.googlepages.com THE VIEWS EXPRESSED IN THIS NEWSLETTER ARE NOT NECESSARILY THE VIEWS OF THE COMMITTEE Editorial This is the first issue produced by me as new LeedsLines editor. Despite Chairman Jack’s reassurances to members that I was completely ‘au fait’ with Microsoft Publisher it would have been nearer the mark to say I was aware it existed. Fortunately skills learned from other Office products seem to translate well to the new environment and by adopting an ‘if it isn’t broken don’t fix it’ approach I hope to continue the sterling work of past editors without any mishaps. Time will tell! I have already found members willing to provide interesting articles to include in the newsletter . If you have a story, report on some event you have attended or a technical article you would like including please email it to me Geoff Botterill or send them by more traditional methods via the Club Secretary. I would like to thank Colin for all his assistance during this transitional period. Without his help things could have been so much more complicated. On the 14th May the Society was given a most interesting talk titled ‘Airships over the Humber’ by Ken Deacon a member of the Barnes Wallis Trust. Ken explained that there were rigid, semi-rigid and non-rigid (‘blimp’) airships. Henri Giffard had made the first airship in 1852 and the German von Zeppelin believed in airships and by 1910 there were two German airships in regular passenger service.