A History of Java's Progress to a Field Programmable Gate Array Document (U) Title (U) Abstract (U) 4

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Download Issue

Issue October 2019 | presented by www.jaxenter.com #70 The digital magazine for enterprise developers JavaThe JDK’s hidden 13 treasures i Jakarta EE 8 Let the games begin JDK 13 Why text blocks are worth the wait OpenJFX 13 JavaFX gets its own identity © Teguh Mujiono/Shutterstock.com, Pushkin/Shutterstock.com Illustrationen: Sun Microsystems Inc., S&S Media Editorial Let’s celebrate Java – three times! It’s that time again: A new Java version is here! Java 13 Last but not least: Jakarta EE, the follow-up project of was launched as planned, six months after the release Java EE, has announced its first release under the umbrella of of Java 12, and again it has some interesting features on the Eclipse Foundation. We got hold of the executive director board. In this issue of Jax Magazine, we’ve covered them of the Eclipse Foundation, Mike Milinkovich, and asked him for you in detail. about the current status of Jakarta EE. The good news doesn’t end there, as JavaFX 13 has also been released. The UI toolkit is no longer included in the JDK Happy reading, but has adjusted its new version releases to the new Java re- lease cadence. Find out what’s new here! Hartmut Schlosser Java 13 – a deep dive into the JDK’s 3 Kubernetes as a multi-cloud 17 new features operating system Falk Sippach Patrick Arnold Index Java 13 – why text blocks are worth the wait 6 Multi-tier deployment with Ansible 21 Tim Zöller Daniel Stender Jakarta EE 8 is sprinting towards an 9 Do we need a service mesh? 28 exciting future for enterprise Java Anton Weiss Thilo Frotscher -

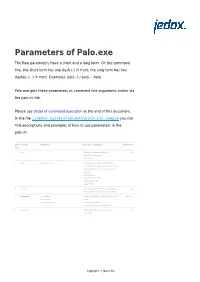

Parameters of Palo.Exe

Parameters of Palo.exe The Palo parameters have a short and a long form. On the command line, the short form has one dash (-) in front; the long form has two dashes (- -) in front. Examples: palo -? / palo – -help. Palo.exe gets these parameters as command line arguments and/or via the palo.ini file. Please see Order of command execution at the end of this document. In the file …\Jedox Suite\olap\data\palo.ini.sample you can find descriptions and examples of how to use parameters in the palo.ini. Short Long form Argument(s) Description / Example(s) Default value form ? help Displays the parameters of palo.exe. False Only for the command line. On/off switch. a admin <address> <port> Http interface with server browser and online documentation. An address can be a server name, an internet address or “” for all server internet addresses. Port is a number: admin 192.168.1.2 7777 admin localhost 7770 admin “” 7778 A auto-load Loads all databases on server start into memory True which are defined in the palo.csv. On/off switch. b cache-barrier <max number Sets the max number of cells to store in each cube 100000000 of cells to store cache. in each cube cache> cache-barrier 150000000 cache-barrier 0 (sets cache-barrier to 0). B auto-commit Commits all changes on server shutdown. True On/off switch. Copyright © Jedox AG c crypt Turns on encrypting of the database files. Newly False saved files are encrypted if this is set using the Blowfish algorithm. On/off switch. -

Advanced Programming for the Java(TM) 2 Platform

Advanced Programming for the Java(TM) 2 Platform Training Index Advanced Programming for the JavaTM 2 Platform By Calvin Austin and Monica Pawlan November 1999 [CONTENTS] [NEXT>>] [DOWNLOAD] Requires login As an experienced developer on the JavaTM platform, you undoubtedly know how fast moving and comprehensive the Early Access platform is. Its many application programming interfaces (APIs) Downloads provide a wealth of functionality for all aspects of application and system-level programming. Real-world developers never use one Bug Database or two APIs to solve a problem, but bring together key Submit a Bug functionality spanning a number of APIs. Knowing which APIs you View Database need, which parts of which APIs you need, and how the APIs work together to create the best solution can be a daunting task. Newsletters Back Issues To help you navigate the Java APIs and fast-track your project Subscribe development time, this book includes the design, development, test, and deployment phases for an enterprise-worthy auction Learning Centers application. While the example application does not cover every Articles possible programming scenario, it explores many common Bookshelf situations and the discussions leave you with a solid methodology Code Samples for designing and building your own solutions. New to Java Question of the Week This book is for developers with more than a beginning level of Quizzes understanding of writing programs in the Java programming Tech Tips language. The example application is written with the Java® 2 Tutorials platform APIs and explained in terms of functional hows and whys, so if you need help installing the Java platform, setting up your Forums environment, or getting your first application to work, you should first read a more introductory book such as Essentials of the Java Programming Language: A Hands-On Guide or The Java Tutorial. -

The Role of Multidimensional Databases in Modern Organizations

Vol.IV (LXVII) 95 - 102 Economic Insights – Trends and Challenges No. 2/2015 The Role of Multidimensional Databases in Modern Organizations Ana Tănăsescu Faculty of Economic Sciences, Petroleum-Gas University of Ploieşti, Bd. Bucureşti 39, 100680, Ploieşti, Romania e-mail: [email protected] Abstract The relational databases represent an ineffective data storage method when organizations manipulate a large amount of heterogeneous data and must realize complex analyses on these data. Thus, a new concept is required, the multidimensional database concept. In this paper the multidimensional database concept will be presented, its characteristics will be described, a comparative analysis between multidimensional databases and relational databases will be realized and a multidimensional database will be presented. This database was designed using Palo for Excel tool and can be used in order to analyse the academic staff research activity from a faculty. Keywords: multidimensional databases; multidimensional modelling; relational databases JEL Classification: C63; C81 Introduction The large amount of heterogeneous data accumulated by organizations represents one of the reasons why organizations need a technology that allows them to quickly achieve complex analyses on these data. Because the relational databases are ineffective from this point of view, a new concept is required, the multidimensional database concept. Annually, a large volume of information regarding the teaching and research activity of the academic staff from faculty departments is accumulated. The departments’ managers as well as the teaching process and research activity responsible persons must, periodically, elaborate reports, synthesizing the information accumulated in different time periods. A multidimensional database where this information will be stored is required to be designed in order to streamline their activity. -

Java (Programming Langua a (Programming Language)

Java (programming language) From Wikipedia, the free encyclopedialopedia "Java language" redirects here. For the natural language from the Indonesian island of Java, see Javanese language. Not to be confused with JavaScript. Java multi-paradigm: object-oriented, structured, imperative, Paradigm(s) functional, generic, reflective, concurrent James Gosling and Designed by Sun Microsystems Developer Oracle Corporation Appeared in 1995[1] Java Standard Edition 8 Update Stable release 5 (1.8.0_5) / April 15, 2014; 2 months ago Static, strong, safe, nominative, Typing discipline manifest Major OpenJDK, many others implementations Dialects Generic Java, Pizza Ada 83, C++, C#,[2] Eiffel,[3] Generic Java, Mesa,[4] Modula- Influenced by 3,[5] Oberon,[6] Objective-C,[7] UCSD Pascal,[8][9] Smalltalk Ada 2005, BeanShell, C#, Clojure, D, ECMAScript, Influenced Groovy, J#, JavaScript, Kotlin, PHP, Python, Scala, Seed7, Vala Implementation C and C++ language OS Cross-platform (multi-platform) GNU General Public License, License Java CommuniCommunity Process Filename .java , .class, .jar extension(s) Website For Java Developers Java Programming at Wikibooks Java is a computer programming language that is concurrent, class-based, object-oriented, and specifically designed to have as few impimplementation dependencies as possible.ble. It is intended to let application developers "write once, run ananywhere" (WORA), meaning that code that runs on one platform does not need to be recompiled to rurun on another. Java applications ns are typically compiled to bytecode (class file) that can run on anany Java virtual machine (JVM)) regardless of computer architecture. Java is, as of 2014, one of tthe most popular programming ng languages in use, particularly for client-server web applications, witwith a reported 9 million developers.[10][11] Java was originallyy developed by James Gosling at Sun Microsystems (which has since merged into Oracle Corporation) and released in 1995 as a core component of Sun Microsystems'Micros Java platform. -

Real-Time Java for Embedded Devices: the Javamen Project*

REAL-TIME JAVA FOR EMBEDDED DEVICES: THE JAVAMEN PROJECT* A. Borg, N. Audsley, A. Wellings The University of York, UK ABSTRACT: Hardware Java-specific processors have been shown to provide the performance benefits over their software counterparts that make Java a feasible environment for executing even the most computationally expensive systems. In most cases, the core of these processors is a simple stack machine on which stack operations and logic and arithmetic operations are carried out. More complex bytecodes are implemented either in microcode through a sequence of stack and memory operations or in Java and therefore through a set of bytecodes. This paper investigates the Figure 1: Three alternatives for executing Java code (take from (6)) state-of-the-art in Java processors and identifies two areas of improvement for specialising these processors timeliness as a key issue. The language therefore fails to for real-time applications. This is achieved through a allow more advanced temporal requirements of threads combination of the implementation of real-time Java to be expressed and virtual machine implementations components in hardware and by using application- may behave unpredictably in this context. For example, specific characteristics expressed at the Java level to whereas a basic thread priority can be specified, it is not drive a co-design strategy. An implementation of these required to be observed by a virtual machine and there propositions will provide a flexible Ravenscar- is no guarantee that the highest priority thread will compliant virtual machine that provides better preempt lower priority threads. In order to address this performance while still guaranteeing real-time shortcoming, two competing specifications have been requirements. -

Cost-Effective Compilation Techniques for Java Just-In-Time Compilers 3

IEICE TRANS. ??, VOL.Exx–??, NO.xx XXXX 200x 1 PAPER Cost-Effective Compilation Techniques for Java Just-in-Time Compilers Kazuyuki SHUDO†, Satoshi SEKIGUCHI†, Nonmembers, and Yoichi MURAOKA ††, Fel low SUMMARY Java Just-in-Time compilers have to satisfy a policies. number of requirements in conflict with each other. Effective execution of a generated code is not the only requirement, but 1. Ease of use as a base of researches. compilation time, memory consumption and compliance with the 2. Cost-effective development. Less labor and rela- Java Virtual Machine specification are also important. We have tively much effect. developed a Java Just-in-Time compiler keeping implementation 3. Adequate quality and performance for practical labor little. Another important objective is developing an ad- equate base of following researches which utilize this compiler. use. The proposed compilation techniques take low compilation cost and low development cost. This paper also describes optimization Compiler development involves much work on a methods implemented in the compiler, for instance, instruction parser, intermediate representations and a number of folding, exception handling with signals and code patching. optimizations. Because of it, we have to consider those key words: Runtime compilation, Java Virtual Machine, Stack human and engineering factor seriously in addition to caching, Instruction folding, Code patching technical requirements like performance. Our plan on the development of the JIT compiler was to have a prac- 1. Introduction tical compiler with work several man-month. Our an- other goal was specifically having a research base on Just-in-Time (JIT) compilers for Java bytecode have which we do following researches with less labor while to satisfy a number of requirements, which are differ- developing it with less work. -

S32 Design Studio for S32 Platform 3.4 Installation Guide

S32 Design Studio for S32 Platform 3.4 Installation Guide Document Number: S32DSIG Rev. 1.0, 12/2020 Contents System Requirements......................................................................................................................3 Installation prerequisites for Linux platforms.............................................................................5 Downloading S32DS 3.4................................................................................................................12 Downloading the S32DS 3.4 installer................................................................................................................12 Obtaining the activation code.............................................................................................................................12 Installing S32DS 3.4......................................................................................................................14 Debian 8 post-installation settings..................................................................................................................... 20 Installing product updates and packages................................................................................... 23 Installing Synopsys tools...............................................................................................................25 Installing VP Explorer........................................................................................................................................25 Post-installation settings.................................................................................................................................... -

Picojava-II™ Programmer's Reference Manual

picoJava-II™ Programmer’s Reference Manual Sun Microsystems, Inc. 901 San Antonio Road Palo Alto, CA 94303 USA 650 960-1300 Part No.: 805-2800-06 March 1999 Copyright 1999 Sun Microsystems, Inc. 901 San Antonio Road, Palo Alto, California 94303 U.S.A. All rights reserved. The contents of this document are subject to the current version of the Sun Community Source License, picoJava Core (“the License”). You may not use this document except in compliance with the License. You may obtain a copy of the License by searching for “Sun Community Source License” on the World Wide Web at http://www.sun.com. See the License for the rights, obligations, and limitations governing use of the contents of this document. Sun, Sun Microsystems, the Sun logo and all Sun-based trademarks and logos, Java, picoJava, and all Java-based trademarks and logos are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. DOCUMENTATION IS PROVIDED “AS IS” AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON- INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID. THIS PUBLICATION COULD INCLUDE TECHNICAL INACCURACIES OR TYPOGRAPHICAL ERRORS. CHANGES ARE PERIODICALLY ADDED TO THE INFORMATION HEREIN; THESE CHANGES WILL BE INCORPORATED IN NEW EDITIONS OF THE PUBLICATION. -

Extending a J2EE™ Server with Dynamic and Flexible Resource Management

Extending a J2EE™ Server with Dynamic and Flexible Resource Management 1 1 2 1 Mick Jordan , Grzegorz Czajkowski , Kirill Kouklinski , and Glenn Skinner 1 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, CA 95054, USA {firstname.lastname}@sun.com 2School of Computer Science, University of Waterloo, Waterloo, ON N2L 3G1, Canada [email protected] Abstract. The Java™ 2 Platform, Enterprise Edition (J2EE™) is the standard platform for hosting enterprise applications written in the Java programming language. A single J2EE server can support multiple applications much like a traditional operating system, but performance levels can be difficult to control, due to the absence of resource management facilities in the Java platform. The Resource Management (RM) interface addresses this problem by providing a flexible and extensible framework for managing resources that is applicable across a broad spectrum, from low-level resources like CPU time to higherlevel resources such as database connections. RM has been implemented in the Multi-tasking Virtual Machine (MVM), a scalable operating environment for multiple applications based on the concept of isolated computations. This paper describes the application of MVM and RM to the management of resources in a J2EE Server and shows that application performance can be controlled flexibly and easily with low overhead and minimal intrusion. 1 Introduction The Java™ 2 Platform, Enterprise Edition (J2EE™) [1] is the standard server-side environment for developing enterprise applications in the Java programming lan- guage. J2EE is itself layered on the Java™ 2 Platform, Standard Edition (J2SE™) [2]. In many respects the combination of the J2EE and J2SE platforms subsumes the un- derlying operating system (OS). -

The Cedar Programming Environment: a Midterm Report and Examination

The Cedar Programming Environment: A Midterm Report and Examination Warren Teitelman The Cedar Programming Environment: A Midterm Report and Examination Warren Teitelman t CSL-83-11 June 1984 [P83-00012] © Copyright 1984 Xerox Corporation. All rights reserved. CR Categories and Subject Descriptors: D.2_6 [Software Engineering]: Programming environments. Additional Keywords and Phrases: integrated programming environment, experimental programming, display oriented user interface, strongly typed programming language environment, personal computing. t The author's present address is: Sun Microsystems, Inc., 2550 Garcia Avenue, Mountain View, Ca. 94043. The work described here was performed while employed by Xerox Corporation. XEROX Xerox Corporation Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, California 94304 1 Abstract: This collection of papers comprises a report on Cedar, a state-of-the-art programming system. Cedar combines in a single integrated environment: high-quality graphics, a sophisticated editor and document preparation facility, and a variety of tools for the programmer to use in the construction and debugging of his programs. The Cedar Programming Language is a strongly-typed, compiler-oriented language of the Pascal family. What is especially interesting about the Ce~ar project is that it is one of the few examples where an interactive, experimental programming environment has been built for this kind of language. In the past, such environments have been confined to dynamically typed languages like Lisp and Smalltalk. The first paper, "The Roots of Cedar," describes the conditions in 1978 in the Xerox Palo Alto Research Center's Computer Science Laboratory that led us to embark on the Cedar project and helped to define its objectives and goals. -

Resume Emmanuel Puybaret / Java Developer

Emmanuel PUYBARET 52, married, two children 35, rue de Chambéry French native, fluent in English 75015 PARIS FRANCE Tel +33 1 58 45 28 27 Email [email protected] EDUCATION 1992-1993 Master's degree in INDUSTRIAL DESIGN/PRODUCT DESIGN, U.T.C. (University of Technology of Compiègne). 1985-1991 AERONAUTICS ENGINEER, E.S.T.A.C.A. (Graduate School of Aeronautics Engineering and Cars Construction). 1988-1990 BS in COMPUTER SCIENCE, University of Paris 6 (specialization in 2D/3D graphics, Artificial Intelligence, signal processing). COMPUTER SKILLS Systems Windows XP/7/8/10, Mac OS X, Linux. Languages Java, JavaScript, HTML, XML, SQL, C, C++, C#, Objective C, UML. Java API J2SE / Java SE: AWT, Swing, Java 2D, JavaSound, JDBC, SAX, DOM, JNI, multi-threading. J2EE / Java EE: Servlet, JSP, JSF, JPA, JavaMail, JMS, EJB. Other API: Struts, Hibernate, Ant, JUnit/TestNG, Abbot, FEST, SWT/JFace, Java 3D, WebGL. WORK EXPERIENCE Since 1999 JAVA ENGINEER AND TRAINER, freelancer, eTeks. References: 1999-2019 • eTeks: Author of the web site http://www.eteks.com (more than 10,000 visits per month): 5 months o Writing in French of the tutorial From C/C++ to Java and programming tips. 8 years o Development of Java products available under GNU GPL Open Source license: Sweet Home 3D interior design application, Jeks Swing spreadsheet, PJA Toolkit graphical library. 1 month o Development of the navigation applet TeksMenu sold to ten web sites. 1999-2018 23 months • AFTI, BSPP, CAI, EFREI, ENSEA, ESIC, ESIGETEL, GRETA, ib, Infotel, Intrabases, ITIN, LTM, SmartFutur, SofTeam, Sun Educational: Trainings in Java, JDBC, JSP, Swing, Java 2D, Java 3D, C++.