Tia Systems Bulletin

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Problems in Fibre Optic Communication in the Communication Systems of Vehicles

TEKA Kom. Mot. i Energ. Roln. – OL PAN, 2011, 11, 363–372 THE PROBLEMS IN FIBRE OPTIC COMMUNICATION IN THE COMMUNICATION SYSTEMS OF VEHICLES Sumorek Andrzej, Buczaj Marcin Department of Computer and Electrical Engineering, Lublin University of Technology, Poland Summary. The diversifi cation of technical solutions occurred as a result of almost thirty years of evolution of the communication systems between the mechatronic systems in motor vehicles. The vehicles are equipped with the conventional cable connections between the switches and actuators as well as with advanced data exchange networks. These networks show more and more similarities to computer networks. They are the new solutions; even their classifi cation has been created a few years ago (class D). Therefore the personnel engaged in the scope of functional programming and vehicles servicing encounter the problems associated with networks operation. The purpose of the article is to present the principles of functioning of the basic networks with the medium in the form of an optical fi bre. Particular emphasis has been placed on the detection of failures consisting in the damage of communication node and optical fi bre. Key words: Media Oriented Systems Transport, Domestic Digital Bus. INTRODUCTION The systematics associated with networks classifi cation presented in the year 1994 contained 3 types of networks. Such systematics was also presented in 2007 in literature in 2007 [12]. This approach has been established as a result of the standardization introduced by SAE J1850 [5, 10]. Three classes of communication systems have been specifi ed in SAE J1850. The applications group associated with bus throughput is used as the criterion of subdivision. -

SAE J1587 (2002 Standard).Pdf

SURFACE REV. VEHICLE J1587 FEB2002 RECOMMENDED Issued 1988-01 400 Commonwealth Drive, Warrendale, PA 15096-0001 PRACTICE Revised 2002-02 Superseding J1587 JUL1998 Electronic Data Interchange Between Microcomputer Systems in Heavy-Duty Vehicle Applications 1. Scope—This SAE Recommended Practice defines a document for the format of messages and data that is of general value to modules on the data communications link. Included are field descriptions, size, scale, internal data representation, and position within a message. This document also describes guidelines for the frequency of and circumstances in which messages are transmitted. In order to promote compatibility among all aspects of electronic data used in heavy-duty applications, it is the intention of the SAE Truck and Bus Low Speed Communications Network Subcommittee (formerly Data Format Subcommittee) (in conjunction with other industry groups) to develop recommended message formats for: a. Vehicle and Component Information—This includes all information that pertains to the operation of the vehicle and its components (such as performance, maintenance, and diagnostic data). b. Routing and Scheduling Information—Information related to the planned or actual route of the vehicle. It includes current vehicle location (for example, geographical coordinates) and estimated time of arrival. c. Driver Information—Information related to driver activity. Includes driver identification, logs, (for example, DOT), driver expenses, performance, status, and payroll data. d. Freight Information—Provides data associated with cargo being shipped, picked up, or delivered. Includes freight status, overage, shortage and damage reporting, billing and invoice information as well as customer and consignee data. This document represents the recommended formats for basic vehicle and component identification and performance data. -

Body Builder Connectors, Schematic

BODY BUILDER INSTRUCTIONS Mack Trucks Electrical Wiring and Connections CHU, CXU, GU, TD, MRU, LR Section 3 Introduction This information provides design and function, specification and procedure details for Electrical Wiring and Connections for MACK vehicles. Note: For information on mDrive PTO installation and wiring see Section 9 PTO Installation, mDrive. Note: For information on PTO parameter programming see Section 9 PTO Parameter Programming. Unless stated otherwise, following a recommendation listed in this manual does not automatically guarantee compliance with applicable government regulations. Compliance with applicable government regulations is your responsibility as the party making the additions/modifications. Please be advised that the MACK Trucks, Inc. vehicle warranty does not apply to any MACK vehicle that has been modified in any way, which in MACK's judgment might affect the vehicles stability or reliability. Contents • “Abbreviations”, page 3 • “General Wiring Definitions”, page 4 • “Routing and Clipping Guidelines”, page 5 • “Body Builder Connectors, Schematic Examples”, page 17 • “Remote Start n Stop”, page 23 • “Remote Engine Stop”, page 24 • “Adding Auxiliary Accelerator Pedal”, page 25 • “BodyLink III”, page 26 • “Auxiliary Switch Locations (Cab)”, page 30 • “Power Connections”, page 31 • “Control Link II”, page 37 • “LR Workbrake”, page 50 Mack Body Builder Instructions CHU, CXU, GU, TD, MRU, LR USA139448393 Date 9.2017 Page 1 (94) All Rights Reserved • “Wiring J1939”, page 52 • “9-pin Diagnostic Connector”, -

Study of an Error in Engine ECU Data Collected for In-Use Emissions Testing and Development and Evaluation of a Corrective Procedure

Graduate Theses, Dissertations, and Problem Reports 2007 Study of an error in engine ECU data collected for in-use emissions testing and development and evaluation of a corrective procedure Petr Sindler West Virginia University Follow this and additional works at: https://researchrepository.wvu.edu/etd Recommended Citation Sindler, Petr, "Study of an error in engine ECU data collected for in-use emissions testing and development and evaluation of a corrective procedure" (2007). Graduate Theses, Dissertations, and Problem Reports. 1840. https://researchrepository.wvu.edu/etd/1840 This Thesis is protected by copyright and/or related rights. It has been brought to you by the The Research Repository @ WVU with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository @ WVU. For more information, please contact [email protected]. Study of an Error in Engine ECU Data Collected for In-Use Emissions Testing and Development and Evaluation of a Corrective Procedure Petr Sindler Thesis submitted to the College of Engineering and Mineral Resources at West Virginia University in partial fulfillment of the requirements for the degree of Master of Science in Mechanical Engineering Mridul Gautam, Ph.D., Chair Gregory J. -

SAE International® PROGRESS in TECHNOLOGY SERIES Downloaded from SAE International by Eric Anderson, Thursday, September 10, 2015

Downloaded from SAE International by Eric Anderson, Thursday, September 10, 2015 Connectivity and the Mobility Industry Edited by Dr. Andrew Brown, Jr. SAE International® PROGRESS IN TECHNOLOGY SERIES Downloaded from SAE International by Eric Anderson, Thursday, September 10, 2015 Connectivity and the Mobility Industry Downloaded from SAE International by Eric Anderson, Thursday, September 10, 2015 Other SAE books of interest: Green Technologies and the Mobility Industry By Dr. Andrew Brown, Jr. (Product Code: PT-146) Active Safety and the Mobility Industry By Dr. Andrew Brown, Jr. (Product Code: PT-147) Automotive 2030 – North America By Bruce Morey (Product Code: T-127) Multiplexed Networks for Embedded Systems By Dominique Paret (Product Code: R-385) For more information or to order a book, contact SAE International at 400 Commonwealth Drive, Warrendale, PA 15096-0001, USA phone 877-606-7323 (U.S. and Canada) or 724-776-4970 (outside U.S. and Canada); fax 724-776-0790; e-mail [email protected]; website http://store.sae.org. Downloaded from SAE International by Eric Anderson, Thursday, September 10, 2015 Connectivity and the Mobility Industry By Dr. Andrew Brown, Jr. Warrendale, Pennsylvania, USA Copyright © 2011 SAE International. eISBN: 978-0-7680-7461-1 Downloaded from SAE International by Eric Anderson, Thursday, September 10, 2015 400 Commonwealth Drive Warrendale, PA 15096-0001 USA E-mail: [email protected] Phone: 877-606-7323 (inside USA and Canada) 724-776-4970 (outside USA) Fax: 724-776-0790 Copyright © 2011 SAE International. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, distributed, or transmitted, in any form or by any means without the prior written permission of SAE. -

Surface Vehicle Standard

SURFACE J1939-01 VEHICLE Issued 2000-09 STANDARD Submitted for recognition as an American National Standard Recommended Practice for Control and Communications Network for On-Highway Equipment Foreword—This series of SAE Recommended Practices have been developed by the Truck and Bus Control and Communications Network Subcommittee of the Truck and Bus Electrical and Electronics Committee. The objectives of the subcommittee are to develop information reports, recommended practices and standards concerned with the requirements design and usage of devices which transmit electrical signals and control information among vehicle components. The usage of these recommended practices is not limited to truck and bus applications, other applications may utilize them as long as they adhere to the recommended practices listed herein. These SAE Recommended Practices are intended as a guide toward standard practice and are subject to change so as to keep pace with experience and technical advances. As described in the parent document, SAE J1939, there are a minimum of five documents required to fully define a complete version of this network. This particular document, SAE J1939-01, identifies one such complete network by specifying the particular set of SAE J1939 documents which define the Truck and Bus Control and Communications Vehicle Network as it applies to on-highway equipment. Table of Contents 1 Scope ......................................................................................................................................2 1.1 Degree -

Extracting and Mapping Industry 4.0 Technologies Using Wikipedia

Computers in Industry 100 (2018) 244–257 Contents lists available at ScienceDirect Computers in Industry journal homepage: www.elsevier.com/locate/compind Extracting and mapping industry 4.0 technologies using wikipedia T ⁎ Filippo Chiarelloa, , Leonello Trivellib, Andrea Bonaccorsia, Gualtiero Fantonic a Department of Energy, Systems, Territory and Construction Engineering, University of Pisa, Largo Lucio Lazzarino, 2, 56126 Pisa, Italy b Department of Economics and Management, University of Pisa, Via Cosimo Ridolfi, 10, 56124 Pisa, Italy c Department of Mechanical, Nuclear and Production Engineering, University of Pisa, Largo Lucio Lazzarino, 2, 56126 Pisa, Italy ARTICLE INFO ABSTRACT Keywords: The explosion of the interest in the industry 4.0 generated a hype on both academia and business: the former is Industry 4.0 attracted for the opportunities given by the emergence of such a new field, the latter is pulled by incentives and Digital industry national investment plans. The Industry 4.0 technological field is not new but it is highly heterogeneous (actually Industrial IoT it is the aggregation point of more than 30 different fields of the technology). For this reason, many stakeholders Big data feel uncomfortable since they do not master the whole set of technologies, they manifested a lack of knowledge Digital currency and problems of communication with other domains. Programming languages Computing Actually such problem is twofold, on one side a common vocabulary that helps domain experts to have a Embedded systems mutual understanding is missing Riel et al. [1], on the other side, an overall standardization effort would be IoT beneficial to integrate existing terminologies in a reference architecture for the Industry 4.0 paradigm Smit et al. -

Selection Guide for Automotive & Industrial Fanless Box-PC

1/127 PDF Online Selection Guide Stand vom 02.10.2021 - 23:17:17 Bitte laden Sie sich bei Bedarf hier eine aktualisierte Fassung dieses Dokuments herunter! 180 von 180 Artikel aus dem Bereich Automotive & Industrial Box-PC wurden für das PDF ausgewählt. Selection Guide Automotive & Industrial Fanless Box-PC 1. Automotive Box-PC / Car-PC 3 2. KI-Automotive Box-PC 31 3. Railway Box-PC 51 4. Industrial Box-PC / IoT Gateways 61 5. Factory Automation Box-PC 95 6. Digital Signage Box-PC 107 7. Video Surveillance 119 8. Zubehör für Box-PC 127 DELTA COMPONENTS ...we make the difference! 3/127 Automotive Box-PC PDF Online Selection Guide Stand vom 02.10.2021 - 23:17:17 Bitte laden Sie sich bei Bedarf hier eine aktualisierte Fassung dieses Dokuments herunter! 41 von 41 Artikel aus dem Bereich Automotive Box-PC wurden für das PDF ausgewählt. Advanced Telematics Computer Advanced Telematics Computer Advanced Telematics Computer 8010-7AF/7DF 8010-7A 8010-7B Cooling System Swappable fan kit (externally removable fans) Fanless Fanless Mounting System Wall Mount, DIN Rail Wall Mount, DIN Rail Wall Mount, DIN Rail CPU Intel® Core i7-8700T Coffee Lake-S, 6-core, Intel® Core i7-8700T Coffee Lake-S, 6-core, Intel® Core i7-8700T Coffee Lake-S, 6-core, 2.4GHz 2.4GHz 2.4GHz Chipset Intel® Q370 platform controller hub Intel® Q370 platform controller hub Intel® Q370 platform controller hub Watchdog Timer - - - Basic Equipment 8GB 8GB 8GB Maximum Equipment 64G (for two channels) 64G (for two channels) 64G (for two channels) DRAM - - - SDRAM - - - DIMM / MemorySocket -

Cybersecurity Research Considerations for Heavy Vehicles

DOT HS 812 636 December 2018 Cybersecurity Research Considerations for Heavy Vehicles Disclaimer This publication is distributed by the U.S. Department of Transportation, National Highway Traffic Safety Administration, in the interest of information exchange. The opinions, findings, and conclusions expressed in this publication are those of the authors and not necessarily those of the Department of Transportation or the National Highway Traffic Safety Administration. The United States Government assumes no liability for its contents or use thereof. If trade or manufacturers’ names are mentioned, it is only because they are considered essential to the object of the publication and should not be construed as an endorsement. The United States Gov- ernment does not endorse products or manufacturers. Suggested APA Format Citation: Stachowski, S., Bielawski, R., & Weimerskirch, A. (2018, December). Cybersecurity research considerations for heavy vehicles (Report No. DOT HS 812 636). Washington, DC: National Highway Traffic Safety Administration. 1. Report No. 2. Government Accession No. 3. Recipient's Catalog No. DOT HS 812 636 4. Title and Subtitle 5. Report Date Cybersecurity Research Considerations for Heavy Vehicles December 2018 6. Performing Organization Code 7. Authors 8. Performing Organization Report No. Stephen Stachowski, P.E. (UMTRI), Russ Bielawski (UMTRI), André Weimerskirch 9. Performing Organization Name and Address 10. Work Unit No. (TRAIS) University of Michigan Transportation Research Institute 2901 Baxter Rd Ann Arbor, MI 48109 11. Contract or Grant No. DTNH22-15-R-00101, a Vehicle Electronics Systems Safety IDIQ 12. Sponsoring Agency Name and Address 13. Type of Report and Period Covered National Highway Traffic Safety Administration Final Report 1200 New Jersey Avenue SE. -

SAMTEC Automotive Software & Electronics

SAMTEC Automotive Software & Electronics PRODUCT CATALOG 2016 AUTOMOTIVE www.samtec.de PUBLICATION DETAILS 2 CONTACT samtec automotive software & electronics gmbh Einhornstr. 10, D-72138 Kirchentellinsfurt - Germany Phone +49-7121-9937-0 Telefax +49-7121-9937-177 Internet www.samtec.de E-mail [email protected] DISCLAIMER The information contained in this catalog corresponds to the technical status at the time of printing and is passed on with the best of our knowledge. The information in this catalog is in no event a basis for warranty claims or contractual agreements concerning the described products and may especially not be deemed as warranty concerning the quality and durability pursuant to Sec. 443 German Civil Code. samtec automotive software & electronics gmbh reserves the right to make any alterations to this catalog without prior notice. The actual design of products may deviate from the information contained in the catalog if technical alterations and product improvements so require. In any cases, only the proposal made by samtec automotive software & electronics gmbh for a concrete application or product will be binding. All mentioned product names are either registered or unregistered trademarks of their respective owners. Errors and omissions excepted. This catalog has been made available to our customers and interested parties free of charge. It may not, in part or in its entirety, be reproduced in any form without our prior consent. All rights reserved. LEGAL NOTICE samtec automotive software & electronics gmbh Managing directors: René von Stillfried, Dr. Wolfgang Trier Registered office: Kirchentellinsfurt Date: March 2016 Commercial register: Stuttgart, HRB 224968 PREFACE Dear readers, 3 Many of you already know us! You deploy electronic control units, we provide you with the diagnostic solutions. -

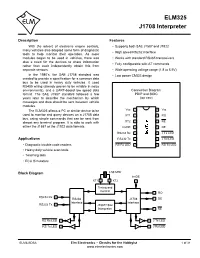

ELM325 J1708 Interpreter

ELM325 J1708 Interpreter Description Features With the advent of electronic engine controls, • Supports both SAE J1587 and J1922 many vehicles also adopted some form of diagnostic • High speed RS232 interface tools to help monitor their operation. As more modules began to be used in vehicles, there was • Works with standard RS485 transceivers also a need for the devices to share information • Fully configurable with AT commands rather than each independently obtain this from separate sensors. • Wide operating voltage range (1.8 to 5.5V) In the 1980’s, the SAE J1708 standard was • Low power CMOS design created to provide a specification for a common data bus to be used in heavy duty vehicles. It used RS485 wiring (already proven to be reliable in noisy environments), and a UART-based low speed data Connection Diagram format. The SAE J1587 standard followed a few PDIP and SOIC years later to describe the mechanism by which (top view) messages and data should be sent between vehicle modules. The ELM325 allows a PC or similar device to be VDD 1 14 VSS used to monitor and query devices on a J1708 data XT1 2 13 RO bus, using simple commands that can be sent from almost any terminal program. It is able to work with XT2 3 12 RE either the J1587 or the J1922 data formats. InvDE 4 11 DE RS232 Rx 5 10 J Tx LED Applications RS232 Tx 6 9 J Rx LED • Diagnostic trouble code readers RS Rx LED 7 8 RS Tx LED • Heavy duty vehicle scan tools • Teaching aids • ECU Simulators Block Diagram 3.58 MHz InvDE XT12 3 XT2 4 Timing and Control 13 RO RS232 Rx 5 RS232 J1708 11 DE Interface Interface RS232 Tx 6 J1587/1922 Interpreter 12 RE RS Rx LED 7 10 J Tx LED RS Tx LED 8 9 J Rx LED ELM325DSA Elm Electronics – Circuits for the Hobbyist 1 of 31 www.elmelectronics.com ELM325 Contents Electrical Information Copyright and Disclaimer.............................................................2 Pin Descriptions.......................................................................... -

RVT-7 User's Manual

RVT-7 7” Rugged Android Vehicle Display Terminal User’s Manual Version 1.0.0 1 Revision History Version Release Time Description 1.0 2019.06 Initial Release Modify chaper 4: docking station using 1.1 2019.07 instruction 1.2 2019.08 Modify Chaper5: Accessories 1.3 2019.10 Add “3.3.3 GPIO specification” Disclaimer The information in this document is subject to change without prior notice in order to improve the reliability, design and function. It does not represent a commitment on the part of the manufacturer. Under no circumstances will the manufacturer be liable for any direct, indirect, special, incidental, or consequential damages arising from the use or inability to use the product or documentation, even if advised of the possibility of such damages. About This Manual This user’s manual provides the general information and installation instructions for the product. The manual is meant for the experienced users and integrators with hardware knowledge of personal computers. If you are not sure about any description in this manual, consult your vendor before further handling. We recommend that you keep one copy of this manual for the quick reference for any necessary maintenance in the future. Thank you for choosing Seatronx products. 2 CONTENT 1.1 Product Highlights .............................................................................................................. 7 1.2 Parts of the Device .............................................................................................................. 7 1.3 Extended Cable Definition