The Commodore PET Revealed

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Small Computer Monitor User Guide

SmallSmall ComputerComputer MonitorMonitor UserUser GuideGuide Monitor version 1.0 for the Z80 CPU Software and Documentation by Stephen C Cousins Edition 1.0.0 CONTENTS OVERVIEW................................................................................................................4 Conventions....................................................................................................... 4 Serial port.......................................................................................................... 5 LiNC80 systems.................................................................................................. 5 RC2014 systems................................................................................................. 6 COMMANDS..............................................................................................................7 ? or Help............................................................................................................ 7 API function call................................................................................................. 8 Assemble instructions...................................................................................... 10 Baud rate setting............................................................................................. 13 Breakpoint set or clear..................................................................................... 13 Console........................................................................................................... -

COMMODORE HOTLINE - What's New on the Commodore Scene 1 4

co mmodore COMPUTING international December 1SS2 £1.00 U S A S32.5Q MICROS FOR OPTICIANS CBM 64 MEMORY MAPS NEW BEGINNERS GUIDE WORD PROCESSING LIGHT PEN VICAID VIC Two sets of Fabulous Utilities in one! LIG H TPEN PROGRAMMERS TOOLKIT Gives extra commands: Auto, Number, Help, Delete, Change, DAMS PRICE T race, Step, LightPen, Breaketc. and ONLY MACHINE CODE MONITOR Gives Save, Memory Display, Load, Verify etc. Similar to TIM on PET. + VAT Examine the VICS ROM £ 1 7 .3 5 Needs DAMS RAM/ROM board or similar FOR PET £ 1 9 .9 5 vat 12" SCREEN £ 1 9 .9 5 + VAT VICMON RAM ’N ROM THE ULTIMATE BOARD PROGRAMING AID FOR THE VIC 3K RAM In Hires area. Also space for Full machine code VICAID and package with: VICMON Assembler, Dissassembler, programming aids Fill, Re-locate, Identify, Exchange, Compare, Printing, Dissassembler etc., etc. Needs DAMS RAM/ROM board or similar +VAT £ 1 9 .9 5 + VAT (Includes Cover) BUY THE 3K RAM N ROM BOARD WITH VICAID AND VICMON WITH MACHINE CODE MANUAL (WORTH £5.00) FROM MOS TECHNOLOGY FOR ONLY £67.85 + VAT AND GET A FREE VIC LIGHT PEN (WORTH £17.35) VIC REFERENCE GUIDE R.R.P. £14.95 DAMS PRICE £14.50 VIC STARTER KIT VIC 20 C2N Cassette Deck, 10 Blank Cassettes, User Manual, Vic Programmers Reference Guide, ANTIGLARE 1 Joystick. Worth£238.30 ONLY«^0 4 m A A SCREENS FOR PET L Z 1 4 . U U +v a t 40 Column (VAT INCL. PRICE = £244.62) £17.95 80 Column OR VIC 20 With free 3K RAM pack or £19.95 Super Cartridge Game ONLY £173.83 ALL PRICES PLUS VAT VDU VIEW THRU + VAT ACCESS & DAMS BUSINESS COMPUTERS LTD. -

How to Get Hundreds of Free Programs for the VIC·20 And

Second Class Mail Registration no. 5918, Shelburne, Ontario The INDEPENDENT Commodore Users' Magazine No. 20 JUNE 1983 ~'),~() VIC, PET Making Games, Finding Games, and Playing Games. C-64 GAMES Is It Good or Bad? How to get Hundreds of Free Programs for the VIC·20 and Commodore 64 see page 2 10610 BAYVIEW (Bayview Plaza) RICHMOND HILL, ONTARIO, CANADA L4C 3N8 (416) 884-4165 C64-LINK' The Smart 64 RTC Call or write payments Serial by VISA, Cartridge Audio 1/0 MASTERCARD Expansion Slot Switch RF Video Port Cassette Port Users Port or BANK TRANSFER. Mail orders also by certified check, etc. IEEE Disks (2031) (4040) Tape VIC Modem (8050) (8250) (9090) lEE E Printers 1541 Drive or VL3 Cable Many more 64s And V L 16 (4022) (8023) to Parallel 1525 Printer (8300) Printer etc. or 1515 Printer Wf fl (future) lEE E to Par a II e I IEEE to Serial or VL4 Cable Interface Cartridge Interface to Standard Parallel M other Board True Serial Modem Devices Devices Give These Expanded Capabilities To Your 64 * The ability to transfer data from any type of device to another (IEEE, Serial, Parallel) ,it I * BASIC 4.0 which allows you to run more PET BASIC programs and gives you extended disk and 110 commands. I And * The ability to have several 64s on line together - sharing common IEEE PAL © devices such as disks or printers with Spooling Capability. * Built-in machine language monitor I * A built-in terminal or modem program which allows the system to communi Spooling Other cate through a modem to many bulletin board systems and other computer mainframes. -

The Commodore 64 Survival Manual

THE COMMODORE 64 SURVIVAL MANUAL Bantam Books of Related Interest Ask your bookseller for the books you have missed THE COMPLETE BUYER’S GUIDE TO PERSONAL COMPUTERS by Tim Hartnell and Stan Veit THE FRIENDLY COMPUTER BOOK: A SIMPLE GUIDE FOR ADULTS by Gene Brown HOW TO GET THE MOST OUT OF COMPUSERVE by Charles Bowen and Dave Peyton THE ILLUSTRATED COMPUTER DICTIONARY by The Editors of Consumer Guide® MASTERING YOUR TIMEX SINCLAIR 1000/1500™ PERSONAL COMPUTER by Tim Hartnell and Dilwyn Jones THE COMMODORE 64 SURVIVAL MANUAL Winn L. Rosch Illustrations by Steve Henry A Hard/Soft Press Book BANTAM BOOKS TORONTO • NEW YORK • LONDON • SYDNEY • AUCKLAND THE COMMODORE 64 SURVIVAL MANUAL A Bantam Book I August 1984 Sprite and sound assistance: Michael Callery All rights reserved. Copyright © 1984 Hard!Soft Inc. Cover art copyright © 1984 by Bantam Books, Inc. This book may not be reproduced in whole or in part, by mimeograph or any other means, without permission. For information address: Bantam Books, Inc. ISBN 0-553-34127-8 Published simultaneously in the United States and Canada Bantam Books are published by Bantam Books, Inc. Its trademark, consisting of the words "Bantam Books” and the portrayal of a rooster, is Registered in U.S. Patent and Trademark Office and in other countries. Marca Registrada. Bantam Books, Inc., 666 Fifth Avenue, New York, New York 10103. PRINTED IN THE UNITED STATES OF AMERICA HL 0987654321 To Granny TABLEOFCONTENTS 1 INTRODUCING THE COMMODORE 64 1 Computer basics made easy. Peripherals, applications, shopping notes, and general hints and tips. 2 BEATING THE SYSTEM______________________ 16 What’s inside your C-64 and how does it work? A fasci nating look at monitors, printers, plotters, storage media, modems, paddles, joysticks, and other devices. -

©Beebugsoft 19984

EXMON II Extended machine code monitor supplied on Eprom for the BBC Micro and Electron BEEBUG SOFT BEEBUG SOFT BEEBUG SOFT BEEBUG SOFT EXMON II THIRD GENERATION MACHINE CODE MONITOR For the BBC MICRO & ELECTRON ©BEEBUGSOFT 1984 P.O. Box 50, St. Albans, Herts. All rights reserved. No part of this product may be reproduced in whole or part by any means without written permission of the publisher. Unauthorised hiring, renting, loaning, public performance or broadcasting of this product or its constituent parts is prohibited. While every care is taken, the publisher cannot be held responsible for any errors in this product. 1 EXMON II THIRD GENERATION MACHINE CODE MONITOR For the BBC MICRO &ELECTRON by Mark Tilley CONTENTS 1. Introduction 3 2. Starting Instructions 5 3. General Overview 6 4. Memory Editor 11 5. Simple Commands 13 6. Relocation 15 7. Debugging Commands 17 8. Single-Stepping 19 9. Trace Options 20 10. Dual Screen Operation 21 Appendix (i) Examples 24 Appendix (ii) Assembling from tape/disc 26 Appendix (iii) Electron Notes 27 Appendix (iv) Command Summary 28 2 3 1. INTRODUCTION EXMON II is an extremely sophisticated third generation machine code monitor for the BBC Micro and Electron. It incorporates a number of advanced features not to be found on EXMON I (i.e. the first release of EXMON), while omitting only one EXMON I feature -- the on-screen Help facility. This had to be sacrificed because of lack of space, and is replaced by a command summary card. Electron users should consult appendix (iii) at this point. -

A Commodore PET-2001 Clone

A Commodore PET-2001 clone Built in 2018 using current-production parts. Glen Kleinschmidt www.glensstuff.com November 2018 Introduction This project had its genesis in 2017 when, reading on-line about old computers, I stumbled upon the fact that a variant of the PET-2001’s original brain, now more than 40 years old, is still being produced. The venerable MOS Technology 6502 microprocessor, in its modern guise, is the W65C02S, supplied by fabless semiconductor company Western Design Center, Inc and distributed by Mouser Electronics. WDC specialise in 65xx-brand microprocessor technology and additionally supply the W65C21N and W65C22N, which are, for all practical purposes here, current production, drop-in replacements for the PET’s original 6520 “PIA” and 6522 “VIA” chips. This clone is therefore not another FPGA port or an emulator running on a Raspberry Pi, but a functional replica of the original computer in the traditional hardware sense. Nor is it a part- for-part duplication of the original circuitry, but a complete re-design using contemporary discrete CMOS logic and memory devices, with some additional features thrown in for good measure. At the time or writing every component used in this project is a current-production part. 74HC(T) CMOS family logic almost entirely displaces the original LS TTL logic and great simplifications were made by using modern memory devices. Additionally, although for all practical purposes here the W65C02 is, functionally, entirely equivalent to the original 6502, it is not a direct drop-in replacement. It has slightly different pin functions, different, more stringent timing requirements due to its ability to run several times faster than the original NMOS 6502 and it is a CMOS part with CMOS-level, rather than TTL-level compatible I/O thresholds. -

Commodore Enters in the Play “Business Is War, I Don't Believe in Compromising, I Believe in Winning” - Jack Tramiel

Commodore enters in the play “Business is war, I don't believe in compromising, I believe in winning” - Jack_Tramiel Commodore_International Logo Commodore International was an American home computer and electronics manufacturer founded by Jack Tramiel. Commodore International (CI), along with its subsidiary Commodore Business Machines (CBM), participated in the development of the home personal computer industry in the 1970s and 1980s. CBM developed and marketed the world's best-selling desktop computer, the Commodore 64 (1982), and released its Amiga computer line in July 1985. With quarterly sales ending 1983 of $49 million (equivalent to $106 million in 2018), Commodore was one of the world's largest personal computer manufacturers. Commodore: the beginnings The company that would become Commodore Business Machines, Inc. was founded in 1954 in Toronto as the Commodore Portable Typewriter Company by Polish-Jewish immigrant and Auschwitz survivor Jack Tramiel. By the late 1950s a wave of Japanese machines forced most North American typewriter companies to cease business, but Tramiel instead turned to adding machines. In 1955, the company was formally incorporated as Commodore Business Machines, Inc. (CBM) in Canada. In 1962 Commodore went public on the New York Stock Exchange (NYSE), under the name of Commodore International Limited. Commodore soon had a profitable calculator line and was one of the more popular brands in the early 1970s, producing both consumer as well as scientific/programmable calculators. However, in 1975, Texas Instruments, the main supplier of calculator parts, entered the market directly and put out a line of machines priced at less than Commodore's cost for the parts. -

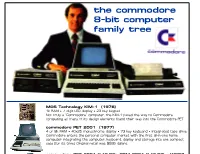

The Commodore 8-Bit Computer Family Tree

the commodore 8-bit computer family tree MOS Technology KIM-1 (1976) 1k RAM • 7 digit LED display • 23 key keypad Not truly a “Commodore” computer, the KIM-1 paved the way to Commodore computing as many of its design elements found their way into the Commodore PET commodore PET 2001 (1977) 4 or 8k RAM • 40x25 monochrome display • 73 key keyboard • Integrated tape drive Commodore enters the personal computer market with the first all-in-one home computer integrating the computer, keyboard, display and storage into one compact case (for its time). Original retail was $595 dollars. commodore PET 2001-8,16,32n CBM 2001-8,16,32b (1978) commodore PET 2001-8,16,32n CBM 2001-8,16,32b (1978) 8, 16 or 32k RAM • 40x25 monochrome display • 74[n]/73[b] key keyboard After many bug fixes the PET gets an overhaul - a more expandable motherboard, new full-sized keyboard (at the expense of the tape drive), ‘upgrade’ BASIC ROMs now include disk drive support. Two models exist, the CBM (b) series with business keyboard and the PET (n) series with graphics keyboard. Starting price for the 8k versions $795.00. (later models would come with 4.0 BASIC and be labeled also the 4000 series - see below) commodore CBM 8008, 8016, 8032 (1980) 8, 16 or 32k RAM • 80x25 monochrome display • 73 key keyboard commodore introduces a more business-like PET model in spring 1980, the 8000 series, again with a newer motherboard to support the more flexible video controller driving the new 12” display as well as integrated piezo speaker for sound. -

Learn Programming Or Fun and the Future

A MARSHALL CAVENDIS 9 COMPUTER COURSE IN WEEKLY PARTS LEARN PROGRAMMING OR FUN AND THE FUTURE HOW TO ORDER YOUR BINDERS UK and Republic of Ireland: Send £4.95 (inc p & p) (IR£5.45) for each binder to the address below: Marshall Cavendish Services Ltd, Department 980, Newtown Road, Hove, Sussex BN3 7DN Australia: See inserts for details, or Vol 1 No 9 write to INPUT, Gordon and Gotch Ltd, PO Box 213, Alexandria, NSW 2015 New Zealand: See inserts for details, or write to INPUT,Gordon and Gotch APPLICATIONS (NZ) Ltd, PO Box 1595, Wellington . . Malta: Binders are available from F DISPLAY YOUR FACTS AND FIGUR ES 267 A local newsagents. Type this program in and you will instantly be able to prepare a colourful bar chart of any data GAMES PROGRAMMING 9 There are four binders each holding 13 issues. PLANNING AN ADVENTURE 264 The first part of a series showing you how to BACK NUMBERS Copies of any part of INPUT can be obtained from the following addresses at the develop a complete adventure game regular cover price, with no extra charge for postage and packing: UK and Republic of Ireland: BASIC PROGRAMMING 19 INPUT, Dept AN, Marshall Cavendish Services, Newtown Road, Hove BN3 7DN Australia, New Zealand and Malta: CROSS-REFERENCING YOUR ARRAYS 269 Back numbers are available through your local newsagent How to store information in multi-dimensioned arrays, and then call up the data to order MACHINE CODE 10 COPIES BY POST Our Subscription Department can supply your copies direct to you regularly at £1.00 each. -

The Commodore 128 1 What's in This Book 2 the Commodore 128: Three Computers in One 3 the C128 Mode 6 the CP/M Mode 9 the Bottom Line 9

The Official Book T {&~ Commodore \! 128 Personal Computer - - ------~-----...::.......... Mitchell Waite, Robert Lafore, and Jerry Volpe The Official Book ~~ Commodore™128 Personal Computer Howard W. Sams & Co., Inc. A Subsidiary of Macmillan, Inc. 4300 West 62nd Street, Indianapolis, Indiana 46268 U.S.A. © 1985 by The Waite Group, Inc. FIRST EDITION SECOND PRINTING - 1985 All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical. photocopying, recording, or otherwise, with out written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein. International Standard Book Number: 0-672-22456-9 Library of Congress Catalog Card Number: 85-50977 Illustrated by Bob Johnson Typography by Walker Graphics Printed in the United States of America The Waite Group has made every attempt to supply trademark information about company names, products, and services mentioned in this book. The trademarks indicated below were derived from various sources. The Waite Group cannot attest to the accuracy of this information. 8008 and Intel are trademarks of Intel Corp. Adventure is a trademark of Adventure International. Altair 8080 is a trademark of Altair. Apple II is a registered trademark of Apple Computer, Inc. Atari and Atari 800 are registered trademarks of Atari Inc. Automatic Proofreader is a trademark of COMPUTE! Publications. -

Cegmon User's Guide

a new monitor for OSI and UK101 BASIC-in-ROM systems user's guide Warranty terms There is no warranty, either expressed or implied, for CEGMON in any version. CEGMON is sold subject to the distributor's standard conditions of sale, copies of which are available on request. Although it has been extensively tested and is believed to be error-free, there is no guarantee that any of the software will operate under conditions not noted in this User Guide. Despite the above, we would be grateful for any comments regarding CEGMON or on any possible faults which may appear, to help us in developing future versions. Licensing and copyright terms CEGMON and its documentation are protected both by copyright and also by our standard licensing agreement for software (copies available on request). In essence, you have bought a 2716 EPROM and associated documentation, and a licence to use the software contained on or in it for your own purposes on your own computer. Copying all or any part of the software onto any medium or into any retrieval system and/or using this on a computer not owned by you is expressly excluded from the terms of your licence and would constitute a breach of contract. CEGMON © 1980 George Chkiantz, Richard Elen, Tom Graves Sold under licence and distributed by Mutek, Quarry Hill, Box, Wiltshire, England Documentation prepared by Wordsmiths, 19a West End, Street, Somerset BA16 OLQ Introduction CEGMON has been developed to provide you with the kind of firmware support that you need to get the most out of your computer. -

Commodore 64, 1982

"THE COMMODORE 64COULD BETHE MICROCOMPUTER INDUSTRY'S OUTSTANDING NEW PRODUCT INTRODUCTION SINCE THE BIRTH OF THIS INDUSTRY." -SHEARSON/AMERICAN,,,,,, ,,,,, EXPRESS,,, FOR$595.YOUGET WHAT NOBODYELSECANF- =:YOU I I FORTWICETHE. .... IN Even at twice the price, you won't find the power and analysts such as Shearson/American Express to of a Commodore 64 in any personal computer: The the typewriter for the kind of praise you read on Commodore 64 has a built-in memory of 64K. the cover. That fact alone would have sent computer critics But there's more. As a quick read here will tell you. THE &,QUITE SIMPL!HAS NOCOMPETITION. AS A QUICK LOOK ATOUR COMPETITION WIUTEUYOU. COMMODORE APPLE IBMa TAN DY ATA R l Features 64 II+@ TRS-808 Ili 800" - --- - -- 1 I Base Price* - " ,, * $595 $1530 - - $1565 Advanced Personal Computer Features- Built-in User Memory ,, ,, 64K 48K 16K 16K 48K .. L' Proarammable Yes Yes Yes Yes Yes ~eaT~~pewriterKeyboard Yes (66 keys) Yes (52keys) Yes (83 keys) Yes (65 keys) Yes (61keys Graphics Characters (from Keyboard) Yes No No No Yes Upper and Lower Case Letters Yes Upper Only Yes Yes Yes 5%" Disk Ca~acitvPer Drive 170K 143K 160K 178K 96K Audio Features Sound Generator ' ,I Yes Yes Music Synthesizer. .. I Yes No . .. .- Hi-Fi Output . .. Yes No i No Yes Video Features II II- , TV Output " 11. Yes Extra Extra I No I Yes -Input/Output Features "Smart" Peripherals Yes No - NO I NO I yes --v--- ,r -- - - - -- " ' :"+I11 -IIIIC :- - 0x1 =:. Software Features 5 1 I c - i ii~ 1?E7 )I..- 1 Y5 CP/M" Option (Over 1,000 packag;$j" rn yes" YE Yes - NO ' - Game Machine Features - z::=;-rJ 1 Cartr~dgeGame Slot - 1rni11- !:;=' I Yes No 1 Yes Game Controllers -L- - Yes Yes - .wT-,-,~ Yes I ;: Yes 'Manufacturer's Suggested Retail Pr~ceJuly1 1982 Disk drives and printersare not includedin prices The 64's price may change without notice And.