A Commodore PET-2001 Clone

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

How to Get Hundreds of Free Programs for the VIC·20 And

Second Class Mail Registration no. 5918, Shelburne, Ontario The INDEPENDENT Commodore Users' Magazine No. 20 JUNE 1983 ~'),~() VIC, PET Making Games, Finding Games, and Playing Games. C-64 GAMES Is It Good or Bad? How to get Hundreds of Free Programs for the VIC·20 and Commodore 64 see page 2 10610 BAYVIEW (Bayview Plaza) RICHMOND HILL, ONTARIO, CANADA L4C 3N8 (416) 884-4165 C64-LINK' The Smart 64 RTC Call or write payments Serial by VISA, Cartridge Audio 1/0 MASTERCARD Expansion Slot Switch RF Video Port Cassette Port Users Port or BANK TRANSFER. Mail orders also by certified check, etc. IEEE Disks (2031) (4040) Tape VIC Modem (8050) (8250) (9090) lEE E Printers 1541 Drive or VL3 Cable Many more 64s And V L 16 (4022) (8023) to Parallel 1525 Printer (8300) Printer etc. or 1515 Printer Wf fl (future) lEE E to Par a II e I IEEE to Serial or VL4 Cable Interface Cartridge Interface to Standard Parallel M other Board True Serial Modem Devices Devices Give These Expanded Capabilities To Your 64 * The ability to transfer data from any type of device to another (IEEE, Serial, Parallel) ,it I * BASIC 4.0 which allows you to run more PET BASIC programs and gives you extended disk and 110 commands. I And * The ability to have several 64s on line together - sharing common IEEE PAL © devices such as disks or printers with Spooling Capability. * Built-in machine language monitor I * A built-in terminal or modem program which allows the system to communi Spooling Other cate through a modem to many bulletin board systems and other computer mainframes. -

The Commodore 64 Survival Manual

THE COMMODORE 64 SURVIVAL MANUAL Bantam Books of Related Interest Ask your bookseller for the books you have missed THE COMPLETE BUYER’S GUIDE TO PERSONAL COMPUTERS by Tim Hartnell and Stan Veit THE FRIENDLY COMPUTER BOOK: A SIMPLE GUIDE FOR ADULTS by Gene Brown HOW TO GET THE MOST OUT OF COMPUSERVE by Charles Bowen and Dave Peyton THE ILLUSTRATED COMPUTER DICTIONARY by The Editors of Consumer Guide® MASTERING YOUR TIMEX SINCLAIR 1000/1500™ PERSONAL COMPUTER by Tim Hartnell and Dilwyn Jones THE COMMODORE 64 SURVIVAL MANUAL Winn L. Rosch Illustrations by Steve Henry A Hard/Soft Press Book BANTAM BOOKS TORONTO • NEW YORK • LONDON • SYDNEY • AUCKLAND THE COMMODORE 64 SURVIVAL MANUAL A Bantam Book I August 1984 Sprite and sound assistance: Michael Callery All rights reserved. Copyright © 1984 Hard!Soft Inc. Cover art copyright © 1984 by Bantam Books, Inc. This book may not be reproduced in whole or in part, by mimeograph or any other means, without permission. For information address: Bantam Books, Inc. ISBN 0-553-34127-8 Published simultaneously in the United States and Canada Bantam Books are published by Bantam Books, Inc. Its trademark, consisting of the words "Bantam Books” and the portrayal of a rooster, is Registered in U.S. Patent and Trademark Office and in other countries. Marca Registrada. Bantam Books, Inc., 666 Fifth Avenue, New York, New York 10103. PRINTED IN THE UNITED STATES OF AMERICA HL 0987654321 To Granny TABLEOFCONTENTS 1 INTRODUCING THE COMMODORE 64 1 Computer basics made easy. Peripherals, applications, shopping notes, and general hints and tips. 2 BEATING THE SYSTEM______________________ 16 What’s inside your C-64 and how does it work? A fasci nating look at monitors, printers, plotters, storage media, modems, paddles, joysticks, and other devices. -

Commodore Enters in the Play “Business Is War, I Don't Believe in Compromising, I Believe in Winning” - Jack Tramiel

Commodore enters in the play “Business is war, I don't believe in compromising, I believe in winning” - Jack_Tramiel Commodore_International Logo Commodore International was an American home computer and electronics manufacturer founded by Jack Tramiel. Commodore International (CI), along with its subsidiary Commodore Business Machines (CBM), participated in the development of the home personal computer industry in the 1970s and 1980s. CBM developed and marketed the world's best-selling desktop computer, the Commodore 64 (1982), and released its Amiga computer line in July 1985. With quarterly sales ending 1983 of $49 million (equivalent to $106 million in 2018), Commodore was one of the world's largest personal computer manufacturers. Commodore: the beginnings The company that would become Commodore Business Machines, Inc. was founded in 1954 in Toronto as the Commodore Portable Typewriter Company by Polish-Jewish immigrant and Auschwitz survivor Jack Tramiel. By the late 1950s a wave of Japanese machines forced most North American typewriter companies to cease business, but Tramiel instead turned to adding machines. In 1955, the company was formally incorporated as Commodore Business Machines, Inc. (CBM) in Canada. In 1962 Commodore went public on the New York Stock Exchange (NYSE), under the name of Commodore International Limited. Commodore soon had a profitable calculator line and was one of the more popular brands in the early 1970s, producing both consumer as well as scientific/programmable calculators. However, in 1975, Texas Instruments, the main supplier of calculator parts, entered the market directly and put out a line of machines priced at less than Commodore's cost for the parts. -

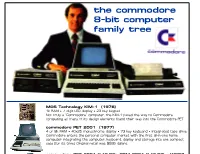

The Commodore 8-Bit Computer Family Tree

the commodore 8-bit computer family tree MOS Technology KIM-1 (1976) 1k RAM • 7 digit LED display • 23 key keypad Not truly a “Commodore” computer, the KIM-1 paved the way to Commodore computing as many of its design elements found their way into the Commodore PET commodore PET 2001 (1977) 4 or 8k RAM • 40x25 monochrome display • 73 key keyboard • Integrated tape drive Commodore enters the personal computer market with the first all-in-one home computer integrating the computer, keyboard, display and storage into one compact case (for its time). Original retail was $595 dollars. commodore PET 2001-8,16,32n CBM 2001-8,16,32b (1978) commodore PET 2001-8,16,32n CBM 2001-8,16,32b (1978) 8, 16 or 32k RAM • 40x25 monochrome display • 74[n]/73[b] key keyboard After many bug fixes the PET gets an overhaul - a more expandable motherboard, new full-sized keyboard (at the expense of the tape drive), ‘upgrade’ BASIC ROMs now include disk drive support. Two models exist, the CBM (b) series with business keyboard and the PET (n) series with graphics keyboard. Starting price for the 8k versions $795.00. (later models would come with 4.0 BASIC and be labeled also the 4000 series - see below) commodore CBM 8008, 8016, 8032 (1980) 8, 16 or 32k RAM • 80x25 monochrome display • 73 key keyboard commodore introduces a more business-like PET model in spring 1980, the 8000 series, again with a newer motherboard to support the more flexible video controller driving the new 12” display as well as integrated piezo speaker for sound. -

The Commodore 128 1 What's in This Book 2 the Commodore 128: Three Computers in One 3 the C128 Mode 6 the CP/M Mode 9 the Bottom Line 9

The Official Book T {&~ Commodore \! 128 Personal Computer - - ------~-----...::.......... Mitchell Waite, Robert Lafore, and Jerry Volpe The Official Book ~~ Commodore™128 Personal Computer Howard W. Sams & Co., Inc. A Subsidiary of Macmillan, Inc. 4300 West 62nd Street, Indianapolis, Indiana 46268 U.S.A. © 1985 by The Waite Group, Inc. FIRST EDITION SECOND PRINTING - 1985 All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical. photocopying, recording, or otherwise, with out written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein. International Standard Book Number: 0-672-22456-9 Library of Congress Catalog Card Number: 85-50977 Illustrated by Bob Johnson Typography by Walker Graphics Printed in the United States of America The Waite Group has made every attempt to supply trademark information about company names, products, and services mentioned in this book. The trademarks indicated below were derived from various sources. The Waite Group cannot attest to the accuracy of this information. 8008 and Intel are trademarks of Intel Corp. Adventure is a trademark of Adventure International. Altair 8080 is a trademark of Altair. Apple II is a registered trademark of Apple Computer, Inc. Atari and Atari 800 are registered trademarks of Atari Inc. Automatic Proofreader is a trademark of COMPUTE! Publications. -

Commodore 64, 1982

"THE COMMODORE 64COULD BETHE MICROCOMPUTER INDUSTRY'S OUTSTANDING NEW PRODUCT INTRODUCTION SINCE THE BIRTH OF THIS INDUSTRY." -SHEARSON/AMERICAN,,,,,, ,,,,, EXPRESS,,, FOR$595.YOUGET WHAT NOBODYELSECANF- =:YOU I I FORTWICETHE. .... IN Even at twice the price, you won't find the power and analysts such as Shearson/American Express to of a Commodore 64 in any personal computer: The the typewriter for the kind of praise you read on Commodore 64 has a built-in memory of 64K. the cover. That fact alone would have sent computer critics But there's more. As a quick read here will tell you. THE &,QUITE SIMPL!HAS NOCOMPETITION. AS A QUICK LOOK ATOUR COMPETITION WIUTEUYOU. COMMODORE APPLE IBMa TAN DY ATA R l Features 64 II+@ TRS-808 Ili 800" - --- - -- 1 I Base Price* - " ,, * $595 $1530 - - $1565 Advanced Personal Computer Features- Built-in User Memory ,, ,, 64K 48K 16K 16K 48K .. L' Proarammable Yes Yes Yes Yes Yes ~eaT~~pewriterKeyboard Yes (66 keys) Yes (52keys) Yes (83 keys) Yes (65 keys) Yes (61keys Graphics Characters (from Keyboard) Yes No No No Yes Upper and Lower Case Letters Yes Upper Only Yes Yes Yes 5%" Disk Ca~acitvPer Drive 170K 143K 160K 178K 96K Audio Features Sound Generator ' ,I Yes Yes Music Synthesizer. .. I Yes No . .. .- Hi-Fi Output . .. Yes No i No Yes Video Features II II- , TV Output " 11. Yes Extra Extra I No I Yes -Input/Output Features "Smart" Peripherals Yes No - NO I NO I yes --v--- ,r -- - - - -- " ' :"+I11 -IIIIC :- - 0x1 =:. Software Features 5 1 I c - i ii~ 1?E7 )I..- 1 Y5 CP/M" Option (Over 1,000 packag;$j" rn yes" YE Yes - NO ' - Game Machine Features - z::=;-rJ 1 Cartr~dgeGame Slot - 1rni11- !:;=' I Yes No 1 Yes Game Controllers -L- - Yes Yes - .wT-,-,~ Yes I ;: Yes 'Manufacturer's Suggested Retail Pr~ceJuly1 1982 Disk drives and printersare not includedin prices The 64's price may change without notice And. -

Instituto De Ciências Matemáticas E De Computação Evolução Histórica Da Computação Profa

HISTÓRIA DO COMPUTADOR INSTITUTO DE CIÊNCIAS MATEMÁTICAS E DE COMPUTAÇÃO EVOLUÇÃO HISTÓRICA DA COMPUTAÇÃO PROFA. ROSANA BRAGA MATERIAL: PROF. MAURÍCIO A DIAS 2 LINHA DO TEMPO ANO Inventores/Invenções Descrição 1936 Konrad Zuse - Z1 Computer Primeiro Computador Programável 1942 John Atanasoff & Clifford Berry Os primeiros no mercado de ABC Computer computadores 1944 Howard Aiken & Grace Hopper Harvard Mark 1. Harvard Mark I Computer 1946 John Presper Eckert & John W. 20,000 vacuum tubes later... Mauchly ENIAC 1 Computer 1948 Frederic Williams & Tom Kilburn Outra empresa de computadores Manchester Baby Computer & The Williams Tube 1947/48 John Bardeen, Walter Brattain & Invenção do Transistor Wiliam Shockley The Transistor 3 LINHA DO TEMPO ANO Inventores/Invenções Descrição 1951 John Presper Eckert & John W. Primeiro computador comercial Mauchly para votação UNIVAC Computer 1953 International Business Machines IBM entra para a história dos IBM 701 EDPM Computer computadores 1954 John Backus & IBM Primeira linguagem de FORTRAN Computer programação de sucesso Programming Language 1955 Stanford Research Institute, Primeiro computador bancário (In Use 1959) Bank of America, and General com reconhecimento de tintas Electric magnéticas em cheques ERMA and MICR 1958 Jack Kilby & Robert Noyce O chip como conhecemos hoje é The Integrated Circuit desenvolvido 1962 Steve Russell & MIT Primeiro jogo eletrônico Spacewar Computer Game inventado 4 LINHA DO TEMPO ANO Inventores/Invenções Descrição 1964 Douglas Engelbart O Mouse foi chamado assim pois Computer -

PETSCII – a Character Set and a Creative Platform

Replay 1(5) 2018 http://dx.doi.org/10.18778/2391-8551.05.02 Markku Reunanen University of Turku and Aalto University Tero Heikkinen University of the Arts Helsinki Anders Carlsson PETSCII – A Character Set and a Creative Platform Introduction Throughout the 1980s Commodore International was arguably the king of the home computer market, thanks to its successful VIC-20, Commodore 64 and the Amiga line of computers (e.g. Bagnall, 2005). The wildly popular Commodore 64, in particular, became an iconic machine of the home computer boom of the early 1980s. One fac- tor contributing to its recognizable aesthetic was its PETSCII character set which the 1980s enthusiasts still remember from the blue startup screen stating that there were “38911 BASIC BYTES FREE”. Even if the C-64 was capable of various pixel graphic modes, its text mode, too, found its uses and has recently become popular again, as a number of visual artists have started experimenting with the format and pushing its boundaries over the last few years. Before we begin, it is necessary define what “PETSCII” means, as the term has differ- ent meanings depending on the context. Technically speaking, it refers to Commodore’s PET Standard Code of Information Interchange, a character encoding used on Commo- dore’s 8-bit computers that partially overlaps with the widely used ASCII encoding. In practice, however, the term is commonly used to denote the built-in character set and font of the Commodore 64, which is also the focus of this article. As can be seen in Figure 1, there are minor differences in the character set between machines and their revisions: for example, European C-64s featured a pound sign instead of a backslash. -

Commodore: Pet

Commodore: Pet Commodore Pet (Personal Electronic Transactor) was the first computer to be produced by Commodore, the company. It was introduced in January 1977 and five months later it had hit the shelves. It was very well received by people especially in the United States, Canada and the United Kingdom. It was the top seller in these markets. Initially, Commodore had planned to produce a calculator. After much debate between the top heads of the company, it was concluded that calculators were a dead end and instead the company will focus its energy and resources in building a ‘real’ machine. In order to be able to show off their ‘real’ machine at the Consumer Electronic Show, two people put their heads together, Leonard Tramiel and Chuck Peddle, to produce the prototype of the first ever all in one home computer. It took these two just six months to produce a computer that was going to be lay the foundation for their later models. The first computer from Commodore was named ‘Pet 2001’. This was a very simple computer with 4 KB of RAM and a 1 MHz MOS Technology 6502 CPU. Later models such as Pet 2001‐8N, Pet 2001‐16N and Pet 2001‐32N had 8Kb, 16KB and 32KB of RAM respectively. The Commodore Pet gained wide spread popularity specifically in the education sector. Its metal body as well as the all in one design made it perfect for rigorous use in classrooms. Since disk drives and printers were very expensive at that time, the IEEE port allowed the sharing of these resources, making it affordable for schools. -

Commodore 64

Second Class Mail Registration no. 5918, Shelburne, Ontario The INDEPENDENT Commodore Users' Magazine No. 22 August 1983 New The Chicago C-64, VIC C.E.S. Report and PET by Chris Bennett p.1S Products New, Updated Lists of Thousands of Public Domain Programs p_ 73 10610 BAYVIEW (Bayview Plaza) RICHMOND HILL, ONTARIO, CANADA L4C 3N8 (416) 884-4165 C64-LINK© The Smart 64 RTC Call orwrite payments Serial by VISA , Cartridge Audio 1/ 0 MASTERCARD Expansion Slot Switch RF Video Port Cassette Port Users Port or BANK TRANSFER. • Mail orders also by certified check, etc. IEEE Disks (2031) (4040) Tape VIC Modem (8050) (8250) (9090) I EEE Printers 1541 Drive or VL3 Cable Many more 64s And VL 16 (4022) (8023) to Parallel 1525 Printer (8300) Printer etc. or 1515 Printer (future) l EE E to Parallel IEEE to Serial or VL4 Cable Cartridge Interface Interface to Standard M other Board Parallel True Serial Modem Devi ces Devices Give These Expanded Capabilities To Your 64 * The ability to transfer data from any type of device to another (IEEE, Serial, Parallel) * BASIC 4.0 which allows you to run more PET BASIC programs and gives you extended disk and 110 commands. POWER ® And * The ability to have several 64s on line together - sharing common IEEE U~hl PAL © devices such as disks or printers with Spooling Capability . * Built-in machine language monitor * A built-in terminal or modem program wh ich allows the system to communi Spooling Other cate through a modem to many bulletin board systems and other computer mainframes. -

Compute Mar/Apr 1980 Issue #3

MARCH I APRIL 1980. ISSUE 3. $2.00 II The Journal for Progressive Computing™ Manual Alphabet ~ Tutorial on a PET .SUSAN SEMANCIK. full featured mnemonic assembler-disassembler enter save load hst run hst the secret baSlc RO Ms RIVI ACE ~ * 1:f 2 ACTION PACKED VIDEO GAMES* * ! PET BASIC BREAKTHROUGH i ~ ~ ~ ~ ~ Softside Soflware j ~ ~ ! presents I ~ ~ ! SYMBOLIC/STRUCTURED BASIC ! ~ t N. last. Symbolic/Structured Basic is ample: LOOP/PRINT "HI": GO TO LOOP. S- iC t available for your PET 8-32K personal com Basic program lines can be up to 255 iC puter! S-Basic is a pre-compiler that enhan characters long, two-and-one-hali times as t t ces the PET's built-in basic monitor with the long as on standard Basic. S-Basic does not ~ t oddition of extra-control statements found compromise any of PET Basie's existing fea- t ~ only in the most sophisticated computers. tures. All PET Basic commands can be used. ~ ~ WHILE ... GOSUB ... calls a subroutine as S-Basic includes an editor with full text ca- ie : long as a condition is true. UNTIL ... GOSUB pabilities. a translator/pre-compiler with its ~ ~ ... jumps to a subroutine unless the condition own errormessages. and the 5-Basicloader. ~ ~ is true. The IF ... Then ... ELSE statement al These programs are recommended for disk- ! ~ lows the programmer to command the based PETs. A printer is optional but sug- ..;: ~ computer to execute instructions if the nor gested. Cassette copies are available and t ~ mal IF condition is not met. require two cassette drives. Comprehen- ~ t Forget about line numbers, S-Basic al sive instructions are included. -

KIM-1 MOS Technology Developed a Second System Concurrently with the TIM

C H A P T E R 11..55 TTiimm aanndd KKiimm 11997755 -- 11997766 In introducing the 6502 microprocessor to the world, Chuck Peddle knew he had something revolutionary. As part of MOS Technology’s marketing plan to encourage people to experiment with the 6502, Peddle and his team at MOS Technology would develop two small computer systems, known as development systems. “They worked on them while we were finishing up the processor and getting ready to do the marketing,” explains Peddle. Engineers and hobbyists, the idea went, would use them to evaluate the 6502 instruction set and develop their own systems. The Kit The first development system offered by MOS was in kit form, which reduced the selling price to only $30. Since the unit was designed primarily to instruct the user on the workings of computer systems in general and the 6502 in particular, MOS Technology contracted Microcomputer Associates of Santa Clara, California to write the unit’s internal program. The two founders, Ray Holt and Manny Lemas, taught engineers how to use microprocessors. Peddle relates, “You have to understand how little the world knew of microprocessors in 1974, ‘75 and ‘76. There were guys making big money selling classes on microprocessors during that time.” Manny Lemas had worked for Peddle during his GE days, while Ray Holt had an impressive background working on the F-14 Tomcat project for the Navy.1 The technicians developed the system in a special research area on the second floor of MOS Technology. The lab was a room within a room, with a large sign on the door in capital letters warning NO ADMITANCE.