System for Preventing the Use of an Unauthorized External Memory

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3 Glossary

Video Game Design Foundations ©2014 Chapter 3: Evolution of the Game—Glossary Atari 2600. First commercially successful video game system (1977) for homes; allowed the owner to purchase individual game cartridges. Backward compatibility. Older games can be played on newer game consoles. Balance. Mix of physical, mental, work, and play activities. Behavioral development. Learning how to react to situations. Bit. Computer term for a single binary digit of 0 or 1. Board game. A portable game environment in which players use imagination to engage in mental or strategic competition. Brain-extremity pathways. Nerve connection from the brain to movement points throughout the body. Card games. A series of uniquely printed cards used within set rules of a game. Carpal tunnel syndrome. Condition that causes pain or tingling in the hand resulting from a pinched nerve in the wrist. Chance. Adds interest to a game by allowing different random results each time a game is played. Cocooning. Social phenomenon where people do not interact with their physical environment. Cognitive development. Building of intelligence through learning, remembering, and problem solving. Commercial success. Product that makes enough of a profit to continue producing it. Compact disc, read-only memory (CD-ROM). Provides interchangeable video games on an inexpensive plastic disc; replacement technology for the ROM game cartridges. Compete. To play against an opponent with a goal or victory condition to determine who is the best. Competitive advantage. Benefit to consumers that other companies do not provide. Content descriptors. Part of a rating system; indicates elements in the game that may have triggered a particular rating. -

Openbsd Gaming Resource

OPENBSD GAMING RESOURCE A continually updated resource for playing video games on OpenBSD. Mr. Satterly Updated August 7, 2021 P11U17A3B8 III Title: OpenBSD Gaming Resource Author: Mr. Satterly Publisher: Mr. Satterly Date: Updated August 7, 2021 Copyright: Creative Commons Zero 1.0 Universal Email: [email protected] Website: https://MrSatterly.com/ Contents 1 Introduction1 2 Ways to play the games2 2.1 Base system........................ 2 2.2 Ports/Editors........................ 3 2.3 Ports/Emulators...................... 3 Arcade emulation..................... 4 Computer emulation................... 4 Game console emulation................. 4 Operating system emulation .............. 7 2.4 Ports/Games........................ 8 Game engines....................... 8 Interactive fiction..................... 9 2.5 Ports/Math......................... 10 2.6 Ports/Net.......................... 10 2.7 Ports/Shells ........................ 12 2.8 Ports/WWW ........................ 12 3 Notable games 14 3.1 Free games ........................ 14 A-I.............................. 14 J-R.............................. 22 S-Z.............................. 26 3.2 Non-free games...................... 31 4 Getting the games 33 4.1 Games............................ 33 5 Former ways to play games 37 6 What next? 38 Appendices 39 A Clones, models, and variants 39 Index 51 IV 1 Introduction I use this document to help organize my thoughts, files, and links on how to play games on OpenBSD. It helps me to remember what I have gone through while finding new games. The biggest reason to read or at least skim this document is because how can you search for something you do not know exists? I will show you ways to play games, what free and non-free games are available, and give links to help you get started on downloading them. -

Sega Genesis Manual

January 22, 2009 Sega Technical Overview 1.00 Page 1 GENESIS Technical Overview CONFIDENTIAL PROPERTY OF SEGA Look forward to more Tech notes: Super Nintendo Jaguar Edited by Nemesis – corrupted images repaired January 22, 2009 Sega Technical Overview 1.00 Page 2 GENESIS: 68000 @8 MHz • main CPU • 1 MByte (8 Mbit) ROM Area • 64 KByte RAM Area VDP (Video Display Processor) • dedicated video display processor - controls playfield & sprites - capable of DMA - Horizontal & Vertical interrupts • 64 KBytes of dedicated VRAM (Video Ram) • 64 x 9-bits of CRAM (Color RAM) Z80 @4 MHz • controls PSG (Programmable Sound Generator) & FM Chips • 8 KBytes of dedicated Sound Ram VIDEO: • NOTE: Playfield and Sprites are character-based • Display Area (visual) - 40 chars wide x 28 chars high • each char is 8 x 8 pixels • pixel resolution = 320 x 224 - 3 Planes • 2 scrolling playfields • 1 sprite plane • definable priorities between planes - Playfields: • 6 different sizes • 1 playfield can have a "fixed" window • playfield map - each char position takes 2 Bytes, that includes: • char name (10 bits); points to char definition • horizontal flip • vertical flip • color palette (2 bits); index into CRAM • priority January 22, 2009 Sega Technical Overview 1.00 Page 3 • scrolling: - 1 pixel scrolling resolution - horizontal: • whole playfield as unit • each character line • each scan line - vertical: • whole playfield as unit • 2 char wide columns - Sprites: • 1 x 1 char up to 4 x 4 chars • up to 80 sprites can be defined • up to 20 sprites displayed on a scan -

Examining the Dynamics of the US Video Game Console Market

Can Nintendo Get its Crown Back? Examining the Dynamics of the U.S. Video Game Console Market by Samuel W. Chow B.S. Electrical Engineering, Kettering University, 1997 A.L.M. Extension Studies in Information Technology, Harvard University, 2004 Submitted to the System Design and Management Program, the Technology and Policy Program, and the Engineering Systems Division on May 11, 2007 in Partial Fulfillment of the Requirements for the Degrees of Master of Science in Engineering and Management and Master of Science in Technology and Policy at the Massachusetts Institute of Technology June 2007 C 2007 Samuel W. Chow. All rights reserved The author hereby grants to NIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now know and hereafter created. Signature of Author Samuel W. Chow System Design and Management Program, and Technology and Policy Program May 11, 2007 Certified by James M. Utterback David J. cGrath jr 9) Professor of Management and Innovation I -'hs Supervisor Accepted by Pat Hale Senior Lecturer in Engineering Systems - Director, System Design and Management Program Accepted by Dava J. Newman OF TEOHNOLoGY Professor of Aeronautics and Astronautics and Engineering Systems Director, Technology and Policy Program FEB 1 E2008 ARCHNOE LIBRARIES Can Nintendo Get its Crown Back? Examining the Dynamics of the U.S. Video Game Console Market by Samuel W. Chow Submitted to the System Design and Management Program, the Technology and Policy Program, and the Engineering Systems Division on May 11, 2007 in Partial Fulfillment of the Requirements for the Degrees of Master of Science in Engineering and Management and Master of Science in Technology and Policy Abstract Several generations of video game consoles have competed in the market since 1972. -

Keeping the Game Alive: Evaluating Strategies for the Preservation of Console Video Games

64 Keeping the Game Alive The International Journal of Digital Curation Issue 1, Volume 5 | 2010 Keeping the Game Alive: Evaluating Strategies for the Preservation of Console Video Games Mark Guttenbrunner, Christoph Becker, Andreas Rauber, Vienna University of Technology Abstract Interactive fiction and video games are part of our cultural heritage. As original systems cease to work because of hardware and media failures, methods to preserve obsolete video games for future generations have to be developed. The public interest in early video games is high, as exhibitions, regular magazines on the topic and newspaper articles demonstrate. Moreover, games considered to be classic are rereleased for new generations of gaming hardware. However, with the rapid development of new computer systems, the way games look and are played changes constantly. When trying to preserve console video games one faces problems of classified development documentation, legal aspects and extracting the contents from original media like cartridges with special hardware. Furthermore, special controllers and non-digital items are used to extend the gaming experience making it difficult to preserve the look and feel of console video games. This paper discusses strategies for the digital preservation of console video games. After a short overview of console video game systems, there follows an introduction to digital preservation and related work in common strategies for digital preservation and preserving interactive art. Then different preservation strategies are described with a specific focus on emulation. Finally a case study on console video game preservation is shown which uses the Planets preservation planning approach for evaluating preservation strategies in a documented decision-making process. -

Lessons from the Game Cartridge Kevin Christopher Tuesday, March

Lessons from the Game Cartridge Kevin Christopher Tuesday, March 16, 2004 STS 145 Lessons from the Game Cartridge For most of their history, computer games were the province of the computer engineers. They wrote the first games, they designed the first hardware, and they provided the quirky, fantasy humor that brought so much creative material to the modern games market. It is thus in no way surprising that the adoption of the video game cartridge should appeal to these engineers; it was a solution to a design problem, a solution that only later came to be distorted by imitators and marketing interests. Today, the march of technology has eliminated all but the last vestiges of the video game cartridge from modern game consoles, though it still retains many of the difficult lessons learned by the early game companies. This history, then, is a history of the game cartridge. Of the Magnavox Odyssey and the beginnings of the game cartridge. Of the Atari 2600, the true classic of the gaming market, whose very popularity caused it to fail. Of the Nintendo Entertainment System, the first console to control, and even abuse, the cartridge system. This is a history of consoles and video games, as told through the game cartridge. It is the story of how a piece of technology drove a market. The first cartridges: Magnavox Odyssey Going back to the very beginnings of game cartridges requires a journey to the first game console that supported multiple games: the Magnavox Odyssey. In 1968, Ralph Baer and Lou Etlinger demonstrated a prototype console for Magnavox executives; four years later, in 1972, the Odyssey reached the market [1]. -

Nintendo 64 Frequently Asked Questions

Nintendo 64 Frequently Asked Questions General Questions ● Game Questions ● Troubleshooting Questions Nintendo 64 Frequently Asked Questions Table of Contents General Questions .......................................................................................................................... 3 Game Questions .............................................................................................................................. 4 Troubleshooting Questions............................................................................................................. 5 2 Nintendo 64 Frequently Asked Questions General Questions Q. Where can I purchase an N64 console, accessories, and games? A. You can purchase an N64, its accessories, or games through various sellers on Amazon and eBay or retailers like GameStop. Q. How can I use the N64 with an HDTV? A. You will need to purchase an additional A/V to HDMI converter and an HDMI cable if you do not own one. For information on how to setup the HDMI converter with the N64, refer to the N64 User Manual. Q. What N64 variants are available? A. There are numerous types of N64 consoles available, including variants that were exclusive to certain regions. Below are a few North American N64 variants: • Charcoal Grey • Grape Purple • Smoke Black • Pikachu Edition For more information on console variants, refer to the N64 Product Overview. For more information on region-specific consoles, refer to the Troubleshooting section. Q. What accessories are available for the N64? A. The N64 has several accessories, including: • Controller Pak • Rumble Pak • Expansion Pak For more information on N64 accessories, refer to the N64 Product Overview. Q. What are the Specifications for the N64? A. The specifications of the N64 are: • GPU: 64-bit NEC VR4300 (MIPS R4300i) with 24 KB L1 cache, runs at 93.75 MHz • Performance: 125 MIPS, 93.75 MFLOPS • GPU: 64-bit Reality Coprocessor, running at 62.5 MHz and over 100 MFLOPS. -

Colecovision - Profile of the Record Breaking Home Arcade History of Colecovision - Visions of the Future Through Coleco Colored Glasses by D.S

ColecoVision - Profile of the Record Breaking Home Arcade History of ColecoVision - Visions of the Future Through Coleco Colored Glasses By D.S. Cohen, About.com Guide http://classicgames.about.com/od/history/a/ColecoVisionHis.htm http://classicgames.about.com/od/history/a/ColecoVisionHis_2.htm http://classicgames.about.com/od/history/a/ColecoVisionHis_3.htm http://classicgames.about.com/od/classicvideogames101/p/ColecoVProfile.htm ColecoVision - Profile of the Record Breaking Home Arcade From 1982 to 1984 ColecoVision was the most advance, powerful and popular console of the time, breaking sales records and digging deep into Atari and Intellivision’s profits. While the ColecoVision was well on its way to becoming the most successful console in history, its life was cut short by the Crash of the Video Game Market and a gamble on an overpriced, bug ridden attempt at transitioning the console into a home computer. The Basics: • Release Date: August 1982 • Discontinued:1984 • Manufacturer: Coleco Industries • Type: ROM Cartridge Based 8-bit Console Originally Packaged With: • Main Console Unit • Two ColecoVision Controllers • Donkey Kong Game Cartridge • TV/Video Switch Box • Video Connector Cable • AC Adaptor Cable Main Console: The ColecoVision Packaging - A rectangular unit, 14 X 8 inches in size, with the controller housing/connections on the top left side and the Images © Coleco Holdings, LLC. top-loading cartridge slot on the right. Expansion Modules connect via a slot on the front of the unit. On the back are the channel 3/4 switch, RF and power outlets. Expansion Modules: ColecoVision had the unique ability to expand its capabilities by adding external hardware modifications. -

Digital Preservation of Console Video Games

DIPLOMARBEIT Digital Preservation of Console Video Games Ausgef¨uhrtam Institut f¨ur Softwaretechnik und Interaktive Systeme der Technischen Universit¨atWien unter der Anleitung von ao.univ.Prof. Dr. Andreas Rauber und Dipl.-Ing. Christoph Becker als verantwortlich mitwirkendem Projektassistenten durch Mark Guttenbrunner 9325367 Neustiftgasse 85/16 1070 Vienna Austria Wien, im Oktober 2007 Abstract Video games are part of our cultural heritage, but with the rapid development of new computer systems the way games look and are played changes rapidly. The public interest in early video games is high, as exhibitions, regular magazines on the topic and newspaper articles show. Games considered to be classic are rereleased for new generations of gaming hardware as well. As original systems cease to work because of hardware and media failures, methods to preserve obsolete video games for future generations have to be de- veloped. This work evaluates strategies for digital preservation of console video games. First it presents an overview of the history of console video game systems. Next an introduction to digital preservation and related work in common strate- gies for digital preservation and preserving interactive art is given. Then emulation as a preservation strategy and the PLANETS preservation planning approach for documented decision-making processes are described. When trying to preserve console video games one has to face the challenges of classified development documentation, legal aspects and extracting the contents from original media like cartridges with special hardware. Special controllers and non-digital items are used to extend the gaming experience making it difficult to preserve the look and feel of console video games. -

1 Japanese Video Game Industry Japanese Economy Division

Industrial Reports (c) JETRO, 2007 Japanese Video Game Industry Japanese Economy Division Summary In 2005, shipments of home video games increased for the first time in four years, bolstered by launches of the Nintendo DS and Sony PlayStation Portable. Next-generation game consoles, such as the Nintendo Wii and Sony PlayStation 3 to be marketed from the end of 2006, are expected to further expand the home video game market into 2007. Since the release of Nintendo’s Family Computer (Famicon) in 1983, Japan’s electronic game industry has come to depend on home video games to such an extent that it can be interchangeably called the game console industry. In recent years, the spread of broadband, flat-rate telecommunications services has enabled new platforms for games, such as online and mobile, further broadening the industry’s base. This report, however, covers only the home video game industry, which still accounts for a significant portion of the industry. 1. History of video game industry Japanese video game companies have been overwhelmingly competitive in the international market, but competition in the hardware sector has intensified in recent years, following the entry of Microsoft. A. Desktop game consoles The industry dawned with the runaway success of the Atari 2600, a home game device with a plug-in ROM cartridge, which was launched by Atari in the U.S. market in 1977. Third-party software could be developed freely, because Atari made the programming specifications openly available. As a result, numerous software packages appeared and were well received by users. Over time, however, user support steadily weakened as inferior software also began to circulate. -

Nintendo 64 Games Guide: V.1 Pdf, Epub, Ebook

NINTENDO 64 GAMES GUIDE: V.1 PDF, EPUB, EBOOK BradyGames | 128 pages | 01 Dec 1996 | DK Publishing | 9781566866316 | English | New York, United States Nintendo 64 Games Guide: v.1 PDF Book September 24, Video Games. Mike Piazza's Strike Zone. Starshot: Space Circus Fever. Don't ignore GVN or other similar websites, though. The game is primarily set inside and around the Mushroom Castle , itself divided in multiple rooms containing portals most represented as paintings that lead to the game's courses. Archived from the original PDF on August 10, The Secret Aquarium On the 3rd level painting room there is a hole on the left top side of the room. These stars protect the castle; with the stars in his control, the beast plans to take over the Mushroom Castle. Super Mario Shop by Category. V-Rally: Edition ' April 18, Star 2: Mystery of the Monkey cage Return to the place where the first star was, as you walk there you will see a caged star. Step on it and eventually you will come to where the star is, grab it! Mysterious Mountainside. The Nintendo 64 home video game console 's library of games were primarily released in a plastic ROM cartridge called the Game Pak. The ruler of the Mushroom Kingdom. Encyclopedia of Game Machines. Ganbare Mario. Star 6: Eye to eye in the secret room You will need the blue switch pressed before getting this star. All Languages. The games are often a pleasant and relaxing way to spend your time since your main focus is growing plants, going fishing, and sometimes raising animals. -

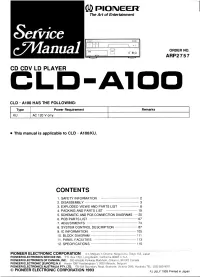

Service 0 , 0 1,- H I \ ,"1 ORDER NO, C./I1anual ~ ARP2757

@PIONEER' ~ I The Art of Entertainment Service 0 , 0 1,- H I \ ,"1 ORDER NO, c./I1anual ~ ARP2757 CD CDV LD PLAYER CLD-A1CC CLD - A100 HAS THE FOLLOWING: Type Power Requirement Remarks KU AC 120 Vonly • This manual is applicable 10 CLD - A100/KU, CONTENTS 1. SAFETY INFORMATION ····· ····· ··· · .. · .. ·· ·· .. ·· ··· ······2 2. Di SASSE MBly · .. ·· .. · .. · .. · .. · .. ········· ····· ··· · ······· 3 3. EXPLODED VI EWS AN D PARTS UST ········· ·········8 4. PACKING AND PARTS LI ST .. ····· · .. ···· .. · .. · .. · .. · .. ··19 5. SCHEMATIC AND PCB CONNECTION DIAGRAMS ... 20 6. PCB PARTS LI ST .. ... .... ... ... ... ... ···· ······· ····67 7. ADJUSTMENTS .. .. ......... ........... ·················· ··· ·· 74 8. SYSTEM CONTROL DESCRIPTION ······ ····· ··· ·· 87 9. Ie IN FORMATION .... .......... ..... ......... .. ··· ··· ·· 105 10. BLOCK DIAGRAM ···· ··· ······· ··· ·· ··········· .. ··· ··· ·· ·· 111 11 PANEL FACILITIES ................. .. ................ .. .. 113 12. SPECIFICATI ONS ·· .. · .. ...... .. · .. .. .. · .... · .. ·· .. · .. · .. ··1 15 PIONEER ELECTRONIC CORPORATION 4· 1, Megu ro 1·Chorne. Meg ur o· ku, Tokyo 153, Japan PIONEER ELECTRONICS SERVICE INC. PO. Box 1760. l ong Beach , Ca lltornl<l 90801 U. S.A PIONEER ELECTRONICS OF CANADA, INC. 300 Allstate Par kway Markh am. Ontari O l 3R OP2 Canada PIONEER ELECTRONIC [EUROPE] N.V. Have n 1087 Kee tberglaa n 1, 9120 Melse le. Bel gilim PIONEER ELECTRONICS AUSTRALIA PTY. LTD. 178· 184 Boundary Ro ad. BraeS lde , Victori a 3195, Aus tr alia TE L [03 ] 580·9911 © PIONEER ELECTRONIC CORPORATION 1993 FJ JU LY 1993 Printed in Japan CLC-AIDD 1. SAFETY INFORMATION This service manual is intended for qualified service technicians; it Is not meant for the casual do·it-yourselfer. Qualified technicians have the necessary test equipment and tools, and have been trained to properly and safely repair complex products such as those covered by this manual.