A Novel Reconfigurable Architecture of a DSP Processor for Efficient Mapping of DSP Functions Using Field Programmable DSP Arrays

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Moving Average Filters

CHAPTER 15 Moving Average Filters The moving average is the most common filter in DSP, mainly because it is the easiest digital filter to understand and use. In spite of its simplicity, the moving average filter is optimal for a common task: reducing random noise while retaining a sharp step response. This makes it the premier filter for time domain encoded signals. However, the moving average is the worst filter for frequency domain encoded signals, with little ability to separate one band of frequencies from another. Relatives of the moving average filter include the Gaussian, Blackman, and multiple- pass moving average. These have slightly better performance in the frequency domain, at the expense of increased computation time. Implementation by Convolution As the name implies, the moving average filter operates by averaging a number of points from the input signal to produce each point in the output signal. In equation form, this is written: EQUATION 15-1 Equation of the moving average filter. In M &1 this equation, x[ ] is the input signal, y[ ] is ' 1 % y[i] j x [i j ] the output signal, and M is the number of M j'0 points used in the moving average. This equation only uses points on one side of the output sample being calculated. Where x[ ] is the input signal, y[ ] is the output signal, and M is the number of points in the average. For example, in a 5 point moving average filter, point 80 in the output signal is given by: x [80] % x [81] % x [82] % x [83] % x [84] y [80] ' 5 277 278 The Scientist and Engineer's Guide to Digital Signal Processing As an alternative, the group of points from the input signal can be chosen symmetrically around the output point: x[78] % x[79] % x[80] % x[81] % x[82] y[80] ' 5 This corresponds to changing the summation in Eq. -

Discrete-Time Fourier Transform 7

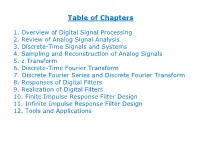

Table of Chapters 1. Overview of Digital Signal Processing 2. Review of Analog Signal Analysis 3. Discrete-Time Signals and Systems 4. Sampling and Reconstruction of Analog Signals 5. z Transform 6. Discrete-Time Fourier Transform 7. Discrete Fourier Series and Discrete Fourier Transform 8. Responses of Digital Filters 9. Realization of Digital Filters 10. Finite Impulse Response Filter Design 11. Infinite Impulse Response Filter Design 12. Tools and Applications Chapter 1: Overview of Digital Signal Processing Chapter Intended Learning Outcomes: (i) Understand basic terminology in digital signal processing (ii) Differentiate digital signal processing and analog signal processing (iii) Describe basic digital signal processing application areas H. C. So Page 1 Signal: . Anything that conveys information, e.g., . Speech . Electrocardiogram (ECG) . Radar pulse . DNA sequence . Stock price . Code division multiple access (CDMA) signal . Image . Video H. C. So Page 2 0.8 0.6 0.4 0.2 0 vowel of "a" -0.2 -0.4 -0.6 0 0.005 0.01 0.015 0.02 time (s) Fig.1.1: Speech H. C. So Page 3 250 200 150 100 ECG 50 0 -50 0 0.5 1 1.5 2 2.5 time (s) Fig.1.2: ECG H. C. So Page 4 1 0.5 0 -0.5 transmitted pulse -1 0 0.2 0.4 0.6 0.8 1 time 1 0.5 0 -0.5 received pulse received t -1 0 0.2 0.4 0.6 0.8 1 time Fig.1.3: Transmitted & received radar waveforms H. C. So Page 5 Radar transceiver sends a 1-D sinusoidal pulse at time 0 It then receives echo reflected by an object at a range of Reflected signal is noisy and has a time delay of which corresponds to round trip propagation time of radar pulse Given the signal propagation speed, denoted by , is simply related to as: (1.1) As a result, the radar pulse contains the object range information H. -

Finite Impulse Response (FIR) Digital Filters (II) Ideal Impulse Response Design Examples Yogananda Isukapalli

Finite Impulse Response (FIR) Digital Filters (II) Ideal Impulse Response Design Examples Yogananda Isukapalli 1 • FIR Filter Design Problem Given H(z) or H(ejw), find filter coefficients {b0, b1, b2, ….. bN-1} which are equal to {h0, h1, h2, ….hN-1} in the case of FIR filters. 1 z-1 z-1 z-1 z-1 x[n] h0 h1 h2 h3 hN-2 hN-1 1 1 1 1 1 y[n] Consider a general (infinite impulse response) definition: ¥ H (z) = å h[n] z-n n=-¥ 2 From complex variable theory, the inverse transform is: 1 n -1 h[n] = ò H (z)z dz 2pj C Where C is a counterclockwise closed contour in the region of convergence of H(z) and encircling the origin of the z-plane • Evaluating H(z) on the unit circle ( z = ejw ) : ¥ H (e jw ) = åh[n]e- jnw n=-¥ 1 p h[n] = ò H (e jw )e jnwdw where dz = jejw dw 2p -p 3 • Design of an ideal low pass FIR digital filter H(ejw) K -2p -p -wc 0 wc p 2p w Find ideal low pass impulse response {h[n]} 1 p h [n] = H (e jw )e jnwdw LP ò 2p -p 1 wc = Ke jnwdw 2p ò -wc Hence K h [n] = sin(nw ) n = 0, ±1, ±2, …. ±¥ LP np c 4 Let K = 1, wc = p/4, n = 0, ±1, …, ±10 The impulse response coefficients are n = 0, h[n] = 0.25 n = ±4, h[n] = 0 = ±1, = 0.225 = ±5, = -0.043 = ±2, = 0.159 = ±6, = -0.053 = ±3, = 0.075 = ±7, = -0.032 n = ±8, h[n] = 0 = ±9, = 0.025 = ±10, = 0.032 5 Non Causal FIR Impulse Response We can make it causal if we shift hLP[n] by 10 units to the right: K h [n] = sin((n -10)w ) LP (n -10)p c n = 0, 1, 2, …. -

Signals and Systems Lecture 8: Finite Impulse Response Filters

Signals and Systems Lecture 8: Finite Impulse Response Filters Dr. Guillaume Ducard Fall 2018 based on materials from: Prof. Dr. Raffaello D’Andrea Institute for Dynamic Systems and Control ETH Zurich, Switzerland G. Ducard 1 / 46 Outline 1 Finite Impulse Response Filters Definition General Properties 2 Moving Average (MA) Filter MA filter as a simple low-pass filter Fast MA filter implementation Weighted Moving Average Filter 3 Non-Causal Moving Average Filter Non-Causal Moving Average Filter Non-Causal Weighted Moving Average Filter 4 Important Considerations Phase is Important Differentiation using FIR Filters Frequency-domain observations Higher derivatives G. Ducard 2 / 46 Finite Impulse Response Filters Moving Average (MA) Filter Definition Non-Causal Moving Average Filter General Properties Important Considerations Outline 1 Finite Impulse Response Filters Definition General Properties 2 Moving Average (MA) Filter MA filter as a simple low-pass filter Fast MA filter implementation Weighted Moving Average Filter 3 Non-Causal Moving Average Filter Non-Causal Moving Average Filter Non-Causal Weighted Moving Average Filter 4 Important Considerations Phase is Important Differentiation using FIR Filters Frequency-domain observations Higher derivatives G. Ducard 3 / 46 Finite Impulse Response Filters Moving Average (MA) Filter Definition Non-Causal Moving Average Filter General Properties Important Considerations FIR filters : definition The class of causal, LTI finite impulse response (FIR) filters can be captured by the difference equation M−1 y[n]= bku[n − k], Xk=0 where 1 M is the number of filter coefficients (also known as filter length), 2 M − 1 is often referred to as the filter order, 3 and bk ∈ R are the filter coefficients that describe the dependence on current and previous inputs. -

Windowing Techniques, the Welch Method for Improvement of Power Spectrum Estimation

Computers, Materials & Continua Tech Science Press DOI:10.32604/cmc.2021.014752 Article Windowing Techniques, the Welch Method for Improvement of Power Spectrum Estimation Dah-Jing Jwo1, *, Wei-Yeh Chang1 and I-Hua Wu2 1Department of Communications, Navigation and Control Engineering, National Taiwan Ocean University, Keelung, 202-24, Taiwan 2Innovative Navigation Technology Ltd., Kaohsiung, 801, Taiwan *Corresponding Author: Dah-Jing Jwo. Email: [email protected] Received: 01 October 2020; Accepted: 08 November 2020 Abstract: This paper revisits the characteristics of windowing techniques with various window functions involved, and successively investigates spectral leak- age mitigation utilizing the Welch method. The discrete Fourier transform (DFT) is ubiquitous in digital signal processing (DSP) for the spectrum anal- ysis and can be efciently realized by the fast Fourier transform (FFT). The sampling signal will result in distortion and thus may cause unpredictable spectral leakage in discrete spectrum when the DFT is employed. Windowing is implemented by multiplying the input signal with a window function and windowing amplitude modulates the input signal so that the spectral leakage is evened out. Therefore, windowing processing reduces the amplitude of the samples at the beginning and end of the window. In addition to selecting appropriate window functions, a pretreatment method, such as the Welch method, is effective to mitigate the spectral leakage. Due to the noise caused by imperfect, nite data, the noise reduction from Welch’s method is a desired treatment. The nonparametric Welch method is an improvement on the peri- odogram spectrum estimation method where the signal-to-noise ratio (SNR) is high and mitigates noise in the estimated power spectra in exchange for frequency resolution reduction. -

Transformations for FIR and IIR Filters' Design

S S symmetry Article Transformations for FIR and IIR Filters’ Design V. N. Stavrou 1,*, I. G. Tsoulos 2 and Nikos E. Mastorakis 1,3 1 Hellenic Naval Academy, Department of Computer Science, Military Institutions of University Education, 18539 Piraeus, Greece 2 Department of Informatics and Telecommunications, University of Ioannina, 47150 Kostaki Artas, Greece; [email protected] 3 Department of Industrial Engineering, Technical University of Sofia, Bulevard Sveti Kliment Ohridski 8, 1000 Sofia, Bulgaria; mastor@tu-sofia.bg * Correspondence: [email protected] Abstract: In this paper, the transfer functions related to one-dimensional (1-D) and two-dimensional (2-D) filters have been theoretically and numerically investigated. The finite impulse response (FIR), as well as the infinite impulse response (IIR) are the main 2-D filters which have been investigated. More specifically, methods like the Windows method, the bilinear transformation method, the design of 2-D filters from appropriate 1-D functions and the design of 2-D filters using optimization techniques have been presented. Keywords: FIR filters; IIR filters; recursive filters; non-recursive filters; digital filters; constrained optimization; transfer functions Citation: Stavrou, V.N.; Tsoulos, I.G.; 1. Introduction Mastorakis, N.E. Transformations for There are two types of digital filters: the Finite Impulse Response (FIR) filters or Non- FIR and IIR Filters’ Design. Symmetry Recursive filters and the Infinite Impulse Response (IIR) filters or Recursive filters [1–5]. 2021, 13, 533. https://doi.org/ In the non-recursive filter structures the output depends only on the input, and in the 10.3390/sym13040533 recursive filter structures the output depends both on the input and on the previous outputs. -

System Identification and Power Spectrum Estimation

182 IEEE TRANSACTIONS ON ACOUSTICS, SPEECH, AND SIGNAL PROCESSING, VOL. ASSP-27, NO. 2, APRIL 1979 Short-TimeFourier Analysis Techniques for FIR System Identification and Power Spectrum Estimation LAWRENCER. RABINER, FELLOW, IEEE, AND JONT B. ALLEN, MEMBER, IEEE Abstract—A wide variety of methods have been proposed for system F[çb] modeling and identification. To date, the most successful of these L = length of w(n) methods have been time domain procedures such as least squares analy- sis, or linear prediction (ARMA models). Although spectral techniques N= length ofDFTF[] have been proposed for spectral estimation and system identification, N' = number of data points the resulting spectral and system estimates have always been strongly N1 = lower limit on sum affected by the analysis window (biased estimates), thereby reducing N7 upper limit on sum the potential applications of this class of techniques. In this paper we M = length of h propose a novel short-time Fourier transform analysis technique in M = estimate of M which the influences of the window on a spectral estimate can essen- tially be removed entirely (an unbiased estimator) by linearly combin- h(n) = systems impulse response ing biased estimates. As a result, section (FFT) lengths for analysis can h(n) = estimate of h(n) be made as small as possible, thereby increasing the speed of the algo- F[.] = Fourier transform operator rithm without sacrificing accuracy. The proposed algorithm has the F'' [] = inverse Fourier transform important property that as the number of samples used in the estimate q1 = number of 0 diagonals below main increases, the solution quickly approaches the least squares (theoreti- cally optimum) solution. -

Lecture 15- Impulse Reponse and FIR Filter

In this lecture, we will learn about: If we apply an impulse at the input of a system, the output response is known as the 1. Impulse response of a discrete system and what it means. system’s impulse response: h(t) for continuous time, and h[n] of discrete time. 2. How impulse response can be used to determine the output of the system given We have demonstrated in Lecture 3 that the Fourier transform of a unit impulse is a its input. constant (of 1), meaning that an impulse contains ALL frequency components. 3. The idea behind convolution. Therefore apply an impulse to the input of a system is like applying ALL frequency 4. How convolution can be applied to moving average filter and why it is called a signals to the system simultaneously. Finite Impulse Response (FIR) filter. Furthermore, since integrating a unit impulse gives us a unit step, we can integrate 5. Frequency spectrum of the moving average filter the impulse response of a system, and we can obtain it’s step response. 6. The idea of recursive or Infinite Impulse Response (IIR) filter. In other words, the impulse response of a system completely specify and I will also introduce two new packages for the Segway proJect: characterise the response of the system. 1. mic.py – A Python package to capture data from the microphone So here are two important lessons: 2. motor.py – A Python package to drive the motors 1. Impulse response h(t) or h[n] characterizes a system in the time-domain. -

Construction of Finite Impulse Wavelet Filter for Partial Discharge Localisation Inside a Transformer Winding

2013 Electrical Insulation Conference, Ottowa, Onterio, Canada, 2 to 5 June 2013 Construction of Finite Impulse Wavelet Filter for Partial Discharge Localisation inside a Transformer Winding M. S. Abd Rahman1, P. Rapisarda2 and P. L. Lewin1 1The Tony Davies High Voltage Laboratory, University of Southampton, SO17 1BJ, UK 2Communications, Signal Processing and Control, University of Southampton, SO17 1BJ, UK Email: [email protected] Abstract- In high voltage (H.V.) plant, ageing processes can strategies [1]. Generally, timed-based preventative occur in the insulation system which are totally unavoidable and maintenance is performed periodically regardless of asset ultimately limit the operational life of the plant. Ultimately, condition which leads to higher operational costs. In order to partial discharge (PD) activity can start to occur at particular save maintenance costs, general CM practice is moving from a points within the insulation system. Operational over stressing and defects introduced during manufacture may also cause PD time-based approach to on-line based on specially condition activity and the presence of this activity if it remains untreated assessment [2,3]. Therefore, partial discharge condition will lead to the development of accelerated degradation processes monitoring for transformers and also PD source location along until eventually there may be catastrophic failure. Therefore, a transformer winding have become important research areas partial discharge condition monitoring of valuable HV plant such that aim to provide asset health information, enabling as a transformers and in particular along a transformer winding maintenance and replacement processes to be carried out is an important research area as this may ultimately provide effectively. -

Digital Filters in Radiation Detection and Spectroscopy

Digital Filters in Radiation Detection and Spectroscopy Digital Radiation Measurement and Spectroscopy NE/RHP 537 1 Digital Radiation Measurement and Spectroscopy, Oregon State University, Abi Farsoni Classical and Digital Spectrometers •Classical Spectrometer Analog Detector Preamplifier Shaping Multichannel Histogram Amplifier Analyzer Memory •Digital Spectrometer High-Speed Digital Pulse Histogram Detector Preamplifier ADC Processing Memory 2 Digital Radiation Measurement and Spectroscopy, Oregon State University, Abi Farsoni Digital Spectrometers: Advantages • Pulse processing algorithm is easy to edit • No bulky analog electronics • Post-processing •Digital Spectrometer High-Speed Digital Pulse Histogram • Digital pulse shaping Detector Preamplifier ADC Processing Memory • More cost-effective • The algorithm is stable and reliable, no thermal noise or other fluctuations • Effects, such as pile-up can be corrected or eliminated at the processing level • Signal capture and processing can be based more easily on coincidence criteria between different detectors or different parts of the same detector • Disadvantage: Lack of expert in (Digital Systems + Nuclear Spectroscopy) 3 Digital Radiation Measurement and Spectroscopy, Oregon State University, Abi Farsoni Signal Pulses From Scintillation Detectors Integrating Preamp Rf Anode Cf Preamp output output Scintillation Detector NaI PMT 2 A 1 Vmax 4 Digital Radiation Measurement and Spectroscopy, Oregon State University, Abi Farsoni Digital Spectrometers: Digital Pulse Processor (Hardware) -

Interpolated FIR Filters

1 Interpolated FIR Filters Kyle S. Marcolini, Student, University of Miami Abstract—The idea of interpolated finite impulse response III. IFIR DESIGN filters (IFIR) is a technique devised in the 1980s used for designing narrowband filters. Typically, FIR can be of high order IFIR filters were introduced to help with this problem of to achieve the same results as their infinite impulse response normal FIR filters. To achieve a narrowband filter, FIR filters (IIR) counterparts, especially considering filters that have a steep will indefinitely be very high order. IFIR filters begin with a L transition band. IFIR filters can be implemented in place of FIR model FIR filter, FM(z ), but with an introduced stretching, or filters in this case, as they will be lower order overall and interpolation factor, L, increasing the width of the passband. computational efficient. This study will give an overview of IFIR As the passband width increases, the order of the filter filters, improvements made on them, as well a advantages and disadvantages of these enhancements. decreases by L. This model filter is then run through an image filter, G(z), Index Terms—interpolated, impulse response, infinite, finite, which narrows out the passband by attenuating undesired narrowband, order redundancies, creating a lower-order, FIR narrowband filter. The use of low-order cascaded filters in this design results in lowering the order of a single FIR filter, saving computation I. INTRODUCTION because of the number of extra multipliers that are not needed. WO types of filters used in modern filtering are finite The system flow diagram is shown in Figure 1 [1]. -

The Fast Wavelet Transform and Its Application to Electroencephalography: a Study of Schizophrenia

The Fast Wavelet Transform and its Application to Electroencephalography: A Study of Schizophrenia Prepared by: Cullen Jon Navarre Roth May 7, 2014 ACKNOWLEDGMENTS I would like to thank the National Science Foundation for its support through the Fall of the academic year of 2014 ―Mentoring through Critical Transition Points‖ (MCTP) grant DMS 1148001. I would also like to thank the Undergraduate Committee, especially Professor Monika Nitsche in her dual role as Chair of the Undergraduate Committee and PI of the MCPT grant. I would also like to thank Professor Christina Pereyra, Dr. David Bridwell, Dr. NavinCota Gupta, Dr. Vince Calhoun, and Dr. Maggie Werner-Washburne for their support and encouragement. TABLE OF CONTENTS Table of Contents Chapter 1 Introduction ......................................................................................... 1 Chapter 2 Preliminaries ........................................................................................ 2 2.1. The Wavelet Basis ............................................................................... 2 2.2. Orthogonal Multiresolution Analysis (MRA): .................................... 3 Chapter 3 Scaling Equation and Conjugate Mirror Conditions ........................... 8 3.1. The Scaling Equation ........................................................................... 8 3.2. Conjugate Mirror Filters .................................................................... 11 3.3. The Wavelet and Conjugate Mirror Filters ........................................ 13 Chapter