Microcontrollers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Oriented Conferences Four Solutions

Delivering Solutions and Technology to the World’s Design Engineering Community Four Solutions- Oriented Conferences • System-on-Chip Design Conference • IP World Forum • High-Performance System Design Conference • Wireless and Optical Broadband Design Conference Special Technology Focus Areas January 29 – February 1, 2001 • Internet and Information Exhibits: January 30–31, 2001 Appliance Design Santa Clara Convention Center • Embedded Design Santa Clara, California • RF, Optical, and Analog Design NEW! • IEC Executive Forum International Engineering Register by January 5 and Consortium save $100 – and be entered to win www.iec.org a Palm Pilot! Practical Design Solutions Practical design-engineering solutions presented by practicing engineers—The DesignCon reputation of excellence has been built largely by the practical nature of its sessions. Design engineers hand selected by our team of professionals provide you with the best electronic design and silicon-solutions information available in the industry. DesignCon provides attendees with DesignCon has an established reputation for the high design solutions from peers and professionals. quality of its papers and its expert-level speakers from Silicon Valley and around the world. Each year more than 100 industry pioneers bring to light the design-engineering solutions that are on the leading edge of technology. This elite group of design engineers presents unique case studies, technology innovations, practical techniques, design tips, and application overviews. Who Should Attend Any professionals who need to stay on top of current information regarding design-engineering theories, The most complete educational experience techniques, and application strategies should attend this in the industry conference. DesignCon attracts engineers and allied The four conference options of DesignCon 2001 provide a professionals from all levels and disciplines. -

Zilog’S Ez80acclaim!™ Product Family, Which Offers On-Chip Flash Versions of Zilog’S Ez80® • 3.0–3.6 V Supply Voltage with 5 V Tolerant Inputs Processor Core

eZ80Acclaim!™ Flash Microcontrollers eZ80F91 Product Brief PB013502-0104 Product Block Diagram • I2C with independent clock rate generator • SPI with independent clock rate generator eZ80F91 MCU • Four Counter/Timers with prescalers supporting event counting, input capture, output compare, and 256 KB Flash + 32-Bit GPIO PWM modes 512 B Flash • Watch-Dog Timer with internal RC clocking 10/100 Mbps option 8KB SRAM Ethernet MAC • Real-time clock with on-chip 32kHz oscillator, 8KB Frame Buffer selectable 50/60Hz input, and separate RTC_VDD pin for battery backup. Infrared 2 • Glueless external memory interface with 4 Chip- Encoder/ 2 UART I C SPI Selects/Wait-State Generators and external WAIT Decoder input pin. Supports Intel and Motorola buses. Real-Time • JTAG Interface supporting emulation features 4 PRT WDT Clock • Low-power PLL and on-chip oscillator • Programmable-priority vectored interrupts, non- 4 CS JTAG ZDI PLL maskable interrupts, and interrupt controller +WSG • New DMA-like eZ80® CPU instructions • Power management features supporting HALT/ Features SLEEP modes and selective peripheral power- down controls The eZ80F91 microcontroller is a member of • 144-pin BGA or 144-pin LQFP package ZiLOG’s eZ80Acclaim!™ product family, which offers on-chip Flash versions of ZiLOG’s eZ80® • 3.0–3.6 V supply voltage with 5 V tolerant inputs processor core. The eZ80F91 offers the following • Operating Temperature Ranges: features: – Standard: 0ºC to +70ºC • 50MHz High-Performance eZ80® CPU – Extended: –40ºC to +105ºC • 256 KB Flash Program Memory plus extra 512B device configuration Flash memory General Description • 32 bits of General-Purpose I/O The eZ80F91 device is an industry first, featuring a • 16K B total on-chip high-speed SRAM: high-performance 8-bit microcontroller with an integrated 10/100 BaseT Ethernet Media Access – 8KB for general-purpose use controller (EMAC). -

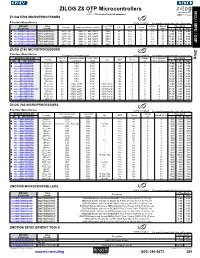

ZILOG Z8 OTP Microcontrollers MCU / MPU / DSP This Product Is Rohs Compliant

ZILOG Z8 OTP Microcontrollers DSP MPU / MCU / This product is RoHS compliant. ZILOG EZ80 MICROPROCESSORS ♦ Surface Mount Device For quantities greater than listed, call for quote. MOUSER Zilog Core CPU Voltage Speed Price Each Package Communications Controller I/O WDT Timers STOCK NO. Part No. Used (V) (MHz) 1 25 100 ♦ 692-EZ80L92AZ020EG EZ80L92AZ020EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 9.29 9.10 8.63 ♦ 692-EZ80L92AZ020SG EZ80L92AZ020SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 8.08 7.78 7.50 ♦ 692-EZ80L92AZ050EG EZ80L92AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 10.21 9.75 9.49 ♦ 692-EZ80L92AZ050SG EZ80L92AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 8.89 8.54 8.26 ♦ 692-EZ80190AZ050SG EZ80190AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 12.03 11.59 11.17 ♦ 692-EZ80190AZ050EG EZ80190AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 13.82 13.28 12.84 ZILOG Z180 MICROPROCESSORS Zilog ♦Surface Mount Device *See above for development tools. For quantities greater than listed, call for quote. MOUSER STOCK NO. Speed Communications Core CPU Voltage Development Price Each Package I/O WDT Timers Mfr. Mfr. Part No. (MHz) Controller Used (V) Tools Available 1 25 100 ♦ 692-Z8018006VSG PLCC-68 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 ♦ 692-Z8018006VEG PLCC-68 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018006PSG DIP-64 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 692-Z8018006PEG DIP-64 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018008PSG DIP-64 8 CPU Z180 - No 2 5 - 8.75 7.38 6.25 ♦ 692-Z8018008VSG -

Architecture of 8051 & Their Pin Details

SESHASAYEE INSTITUTE OF TECHNOLOGY ARIYAMANGALAM , TRICHY – 620 010 ARCHITECTURE OF 8051 & THEIR PIN DETAILS UNIT I WELCOME ARCHITECTURE OF 8051 & THEIR PIN DETAILS U1.1 : Introduction to microprocessor & microcontroller : Architecture of 8085 -Functions of each block. Comparison of Microprocessor & Microcontroller - Features of microcontroller -Advantages of microcontroller -Applications Of microcontroller -Manufactures of microcontroller. U1.2 : Architecture of 8051 : Block diagram of Microcontroller – Functions of each block. Pin details of 8051 -Oscillator and Clock -Clock Cycle -State - Machine Cycle -Instruction cycle –Reset - Power on Reset - Special function registers :Program Counter -PSW register -Stack - I/O Ports . U1.3 : Memory Organisation & I/O port configuration: ROM RAM - Memory Organization of 8051,Interfacing external memory to 8051 Microcontroller vs. Microprocessors 1. CPU for Computers 1. A smaller computer 2. No RAM, ROM, I/O on CPU chip 2. On-chip RAM, ROM, I/O itself ports... 3. Example:Intel’s x86, Motorola’s 3. Example:Motorola’s 6811, 680x0 Intel’s 8051, Zilog’s Z8 and PIC Microcontroller vs. Microprocessors Microprocessor Microcontroller 1. CPU is stand-alone, RAM, ROM, I/O, timer are separate 1. CPU, RAM, ROM, I/O and timer are all on a single 2. designer can decide on the chip amount of ROM, RAM and I/O ports. 2. fix amount of on-chip ROM, RAM, I/O ports 3. expansive 3. for applications in which 4. versatility cost, power and space are 5. general-purpose critical 4. single-purpose uP vs. uC – cont. Applications – uCs are suitable to control of I/O devices in designs requiring a minimum component – uPs are suitable to processing information in computer systems. -

Data Acquisition

#147 October 2002 www.circuitcellar.com CIRCUIT CELLAR® THE MAGAZINE FOR COMPUTER APPLICATIONS DATA ACQUISITION 2-D Or Not 2-D Solar-Powered Robot The LED Alternative Mad DashWWW.GiURUMELE.Hi2.RO For Flash Cash Contest Primer 10> 7925274 75349 $4.95 U.S. ($5.95 Canada) WWW.GiURUMELE.Hi2.RO WWW.GiURUMELE.Hi2.RO Digital Oscilloscopes • 2 Channel Digital Oscilloscope DSO-2102S $525 • 100 MSa/s max single shot rate DSO-2102M $650 • 32K samples per channel Each includes Oscilloscope, • Advanced Triggering Probes, Interface Cable, Power • Only 9 oz and 6.3” x 3.75” x 1.25” Adapter, and software for • Small, Lightweight, and Portable Win95/98, WinNT, Win2000 • Parallel Port interface to PC and DOS. • Advanced Math options • FFT Spectrum Analyzer options Logic Analyzers • 40 to 160 channels • 24 Channel Logic Analyzer • up to 500 MSa/s • 100MSa/S max sample rate • Variable Threshold • Variable Threshold Voltage • 8 External Clocks • Large 128k Buffer • 16 Level Triggering • Small, Lightweight and Portable • up to 512KWWW.GiURUMELE.Hi2.RO samples/ch • Only 4 oz and 4.75” x 2.75” x 1” • Optional Parallel Interface • Parallel Port Interface to PC • Optional 100 MSa/s Pattern Generator • Trigger Out • Windows 95/98 Software LA4240-32K (200MHz, 40CH) $1350 LA4280-32K (200MHz, 80CH) $2000 LA2124-128K (100MSa/s, 24CH) LA4540-128K (500MHz, 40CH) $1900 Clips, Wires, Interface Cable, AC LA4580-128K (500MHz, 80CH) $2800 Adapter and Software $800 LA45160-128K (500MHz, 160CH) $7000 All prices include Pods and Software www.LinkIns4.com Link Instruments • 369 Passaic Ave • Suite 100 • Fairfield, NJ 07004 • (973) 808-8990 • Fax (973) 808-8786 WWW.GiURUMELE.Hi2.RO TASK MANAGER EDITORIAL DIRECTOR/FOUNDER CHIEF FINANCIAL OFFICER Be a Contender Steve Ciarcia Jeannette Ciarcia MANAGING EDITOR Jennifer Huber CUSTOMER SERVICE Elaine Johnston TECHNICAL EDITOR C.J. -

Important Notice Dear Customer, on 7 February 2017 The

Important notice Dear Customer, On 7 February 2017 the former NXP Standard Product business became a new company with the tradename Nexperia. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below. Instead of http://www.nxp.com, http://www.philips.com/ or http://www.semiconductors.philips.com/, use http://www.nexperia.com Instead of [email protected] or [email protected], use [email protected] (email) Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below: - © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved Should be replaced with: - © Nexperia B.V. (year). All rights reserved. If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via [email protected]). Thank you for your cooperation and understanding, Kind regards, Team Nexperia PMN27XPE 20 V, single P-channel Trench MOSFET 20 September 2012 Product data sheet 1. Product profile 1.1 General description P-channel enhancement mode Field-Effect Transistor (FET) in a small SOT457 (SC-74) Surface-Mounted Device (SMD) plastic package using Trench MOSFET technology. 1.2 Features and benefits • Fast switching • Trench MOSFET technology • 2 kV ESD protection 1.3 Applications • Relay driver • High-speed line driver • High-side loadswitch • Switching circuits 1.4 Quick reference data Table 1. -

Embedded Systems and Internet of Things (Iots) - Challenges in Teaching the ARM Controller in the Classroom

Paper ID #20286 Embedded Systems and Internet of Things (IoTs) - Challenges in Teaching the ARM Controller in the Classroom Prof. Dhananjay V. Gadre, Netaji Subhas Institute of Technology Dhananjay V. Gadre (New Delhi, India) completed his MSc (electronic science) from the University of Delhi and M.Engr (computer engineering) from the University of Idaho, USA. In his professional career of more than 27 years, he has taught at the SGTB Khalsa College, University of Delhi, worked as a scientific officer at the Inter University Centre for Astronomy and Astrophysics (IUCAA), Pune, and since 2001, has been with the Electronics and Communication Engineering Division, Netaji Subhas Institute of Technology (NSIT), New Delhi, currently as an associate professor. He directs two open access laboratories at NSIT, namely Centre for Electronics Design and Technology (CEDT) and TI Centre for Embedded Product Design (TI-CEPD). Professor Gadre is the author of several professional articles and five books. One of his books has been translated into Chinese and another one into Greek. His recent book ”TinyAVR Microcontroller Projects for the Evil Genius”, published by McGraw Hill International consists of more than 30 hands-on projects and has been translated into Chinese and Russian. He is a licensed radio amateur with a call sign VU2NOX and hopes to design and build an amateur radio satellite in the near future. Dr. Ramesh S. Gaonkar, SUNY-PCC and IITGN Ramesh Gaonkar, Ph.D., Professor Emeritus, SUNY OCC, (Syracuse, NY) was a professor in Electrical Technology, and presently, he is teaching as a Visiting Professor at Indian Institute of Technology (IIT), Gandhinagar, India. -

Natalia Nikolaevna Shusharina Maxin.Pmd

BIOSCIENCES BIOTECHNOLOGY RESEARCH ASIA, September 2016. Vol. 13(3), 1523-1536 Development of the Brain-computer Interface Based on the Biometric Control Channels and Multi-modal Feedback to Provide A Human with Neuro-electronic Systems and Exoskeleton Structures to Compensate the Motor Functions Natalia Nikolaevna Shusharina1, Evgeny Anatolyevich Bogdanov1, Stepan Aleksandrovich Botman1, Ekaterina Vladimirovna Silina2, Victor Aleksandrovich Stupin3 and Maksim Vladimirovich Patrushev1 1Immanuel Kant Baltic Federal University (IKBFU), Nevskogo Str., 14, Kaliningrad, 236041, Russia 2I.M. Sechenov First Moscow State Medical University (First MSMU), Trubetskaya str, 8, Moscow, 119991, Russia 3Pirogov´s Russian National Research Medical University (RNRMU), Ostrovityanova str, 1, Moscow, 117997, Russia http://dx.doi.org/10.13005/bbra/2295 (Received: 15 June 2016; accepted: 05 August 2016) The aim of this paper is to create a multi-functional neuro-device and to study the possibilities of long-term monitoring of several physiological parameters of an organism controlled by brain activity with transmitting the data to the exoskeleton. To achieve this goal, analytical review of modern scientific-and-technical, normative, technical, and medical literature involving scientific and technical problems has been performed; the research area has been chosen and justified, including the definition of optimal electrodes and their affixing to the body of the patient, the definition of the best suitable power source and its operation mode, the definition of the best suitable useful signal amplifiers, and a system of filtering off external noises. A neuro-device mock-up has been made for recognizing electrophysiological signals and transmitting them to the exoskeleton, also the software has been written. -

Portability Techniques for Embedded Systems Data Management

Portability Techniques for Embedded Systems Data Management McObject LLC st 33309 1 Way South Suite A-208 Federal Way, WA 98003 Phone: 425-888-8505 E-mail: [email protected] www.mcobject.com Copyright 2020, McObject LLC Whether an embedded systems database is developed for a specific application or as a commercial product, portability matters. Most embedded data management code is still “homegrown,” and when external forces drive an operating system or hardware change, data management code portability saves significant development time. This is especially important since increasingly, hardware’s lifespan is shorter than firmware’s. For database vendors, compatibility with the dozens of hardware designs, operating systems and compilers used in embedded systems provides a major marketing advantage. For real-time embedded systems, database code portability means more than the ability to compile and execute on different platforms: portability strategies also tie into performance. Software developed for a specific OS, hardware platform and compiler often performs poorly when moved to a new environment, and optimizations to remedy this are very time-consuming. Truly portable embedded systems data management code carries its optimization with it, requiring the absolute minimum adaptation to deliver the best performance in new environments. Using Standard C Writing portable code traditionally begins with a commitment to use only ANSI C. But this is easier said than done. Even code written with the purest ANSI C intentions frequently makes assumptions about the target hardware and operating environment. In addition, programmers often tend to use available compiler extensions. Many of the extensions – prototypes, stronger type- checking, etc, – enhance portability, but others may add to platform dependencies. -

2 XII December 2014

2 XII December 2014 www.ijraset.com Volume 2 Issue XII, December 2014 ISSN: 2321-9653 International Journal for Research in Applied Science & Engineering Technology (IJRASET) Overview and Comparative Study of Different Microcontrollers Rajratna Khadse1, Nitin Gawai2, Bagwan M. Faruk3 1Assist.Professor, Electronics Engineering Department, RCOEM, Nagpur 2,3Assist.Professor, E & Tc Engineering Department, JDIET, Yavatmal Abstract—A microcontroller is a small and low-cost computer built for the purpose of dealing with specific tasks, such as displaying information on seven segment display at railway platform or receiving information from a television’s remote control. Microcontrollers are mainly used in products that require a degree of control to be exerted by the user. Today various types of microcontrollers are available in market with different word lengths such as 8bit, 16bit, 32bit, and microcontrollers. Microcontroller is a compressed microcomputer manufactured to control the functions of embedded systems in office machines, robots, home appliances, motor vehicles, and a number of other gadgets. Therefore in today’s technological world lot of things done with the help of Microcontroller. Depending upon the applications we have to choose particular types of Microcontroller. The aim of this paper to give the basic information of microcontroller and comparative study of 8051 Microcontroller, ARM Microcontroller, PIC Microcontroller and AVR Microcontroller Keywords— Microcontroller, Memory, Instruction, cycle, bit, architecture I. INTRODUCTION Microcontrollers have directly or indirectly impact on our daily life. Usually, But their presence is unnoticed at most of the places like: At supermarkets in Cash Registers, Weighing Scales, Video games ,security system , etc. At home in Ovens, Washing Machines, Alarm Clocks, paging, VCR, LASER Printers, color printers etc. -

6800/68000 Cmos

Click Here to Request a Large Quantity Quote 6800/68000 CMOS Jameco Manufacturer Manufacturer Description Package Product Type Organization Family Application Price 1 Part # Part # 130366 Major Brands 00130366 420 PIECE DIODE REFILL PACKAGE $29.95 130374 Major Brands 00130374 560 Piece Transistor Kit Refill Package $54.95 130391 Major Brands 00130391 420 Piece 74LS Logic Series Refill Package $214.95 130403 Major Brands 00130403 300 PIECE CD4000 SERIES REFILL PACKAGE $74.95 130411 Major Brands 00130411 480 PIECE LINEAR SERIES REFILL PACKAGE $164.95 1542961 Vishay 1.5KE16CA TVS Diode 22.5V Clamp 66.7A Ipp Through Hole 1500W DO-201 $0.49 1.5KE 2303247 Major Brands 1.5KE8.2C TVS Diode 12.1V Clamp 125.6A Ipp DO-201 DO-201 $0.59 35924 Major Brands 1N1188 Diode 1N1188 400 VOLT 35 AMP SILICON RECTIFIER DO-5 Stud Rectifier $3.95 2197610 Kest Parts 1N1190A Diode 1N1190A Power Silicon Rectifier 40 Amp 600V DO-5 DO-5 Stud Rectifier $4.95 2197628 Kest Parts 1N1190RA Diode 1N1190RA 40A 600V Power Silicon Rectifier DO-5 Stud Rectifier $4.95 2287679 Major Brands 1N1202A 200V 12A Rectifier Stud Mount DO-203 DO-203 Stud Rectifier $1.95 35941 Major Brands 1N270 Diode 1N270 Germanium 1 Volt @ 200Ma DO-7 General $1.19 Purpose 2220533 Major Brands 1N34A Diode 1N34A General Purpose Germanium DO-7 General $1.95 Purpose 35975 Major Brands 1N4001 Diode 1N4001 50 Volt 1 Amp General Purpose Rectifier DO-41 Standard $0.09 76961 Major Brands 1N4002 Diode 1N4002 100 Volt 1A DO-41 package DO-41 Standard $0.09 76970 Major Brands 1N4003 Diode 1N4003 Rectifier 200 Volt -

152F580552eb358625881dd680

Products Catalog Index PART NO. MANUFACTURER DESCRIPTION URL PRICE Q65112A2615 OSRAM OPTO Q65112A2615 http://www.searchdatasheet.com/Q65112A2615-datasheet.html QUOTE SEMICONDUCTORS XR33053ID-F EXAR Transceiver 1Mbps 3.3V/5V http://www.searchdatasheet.com/XR33053ID-F-datasheet.html QUOTE 14-Pin SOIC N Tube Q65111A7362 OSRAM OPTO LED Uni-Color White 2-Pin http://www.searchdatasheet.com/Q65111A7362-datasheet.html QUOTE SEMICONDUCTORS SMD T/R EL-17-21UYC/S530-A2/TR8 EVERLIGHT EL-17-21UYC/S530-A2/TR8 http://www.searchdatasheet.com/EL-17-21UYC%2FS530-A2%2FTR8-datasheet.html QUOTE ELECTRONICS Q65112A2616 OSRAM OPTO Q65112A2616 http://www.searchdatasheet.com/Q65112A2616-datasheet.html QUOTE SEMICONDUCTORS Q65111A9950 OSRAM OPTO Q65111A9950 http://www.searchdatasheet.com/Q65111A9950-datasheet.html QUOTE SEMICONDUCTORS Q65112A2629 OSRAM OPTO Q65112A2629 http://www.searchdatasheet.com/Q65112A2629-datasheet.html QUOTE SEMICONDUCTORS Q65112A0819 OSRAM OPTO LED Uni-Color White 2-Pin http://www.searchdatasheet.com/Q65112A0819-datasheet.html QUOTE SEMICONDUCTORS CSMD EP Q65111A9208 OSRAM OPTO Q65111A9208 http://www.searchdatasheet.com/Q65111A9208-datasheet.html QUOTE SEMICONDUCTORS Q65111A8966 OSRAM OPTO Q65111A8966 http://www.searchdatasheet.com/Q65111A8966-datasheet.html QUOTE SEMICONDUCTORS RLR20C1201GMRE6 VISHAY Res Metal Film 1.2K Ohm http://www.searchdatasheet.com/RLR20C1201GMRE6-datasheet.html QUOTE 2% 0.5W(1/2W) ±100ppm/C 1% Epoxy AXL T/R EVMB Connect One Evaluation Master Kit with http://www.searchdatasheet.com/EVMB-datasheet.html QUOTE Semiconductors