Integration and Analysis of a 24.3Mhz FM Transmitter/Receiver System

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Toward a Large Bandwidth Photonic Correlator for Infrared Heterodyne Interferometry a first Laboratory Proof of Concept

A&A 639, A53 (2020) Astronomy https://doi.org/10.1051/0004-6361/201937368 & c G. Bourdarot et al. 2020 Astrophysics Toward a large bandwidth photonic correlator for infrared heterodyne interferometry A first laboratory proof of concept G. Bourdarot1,2, H. Guillet de Chatellus2, and J-P. Berger1 1 Univ. Grenoble Alpes, CNRS, IPAG, 38000 Grenoble, France e-mail: [email protected] 2 Univ. Grenoble Alpes, CNRS, LIPHY, 38000 Grenoble, France Received 19 December 2019 / Accepted 17 May 2020 ABSTRACT Context. Infrared heterodyne interferometry has been proposed as a practical alternative for recombining a large number of telescopes over kilometric baselines in the mid-infrared. However, the current limited correlation capacities impose strong restrictions on the sen- sitivity of this appealing technique. Aims. In this paper, we propose to address the problem of transport and correlation of wide-bandwidth signals over kilometric dis- tances by introducing photonic processing in infrared heterodyne interferometry. Methods. We describe the architecture of a photonic double-sideband correlator for two telescopes, along with the experimental demonstration of this concept on a proof-of-principle test bed. Results. We demonstrate the a posteriori correlation of two infrared signals previously generated on a two-telescope simulator in a double-sideband photonic correlator. A degradation of the signal-to-noise ratio of 13%, equivalent to a noise factor NF = 1:15, is obtained through the correlator, and the temporal coherence properties of our input signals are retrieved from these measurements. Conclusions. Our results demonstrate that photonic processing can be used to correlate heterodyne signals with a potentially large increase of detection bandwidth. -

Electronic Warfare Fundamentals

ELECTRONIC WARFARE FUNDAMENTALS NOVEMBER 2000 PREFACE Electronic Warfare Fundamentals is a student supplementary text and reference book that provides the foundation for understanding the basic concepts underlying electronic warfare (EW). This text uses a practical building-block approach to facilitate student comprehension of the essential subject matter associated with the combat applications of EW. Since radar and infrared (IR) weapons systems present the greatest threat to air operations on today's battlefield, this text emphasizes radar and IR theory and countermeasures. Although command and control (C2) systems play a vital role in modern warfare, these systems are not a direct threat to the aircrew and hence are not discussed in this book. This text does address the specific types of radar systems most likely to be associated with a modern integrated air defense system (lADS). To introduce the reader to EW, Electronic Warfare Fundamentals begins with a brief history of radar, an overview of radar capabilities, and a brief introduction to the threat systems associated with a typical lADS. The two subsequent chapters introduce the theory and characteristics of radio frequency (RF) energy as it relates to radar operations. These are followed by radar signal characteristics, radar system components, and radar target discrimination capabilities. The book continues with a discussion of antenna types and scans, target tracking, and missile guidance techniques. The next step in the building-block approach is a detailed description of countermeasures designed to defeat radar systems. The text presents the theory and employment considerations for both noise and deception jamming techniques and their impact on radar systems. -

AM Series AGILE MODULATOR

AM Series AGILE MODULATOR AM series is a family of frequency-agile analog audio/video modulators. AM-60-860, the flag-ship model, is available in NTSC C channels 2-135 (54-860 MHz), and the PAL B, G, and I channels in the same frequency range. A More economical models are available in NTSC for the frequency ranges 54-550 MHz, or 54-806 MHz. EAS (Emergency Alert System) is standard on all models. Stereo Audio, SAP (Secondary Audio Programming), and several other optional T features are also available. V Baseband Audio/Video P R O D U Modulated C Analog RF T S Ordering Information Model Stock # Description AM-60-860 59415A Frequency-agile Audio/Video Modulator, +60 dBmV, 54-860 MHz (NTSC) AM-60-806 59419 Frequency-agile Audio/Video Modulator, +60 dBmV, 54-806 MHz (NTSC) AM-60-550 59416 Frequency-agile Audio/Video Modulator, +60 dBmV, 54-550 MHz (NTSC) AM-45-550 59404 Frequency-agile Audio/Video Modulator, +45 dBmV, 54-550 MHz (NTSC) Options AM-OPT-02 BNC Video Input Connector AM-OPT-04 Sub-Band Output (Available with AM-60-550 only) AM-OPT-05 Integrated BTSC Stereo Audio AM-OPT-06 SAP Audio/ BTSC Stereo (Available with AM-60-860 only) products AM-OPT-07 Video AGC CATV AM-OPT-09 Balanced Audio Input, 600 Ohm (Standard on AM-60-860) Related Products Model Description AMCM Frequency-agile Audio/Video modulator, +45 dBmV, 54-860 MHz (NTSC & PAL), Twelve modulators in 2RU modulators freq. agile ACM Frequency-agile Audio/Video modulator, +45 dBmV, 54-806 MHz (NTSC only), Twelve modulators in 2RU MICM Fixed-channel Audio/Video modulator, +45 dBmV, 54-806 MHz (NTSC & PAL), Twelve modulators in 2RU www.blondertongue.com | 800-523-6049 76 Specifications Input Output Connector Connector: “F” Female Standard: “F” Female Impedance: 75 Ω Option 2: BNC Female Impedance: 75 Ω Return Loss: 12 dB Return Loss: 18 dB Frequency Range Video Input Level AM-60-860 Model: 54 to 860 MHz (NTSC CATV Ch. -

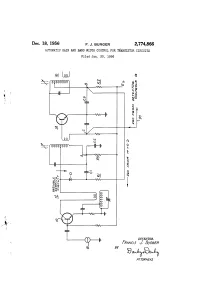

Dec. 18, 1956 . F. J. BURGER 2,774,866 Firancis. J. B/RGER

Dec. 18, 1956 . F. J. BURGER 2,774,866 AUTOMATIC GAIN AND BAND WIDTH CONTROL FORTRANSISTOR CIRCUITS Filed Jan. 30, 1956 s log 00 0 0-0 000 & S. l INVENTOR, firANCIS. J. B/RGER 9. BY alid. A77ORNEYs 2,774,866 United States Patent Office Patented Dec. 18, 1956 2 reduced gain conditions. In order to prevent such dis tortion some means is required to reduce the signal level 2,774,866 prior to its application to the first intermediate frequency stage. In addition to the distortion problem, as is known, AUTOMATIC GAN AND BAND WIDTH CONTROL 5 the band width of the intermediate frequency amplifier FORTRANSISTOR CIRCUITS varies as a function of the magnitude of the automatic Francis J. Burger, Leonia, N. J., assignior to Enuerson gain controi voltage. As the gain of the transistor is Radio & Phonograph Corporation, Jersey City, N. , reduced, the loading which it presents to the intermediate a corporation of New York frequency coils decreases, thus increasing the Q of the O circuit and narrowing the band width. There also results Application January 30, 1956, Serial No. 562,072 a change in reactive loading provided by the I. F. tran 6 Claims. (C. 250-20) sistor which causes the intermediate frequency coils to shift their frequency center to a higher value. The purpose of this invention is to provide a variable This invention relates to improvements in transistor damping system which will vary the primary damping circuits, particularly transistor radio receivers with re of the converter intermediate frequency coil as a func spect to means for providing automatic gain and band tion of the automatic gain control voltage. -

En 300 720 V2.1.0 (2015-12)

Draft ETSI EN 300 720 V2.1.0 (2015-12) HARMONISED EUROPEAN STANDARD Ultra-High Frequency (UHF) on-board vessels communications systems and equipment; Harmonised Standard covering the essential requirements of article 3.2 of the Directive 2014/53/EU 2 Draft ETSI EN 300 720 V2.1.0 (2015-12) Reference REN/ERM-TG26-136 Keywords Harmonised Standard, maritime, radio, UHF ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at http://portal.etsi.org/tb/status/status.asp If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

Detecting and Locating Electronic Devices Using Their Unintended Electromagnetic Emissions

Scholars' Mine Doctoral Dissertations Student Theses and Dissertations Summer 2013 Detecting and locating electronic devices using their unintended electromagnetic emissions Colin Stagner Follow this and additional works at: https://scholarsmine.mst.edu/doctoral_dissertations Part of the Electrical and Computer Engineering Commons Department: Electrical and Computer Engineering Recommended Citation Stagner, Colin, "Detecting and locating electronic devices using their unintended electromagnetic emissions" (2013). Doctoral Dissertations. 2152. https://scholarsmine.mst.edu/doctoral_dissertations/2152 This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact [email protected]. DETECTING AND LOCATING ELECTRONIC DEVICES USING THEIR UNINTENDED ELECTROMAGNETIC EMISSIONS by COLIN BLAKE STAGNER A DISSERTATION Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY in ELECTRICAL & COMPUTER ENGINEERING 2013 Approved by Dr. Steve Grant, Advisor Dr. Daryl Beetner Dr. Kurt Kosbar Dr. Reza Zoughi Dr. Bruce McMillin Copyright 2013 Colin Blake Stagner All Rights Reserved iii ABSTRACT Electronically-initiated explosives can have unintended electromagnetic emis- sions which propagate through walls and sealed containers. These emissions, if prop- erly characterized, enable the prompt and accurate detection of explosive threats. The following dissertation develops and evaluates techniques for detecting and locat- ing common electronic initiators. The unintended emissions of radio receivers and microcontrollers are analyzed. These emissions are low-power radio signals that result from the device's normal operation. -

Low-Noise Local Oscillator Design Techniques Using a DLL-Based Frequency Multiplier for Wireless Applications

Low-Noise Local Oscillator Design Techniques using a DLL-based Frequency Multiplier for Wireless Applications by George Chien B.S. (University of California, Los Angeles) 1993 M.S. (University of California, Berkeley) 1996 A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences in the GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY Committee in charge: Professor Paul R. Gray, Chair Professor Robert G. Meyer Professor Paul K. Wright Spring 2000 The dissertation of George Chien is approved: Professor Paul R. Gray, Chair Date Professor Robert G. Meyer Date Professor Paul K. Wright Date University of California, Berkeley Fall 1999 Low-Noise Local Oscillator Design Techniques using a DLL-based Frequency Multiplier for Wireless Applications Copyright 2000 by George Chien Abstract Low-Noise Local Oscillator Design Techniques using a DLL-based Frequency Multiplier for Wireless Applications by George Chien Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Paul R. Gray, Chair The fast growing demand of wireless communications for voice and data has driven recent efforts to dramatically increase the levels of integration in RF transceivers. One approach to this challenge is to implement all the RF functions in the low-cost CMOS technology, so that RF and baseband sections can be combined in a single chip. This in turn dictates an integrated CMOS implementation of the local oscillators with the same or even better phase noise performance than its discrete counterpart, generally a difficult task using conventional approaches with the available low-Q integrated inductors. -

Superheterodyne Receiver

Superheterodyne Receiver The received RF-signals must transformed in a videosignal to get the wanted informations from the echoes. This transformation is made by a super heterodyne receiver. The main components of the typical superheterodyne receiver are shown on the following picture: Figure 1: Block diagram of a Superheterodyne The superheterodyne receiver changes the rf frequency into an easier to process lower IF- frequency. This IF- frequency will be amplified and demodulated to get a videosignal. The Figure shows a block diagram of a typical superheterodyne receiver. The RF-carrier comes in from the antenna and is applied to a filter. The output of the filter are only the frequencies of the desired frequency-band. These frequencies are applied to the mixer stage. The mixer also receives an input from the local oscillator. These two signals are beat together to obtain the IF through the process of heterodyning. There is a fixed difference in frequency between the local oscillator and the rf-signal at all times by tuning the local oscillator. This difference in frequency is the IF. this fixed difference an ganged tuning ensures a constant IF over the frequency range of the receiver. The IF-carrier is applied to the IF-amplifier. The amplified IF is then sent to the detector. The output of the detector is the video component of the input signal. Image-frequency Filter A low-noise RF amplifier stage ahead of the converter stage provides enough selectivity to reduce the image-frequency response by rejecting these unwanted signals and adds to the sensitivity of the receiver. -

Lecture 15: Introduction to Mixers

EECS 142 Lecture 15: Introduction to Mixers Prof. Ali M. Niknejad University of California, Berkeley Copyright c 2005 by Ali M. Niknejad A. M. Niknejad University of California, Berkeley EECS 142 Lecture 15 p. 1/22 – p. 1/22 Mixers IF RF RF IF LO LO An ideal mixer is usually drawn with a multiplier symbol A real mixer cannot be driven by arbitrary inputs. Instead one port, the “LO” port, is driven by an local oscillator with a fixed amplitude sinusoid. In a down-conversion mixer, the other input port is driven by the “RF” signal, and the output is at a lower IF intermediate frequency In an up-coversion mixer, the other input is the IF signal and the output is the RF signal A. M. Niknejad University of California, Berkeley EECS 142 Lecture 15 p. 2/22 – p. 2/22 Frequency Translation down- conv ers ion IF IFRF LO As shown above, an ideal mixer translates the modulation around one carrier to another. In a receiver, this is usually from a higher RF frequency to a lower IF frequency. In a transmitter, it’s the inverse. We know that an LTI circuit cannot perform frequency translation. Mixers can be realized with either time-varying circuits or non-linear circuits A. M. Niknejad University of California, Berkeley EECS 142 Lecture 15 p. 3/22 – p. 3/22 Ideal Multiplier Suppose that the input of the mixer is the RF and LO signal vRF = A(t) cos (ω0t + φ(t)) vLO = ALO cos (ωL0t) Recall the trigonometric identity cos(A + B) = cos A cos B − sin A sin B Applying the identity, we have vout = vRF × vLO A(t)ALO = {cos φ (cos(ωLO + ω0)t + cos(ωLO − ω0)t) 2 − sin φ (sin(ωLO + ω0)t + sin(ωLO − ω0)t)} A. -

Phase-Locked Loop Based Oscillator Phase Noise Measurement Technique

University of Central Florida STARS Retrospective Theses and Dissertations 1986 Phase-Locked Loop Based Oscillator Phase Noise Measurement Technique Luis M. Jimenez University of Central Florida Part of the Engineering Commons Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact [email protected]. STARS Citation Jimenez, Luis M., "Phase-Locked Loop Based Oscillator Phase Noise Measurement Technique" (1986). Retrospective Theses and Dissertations. 4980. https://stars.library.ucf.edu/rtd/4980 PHASE-LOCKED LOOP BASED OSCILLATOR PHASE NOISE MEASUREMENT TECHNIQUE BY LUIS MIGUEL JIMENEZ B.S.E., University of Central Florida, 1984 THESIS Submitted in partial fulfillment of the requirements for the degree of Master of Science in the Graduate Studies Program of the College of Engineering University of Central Florida Orlando, Florida Summer Term 1986 ABSTRACT Oscillators play an important role in the performance of various radio frequency (RF) systems. The generation of stable carrier and clock frequencies is necessary at both the transmitter and receiver ends of a communication system. Phase noise is the parameter used to characterize an oscillator frequency stability. This thesis introduces a phase noise measurement technique using a phase-locked loop. A 100 MHz Colpitt's oscillator, for the phase noise source, was designed and built. The output of the oscillator was mixed down to 10 MHz, before a phase-locked loop extracted the phase noise information. -

Intermediate Frequency (IF) Sampling Receiver Concepts

ADC12DL040,ADC12DL065,ADC12DL080, ADC14L020,ADC14L040,CLC5903,LMH6550, LMH6551 Intermediate Frequency (IF) Sampling Receiver Concepts Literature Number: SNAA107 AnalogEdge_V4_Issue3 5/31/06 10:26 AM Page 1 ANALOG edge SM Expert tips, tricks, and techniques for analog designs Vol. IV, Issue 3 DESIGN idea Intermediate Frequency (IF) Sampling Receiver Concepts Mark Rives, Principal Applications Engineer his article will discuss Intermediate Frequency zone from 39 MHz to 78 MHz, it can still be recovered (IF) sampling concepts of sub-sampling (or but the absolute frequency information is lost. When the Tunder sampling), noise processing gain, and the input signal moves above Fs/2, it has been effects of interfering signals. Examples will be based on sub-sampled and ‘reflects’ or ‘folds’ at Fs/2 and moves the GSM/EDGE communications standard where the back toward 0 Hz at the ADC output. If Fs/2 = 39 MSPS, channel bandwidth is 200 kHz and the sample rate is an input signal at 40 MHz will fold back to 38 MHz. typically a multiple of 13 MHz. Folding will occur in each Nyquist zone. For example, a 244 MHz IF at 78 MSPS will result in a 10 MHz signal Sub-Sampling at the ADC output. The folded (or aliased) frequency is Nyquist’s sampling theorem states that if a signal is sampled calculated by finding the closest multiple of Fs to the at least twice as fast as the highest sampled frequency desired input frequency (FIN, 244 MHz), then subtracting component, no information will be lost when the signal is the two frequencies: reconstructed. -

AP-60-860A Agile Processor

AP-60-860A Agile Processor The AP-60-860A (Agile Digital/Analog Processor) operates in one of the three following modes: Mode 1: Analog Heterodyne Processor (Analog RF IN > Analog RF OUT) D Mode 2: Digital Heterodyne Processor (QAM IN > QAM OUT) I Mode 3: Digital-to-Analog Processor (8VSB or QAM IN > Analog RF OUT) G I Mode 1 Mode 2 Mode 3 T Analog RF QAM QAM/8VSB CATV Ch. T7-T13 A CATV Ch. 2-135 CATV Ch. 2-135 VHF Ch. 2-13 CATV Ch. T7-T13 VHF Ch. 2-13 L UHF Ch. 14-69 CATV Ch. 2-135 UHF Ch. 14-69 C O CATV Ch. 2-135 CATV Ch. 2-135 CATV Ch. 2-135 L L Analog RF QAM Analog RF E +60 dBmV +55 dBmV +60 dBmV C T Features I • As an agile analog heterodyne processor: accepts one Analog RF input (CATV sub-band channels T7-T13, CATV standard channels 2-135, VHF channels 2-13, and UHF channels 14-69) and delivers one Analog RF output (CATV standard channels 2-135) O • As an agile digital heterodyne processor: accepts one Digital Cable QAM input (CATV sub-band channels T7-T13, and CATV standard N channels 2-135) and delivers one Digital Cable QAM output (CATV standard channels 2-135) • As an agile digital-to-analog processor: accepts one Digital Off-air 8VSB or Digital Cable QAM input (CATV standard channels 2-135, VHF channels 2-13, and UHF channels 14-69) and delivers one Analog RF output (CATV standard channels 2-135) • Equipped with EAS interface which can also be used as an IF (Intermediate Frequency) input • Supports Closed Captioning (EIA-608) Ordering Information Model Stock # Description AP-60-860A 59819 Agile, Processor, +60 dBmV, 54-860 MHz output Related Products Model Description DAP Digital-to-Analog Processor; 1 RU AP Series Agile Heterodyne Processor; 1 RU Purchase from: www.multicominc.com 800-423-2594 407-331-7779 ® Rev.