802.15.4 Low Intermediate Frequency Radio Receiver

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

RANDOM VIBRATION—AN OVERVIEW by Barry Controls, Hopkinton, MA

RANDOM VIBRATION—AN OVERVIEW by Barry Controls, Hopkinton, MA ABSTRACT Random vibration is becoming increasingly recognized as the most realistic method of simulating the dynamic environment of military applications. Whereas the use of random vibration specifications was previously limited to particular missile applications, its use has been extended to areas in which sinusoidal vibration has historically predominated, including propeller driven aircraft and even moderate shipboard environments. These changes have evolved from the growing awareness that random motion is the rule, rather than the exception, and from advances in electronics which improve our ability to measure and duplicate complex dynamic environments. The purpose of this article is to present some fundamental concepts of random vibration which should be understood when designing a structure or an isolation system. INTRODUCTION Random vibration is somewhat of a misnomer. If the generally accepted meaning of the term "random" were applicable, it would not be possible to analyze a system subjected to "random" vibration. Furthermore, if this term were considered in the context of having no specific pattern (i.e., haphazard), it would not be possible to define a vibration environment, for the environment would vary in a totally unpredictable manner. Fortunately, this is not the case. The majority of random processes fall in a special category termed stationary. This means that the parameters by which random vibration is characterized do not change significantly when analyzed statistically over a given period of time - the RMS amplitude is constant with time. For instance, the vibration generated by a particular event, say, a missile launch, will be statistically similar whether the event is measured today or six months from today. -

AM Series AGILE MODULATOR

AM Series AGILE MODULATOR AM series is a family of frequency-agile analog audio/video modulators. AM-60-860, the flag-ship model, is available in NTSC C channels 2-135 (54-860 MHz), and the PAL B, G, and I channels in the same frequency range. A More economical models are available in NTSC for the frequency ranges 54-550 MHz, or 54-806 MHz. EAS (Emergency Alert System) is standard on all models. Stereo Audio, SAP (Secondary Audio Programming), and several other optional T features are also available. V Baseband Audio/Video P R O D U Modulated C Analog RF T S Ordering Information Model Stock # Description AM-60-860 59415A Frequency-agile Audio/Video Modulator, +60 dBmV, 54-860 MHz (NTSC) AM-60-806 59419 Frequency-agile Audio/Video Modulator, +60 dBmV, 54-806 MHz (NTSC) AM-60-550 59416 Frequency-agile Audio/Video Modulator, +60 dBmV, 54-550 MHz (NTSC) AM-45-550 59404 Frequency-agile Audio/Video Modulator, +45 dBmV, 54-550 MHz (NTSC) Options AM-OPT-02 BNC Video Input Connector AM-OPT-04 Sub-Band Output (Available with AM-60-550 only) AM-OPT-05 Integrated BTSC Stereo Audio AM-OPT-06 SAP Audio/ BTSC Stereo (Available with AM-60-860 only) products AM-OPT-07 Video AGC CATV AM-OPT-09 Balanced Audio Input, 600 Ohm (Standard on AM-60-860) Related Products Model Description AMCM Frequency-agile Audio/Video modulator, +45 dBmV, 54-860 MHz (NTSC & PAL), Twelve modulators in 2RU modulators freq. agile ACM Frequency-agile Audio/Video modulator, +45 dBmV, 54-806 MHz (NTSC only), Twelve modulators in 2RU MICM Fixed-channel Audio/Video modulator, +45 dBmV, 54-806 MHz (NTSC & PAL), Twelve modulators in 2RU www.blondertongue.com | 800-523-6049 76 Specifications Input Output Connector Connector: “F” Female Standard: “F” Female Impedance: 75 Ω Option 2: BNC Female Impedance: 75 Ω Return Loss: 12 dB Return Loss: 18 dB Frequency Range Video Input Level AM-60-860 Model: 54 to 860 MHz (NTSC CATV Ch. -

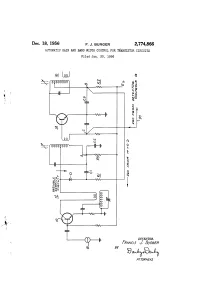

Dec. 18, 1956 . F. J. BURGER 2,774,866 Firancis. J. B/RGER

Dec. 18, 1956 . F. J. BURGER 2,774,866 AUTOMATIC GAIN AND BAND WIDTH CONTROL FORTRANSISTOR CIRCUITS Filed Jan. 30, 1956 s log 00 0 0-0 000 & S. l INVENTOR, firANCIS. J. B/RGER 9. BY alid. A77ORNEYs 2,774,866 United States Patent Office Patented Dec. 18, 1956 2 reduced gain conditions. In order to prevent such dis tortion some means is required to reduce the signal level 2,774,866 prior to its application to the first intermediate frequency stage. In addition to the distortion problem, as is known, AUTOMATIC GAN AND BAND WIDTH CONTROL 5 the band width of the intermediate frequency amplifier FORTRANSISTOR CIRCUITS varies as a function of the magnitude of the automatic Francis J. Burger, Leonia, N. J., assignior to Enuerson gain controi voltage. As the gain of the transistor is Radio & Phonograph Corporation, Jersey City, N. , reduced, the loading which it presents to the intermediate a corporation of New York frequency coils decreases, thus increasing the Q of the O circuit and narrowing the band width. There also results Application January 30, 1956, Serial No. 562,072 a change in reactive loading provided by the I. F. tran 6 Claims. (C. 250-20) sistor which causes the intermediate frequency coils to shift their frequency center to a higher value. The purpose of this invention is to provide a variable This invention relates to improvements in transistor damping system which will vary the primary damping circuits, particularly transistor radio receivers with re of the converter intermediate frequency coil as a func spect to means for providing automatic gain and band tion of the automatic gain control voltage. -

Amplifier Frequency Response

EE105 – Fall 2015 Microelectronic Devices and Circuits Prof. Ming C. Wu [email protected] 511 Sutardja Dai Hall (SDH) 2-1 Amplifier Gain vO Voltage Gain: Av = vI iO Current Gain: Ai = iI load power vOiO Power Gain: Ap = = input power vIiI Note: Ap = Av Ai Note: Av and Ai can be positive, negative, or even complex numbers. Nagative gain means the output is 180° out of phase with input. However, power gain should always be a positive number. Gain is usually expressed in Decibel (dB): 2 Av (dB) =10log Av = 20log Av 2 Ai (dB) =10log Ai = 20log Ai Ap (dB) =10log Ap 2-2 1 Amplifier Power Supply and Dissipation • Circuit needs dc power supplies (e.g., battery) to function. • Typical power supplies are designated VCC (more positive voltage supply) and -VEE (more negative supply). • Total dc power dissipation of the amplifier Pdc = VCC ICC +VEE IEE • Power balance equation Pdc + PI = PL + Pdissipated PI : power drawn from signal source PL : power delivered to the load (useful power) Pdissipated : power dissipated in the amplifier circuit (not counting load) P • Amplifier power efficiency η = L Pdc Power efficiency is important for "power amplifiers" such as output amplifiers for speakers or wireless transmitters. 2-3 Amplifier Saturation • Amplifier transfer characteristics is linear only over a limited range of input and output voltages • Beyond linear range, the output voltage (or current) waveforms saturates, resulting in distortions – Lose fidelity in stereo – Cause interference in wireless system 2-4 2 Symbol Convention iC (t) = IC +ic (t) iC (t) : total instantaneous current IC : dc current ic (t) : small signal current Usually ic (t) = Ic sinωt Please note case of the symbol: lowercase-uppercase: total current lowercase-lowercase: small signal ac component uppercase-uppercase: dc component uppercase-lowercase: amplitude of ac component Similarly for voltage expressions. -

En 300 720 V2.1.0 (2015-12)

Draft ETSI EN 300 720 V2.1.0 (2015-12) HARMONISED EUROPEAN STANDARD Ultra-High Frequency (UHF) on-board vessels communications systems and equipment; Harmonised Standard covering the essential requirements of article 3.2 of the Directive 2014/53/EU 2 Draft ETSI EN 300 720 V2.1.0 (2015-12) Reference REN/ERM-TG26-136 Keywords Harmonised Standard, maritime, radio, UHF ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at http://portal.etsi.org/tb/status/status.asp If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

Frequency Response and Bode Plots

1 Frequency Response and Bode Plots 1.1 Preliminaries The steady-state sinusoidal frequency-response of a circuit is described by the phasor transfer function Hj( ) . A Bode plot is a graph of the magnitude (in dB) or phase of the transfer function versus frequency. Of course we can easily program the transfer function into a computer to make such plots, and for very complicated transfer functions this may be our only recourse. But in many cases the key features of the plot can be quickly sketched by hand using some simple rules that identify the impact of the poles and zeroes in shaping the frequency response. The advantage of this approach is the insight it provides on how the circuit elements influence the frequency response. This is especially important in the design of frequency-selective circuits. We will first consider how to generate Bode plots for simple poles, and then discuss how to handle the general second-order response. Before doing this, however, it may be helpful to review some properties of transfer functions, the decibel scale, and properties of the log function. Poles, Zeroes, and Stability The s-domain transfer function is always a rational polynomial function of the form Ns() smm as12 a s m asa Hs() K K mm12 10 (1.1) nn12 n Ds() s bsnn12 b s bsb 10 As we have seen already, the polynomials in the numerator and denominator are factored to find the poles and zeroes; these are the values of s that make the numerator or denominator zero. If we write the zeroes as zz123,, zetc., and similarly write the poles as pp123,, p , then Hs( ) can be written in factored form as ()()()s zsz sz Hs() K 12 m (1.2) ()()()s psp12 sp n 1 © Bob York 2009 2 Frequency Response and Bode Plots The pole and zero locations can be real or complex. -

Evaluation of Audio Test Methods and Measurements for End-Of-Line Loudspeaker Quality Control

Evaluation of audio test methods and measurements for end-of-line loudspeaker quality control Steve Temme1 and Viktor Dobos2 (1. Listen, Inc., Boston, MA, 02118, USA. [email protected]; 2. Harman/Becker Automotive Systems Kft., H-8000 Székesfehérvár, Hungary) ABSTRACT In order to minimize costly warranty repairs, loudspeaker OEMS impose tight specifications and a “total quality” requirement on their part suppliers. At the same time, they also require low prices. This makes it important for driver manufacturers and contract manufacturers to work with their OEM customers to define reasonable specifications and tolerances. They must understand both how the loudspeaker OEMS are testing as part of their incoming QC and also how to implement their own end-of-line measurements to ensure correlation between the two. Specifying and testing loudspeakers can be tricky since loudspeakers are inherently nonlinear, time-variant and effected by their working conditions & environment. This paper examines the loudspeaker characteristics that can be measured, and discusses common pitfalls and how to avoid them on a loudspeaker production line. Several different audio test methods and measurements for end-of- the-line speaker quality control are evaluated, and the most relevant ones identified. Speed, statistics, and full traceability are also discussed. Keywords: end of line loudspeaker testing, frequency response, distortion, Rub & Buzz, limits INTRODUCTION In order to guarantee quality while keeping testing fast and accurate, it is important for audio manufacturers to perform only those tests which will easily identify out-of-specification products, and omit those which do not provide additional information that directly pertains to the quality of the product or its likelihood of failure. -

Calibration of Radio Receivers to Measure Broadband Interference

NBSIR 73-335 CALIBRATION OF RADIO RECEIVERS TO MEASORE BROADBAND INTERFERENCE Ezra B. Larsen Electromagnetics Division Institute for Basic Standards National Bureau of Standards Boulder, Colorado 80302 September 1973 Final Report, Phase I Prepared for Calibration Coordination Group Army /Navy /Air Force NBSIR 73-335 CALIBRATION OF RADIO RECEIVERS TO MEASORE BROADBAND INTERFERENCE Ezra B. Larsen Electromagnetics Division Institute for Basic Standards National Bureau of Standards Boulder, Colorado 80302 September 1973 Final Report, Phase I Prepared for Calibration Coordination Group Army/Navy /Air Force u s. DEPARTMENT OF COMMERCE, Frederick B. Dent. Secretary NATIONAL BUREAU OF STANDARDS. Richard W Roberts Director V CONTENTS Page 1. BACKGROUND 2 2. INTRODUCTION 3 3. DEFINITIONS OF RECEIVER BANDWIDTH AND IMPULSE STRENGTH (Or Spectral Intensity) 5 3.1 Random noise bandwidth 5 3.2 Impulse bandwidth in terms of receiver response transient 7 3.3 Voltage-response bandwidth of receiver 8 3.4 Receiver bandwidths related to voltage- response bandwidth 9 3.5 Impulse strength in terms of random-noise bandwidth 10 3.6 Sum-and-dif ference correlation radiometer technique 10 3.7 Impulse strength in terms of Fourier trans- forms 11 3.8 Impulse strength in terms of rectangular DC pulses 12 3.9 Impulse strength and impulse bandwidth in terms of RF pulses 13 4. EXPERIMENTAL PROCEDURE AND DATA 16 4.1 Measurement of receiver input impedance and phase linearity 16 4.2 Calibration of receiver as a tuned RF volt- meter 20 4.3 Stepped- frequency measurements of receiver bandwidth 23 4.4 Calibration of receiver impulse bandwidth with a baseband pulse generator 37 iii CONTENTS [Continued) Page 4.5 Calibration o£ receiver impulse bandwidth with a pulsed-RF source 38 5. -

Superheterodyne Receiver

Superheterodyne Receiver The received RF-signals must transformed in a videosignal to get the wanted informations from the echoes. This transformation is made by a super heterodyne receiver. The main components of the typical superheterodyne receiver are shown on the following picture: Figure 1: Block diagram of a Superheterodyne The superheterodyne receiver changes the rf frequency into an easier to process lower IF- frequency. This IF- frequency will be amplified and demodulated to get a videosignal. The Figure shows a block diagram of a typical superheterodyne receiver. The RF-carrier comes in from the antenna and is applied to a filter. The output of the filter are only the frequencies of the desired frequency-band. These frequencies are applied to the mixer stage. The mixer also receives an input from the local oscillator. These two signals are beat together to obtain the IF through the process of heterodyning. There is a fixed difference in frequency between the local oscillator and the rf-signal at all times by tuning the local oscillator. This difference in frequency is the IF. this fixed difference an ganged tuning ensures a constant IF over the frequency range of the receiver. The IF-carrier is applied to the IF-amplifier. The amplified IF is then sent to the detector. The output of the detector is the video component of the input signal. Image-frequency Filter A low-noise RF amplifier stage ahead of the converter stage provides enough selectivity to reduce the image-frequency response by rejecting these unwanted signals and adds to the sensitivity of the receiver. -

Lecture 15: Introduction to Mixers

EECS 142 Lecture 15: Introduction to Mixers Prof. Ali M. Niknejad University of California, Berkeley Copyright c 2005 by Ali M. Niknejad A. M. Niknejad University of California, Berkeley EECS 142 Lecture 15 p. 1/22 – p. 1/22 Mixers IF RF RF IF LO LO An ideal mixer is usually drawn with a multiplier symbol A real mixer cannot be driven by arbitrary inputs. Instead one port, the “LO” port, is driven by an local oscillator with a fixed amplitude sinusoid. In a down-conversion mixer, the other input port is driven by the “RF” signal, and the output is at a lower IF intermediate frequency In an up-coversion mixer, the other input is the IF signal and the output is the RF signal A. M. Niknejad University of California, Berkeley EECS 142 Lecture 15 p. 2/22 – p. 2/22 Frequency Translation down- conv ers ion IF IFRF LO As shown above, an ideal mixer translates the modulation around one carrier to another. In a receiver, this is usually from a higher RF frequency to a lower IF frequency. In a transmitter, it’s the inverse. We know that an LTI circuit cannot perform frequency translation. Mixers can be realized with either time-varying circuits or non-linear circuits A. M. Niknejad University of California, Berkeley EECS 142 Lecture 15 p. 3/22 – p. 3/22 Ideal Multiplier Suppose that the input of the mixer is the RF and LO signal vRF = A(t) cos (ω0t + φ(t)) vLO = ALO cos (ωL0t) Recall the trigonometric identity cos(A + B) = cos A cos B − sin A sin B Applying the identity, we have vout = vRF × vLO A(t)ALO = {cos φ (cos(ωLO + ω0)t + cos(ωLO − ω0)t) 2 − sin φ (sin(ωLO + ω0)t + sin(ωLO − ω0)t)} A. -

Frequency Response Analysis

Frequency Response Analysis Technical Report 10 tech10.pub 26 May 1999 22:05 page 1 Frequency Response Analysis Technical Report 10 N.D. Cogger BSc, PhD, MIOA R.V.Webb BTech, PhD, CEng, MIEE Solartron Instruments Solartron Instruments a division of Solartron Group Ltd Victoria Road, Farnborough Hampshire, GU14 7PW 1997 tech10.pub 26 May 1999 22:05 page 2 Solartron Solartron Overseas Sales Ltd Victoria Road, Farnborough Instruments Division Hampshire GU14 7PW England Block 5012 TECHplace II Tel: +44 (0)1252 376666 Ang Mo Kio Ave. 5, #04-11 Fax: +44 (0)1252 544981 Ang Mo Kio Industrial Park Fax: +44 (0)1252 547384 (Transducers) Singapore 2056 Republic of Singapore Solartron Transducers Tel: +65 482 3500 19408 Park Row, Suite 320 Fax: +65 482 4645 Houston, Texas, 77084 USA Tel: +1 281 398 7890 Solartron Fax: +1 281 398 7891 Beijing Liaison Office Room 327. Ya Mao Building Solartron No. 16 Bei Tu Chen Xi Road 964 Marcon Blvd, Suite 200 Beijing 100101, PR China 91882 MASSY, Cedex Tel: +86 10 2381199 ext 2327 France Fax: +86 10 2028617 Tel: +33 (0)1 69 53 63 53 Fax: +33 (0)1 60 13 37 06 Email: [email protected] Web: http://www.solartron.com For details of our agents in other countries, please contact our Farnborough, UK office. Solartron Instruments pursue a policy of continuous development and product improvement. The specification in this document may therefore be changed without notice. tech10.pub 26 May 1999 22:05 page 3 Frequency Response Analysis P E Wellstead B.Sc. M.Sc. -

Nyquist Stability Criteria

NPTEL >> Mechanical Engineering >> Modeling and Control of Dynamic electro-Mechanical System Module 2- Lecture 14 Nyquist Stability Criteria Dr. Bis ha kh Bhatt ac harya Professor, Department of Mechanical Engineering IIT Kanpur Joint Initiative of IITs and IISc - Funded by MHRD NPTEL >> Mechanical Engineering >> Modeling and Control of Dynamic electro-Mechanical System Module 2- Lecture 14 This Lecture Contains Introduction to Geometric Technique for Stability Analysis Frequency response of two second order systems Nyquist Criteria Gain and Phase Margin of a system Joint Initiative of IITs and IISc - Funded by MHRD NPTEL >> Mechanical Engineering >> Modeling and Control of Dynamic electro-Mechanical System Module 2- Lecture 14 Introduction In the last two lectures we have considered the evaluation of stability by mathema tica l eval uati on of th e ch aract eri sti c equati on. Rth’Routh’s tttest an d Kharitonov’s polynomials are used for this purpose. There are several geometric procedures to find out the stability of a system. These are based on: Nyquist Plot Root Locus Plot and Bode plot The advantage of these geometric techniques is that they not only help in checking the stability of a system, they also help in designing controller for the systems. Joint Initiative of IITs and IISc ‐ Funded by 3 MHRD NPTEL >> Mechanical Engineering >> Modeling and Control of Dynamic electro-Mechanical System Module 2- Lecture 14 NitNyquist Plo t is bdbased on Frequency Response of a TfTransfer FtiFunction. CidConsider two transfer functions as follows: s 5 s 5 T (s) ; T (s) 1 s2 3s 2 2 s2 s 2 The two functions have identical zero.