Testing of an Optimised Data Bus for Pico- and Nanosatellites Making Cubesats Future-Proof

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

List of Known Issues for Winidea 9.21.6.0.117591

List of known issues for winIDEA 9.21.6.0.117591 Issue ID Severity Description General S001177 Medium winIDEA connection stops working after several hours of active debug session. S003966 Low Callstack is not displayed correctly if ARM Cortex application is compiled with DiabData compiler. S003658 Medium Go to... after download operation is not supported for secondary cores. S002844 Low winIDEA becomes unresponsive if CPU Options are changed when winIDEA terminal is connected to SoC and SoC is running. Infineon S003288 Medium winIDEA trace unreliable if interrupt hits on traced function exit (Infineon TC3xx). S003351 Medium Trace synchronization time error between CAN and AGBT trace gradually increases with recording length, (Infineon TC399XE). S003996 Medium Reset is not stable (Infineon TLE9844). S003803 Medium Flash Blank Check after Mass Erase does not work if secondary cores are running (Infineon TC298TP). S003792 Medium winIDEA cannot stop CPU core after external reset is triggered to SoC (Infineon TC298TF). S003330 Medium Start of trace session over AGBT trace protocol fails with faulty error message (Infineon TC277TE). iSYSTEM FBridge debug sync doesn't work when Infineon TC3xx is configured as a master workspace and used in conjunction with S003225 Medium Infineon AGBT Aurora Active Probe (Infineon TC3xx). Swapping tracing data from multiple cores, then in the next trace session from single core and in the next trace session again from S003174 Medium multiple cores, data are not traced from all configured cores (Infineon TC399XE). Correlation between AOM CAN trace and SoC data trace yields incorrect timeline ordering of the events (Infineon TriCore TC2xx and S000221 Low TC3xx). -

SPECIAL ISSUE Internet-Of-Things

boards & solutions + Combined Print Magazine for the European Embedded Market June 03/15 SPECIAL ISSUE Internet-of-Things Wearable Devices.indd 2 24/04/15 12:18 VIEWPOINT Dear Readers, ere is now doubt - a new emerg- ing Megatrend called the Internet of ings (IoT) is going propel- ling the entire electronics indus- try. According to the de nition of Wikipedia “ e Internet of ings is the network of physical objects or things embedded with electron- ics, so ware, sensors and connec- tivity to enable it to achieve greater value and service by exchanging data with the manufacturer, opera- tor and/or other connected devices. Each thing is uniquely identi able through its embedded computing system but is able to interoperate within the existing Internet infra- structure.” e Internet of ings is by another de nition “a group of physical objects with embedded sensor technology that communi- cates an internal state or external environments to a network”. According to Gartner, there will be nearly 26 billion devices on the Inter- net of ings by 2020. ABI Research estimates that more than 30 billion devices will be wirelessly connected to the Internet of ings (Internet of Everything) by 2020. As per a recent survey and study done by Pew Research Internet Project, a large majority of the technology experts and engaged Internet users who responded agreed with the notion that the Internet/Cloud of ings, embedded and wearable computing will have widespread and bene cial e ects by 2025. It is, as such clear that the IoT will consist of a very large number of devices being connected to the Internet. -

Embedded Systems Design with the Texas Instruments MSP432 32-Bit Processor

Embedded Systems Design with the Texas Instruments MSP432 32-bit Processor Synthesis Lectures on Digital Circuits and Systems Editor Mitchell A. ornton, Southern Methodist University e Synthesis Lectures on Digital Circuits and Systems series is comprised of 50- to 100-page books targeted for audience members with a wide-ranging background. e Lectures include topics that are of interest to students, professionals, and researchers in the area of design and analysis of digital circuits and systems. Each Lecture is self-contained and focuses on the background information required to understand the subject matter and practical case studies that illustrate applications. e format of a Lecture is structured such that each will be devoted to a specific topic in digital circuits and systems rather than a larger overview of several topics such as that found in a comprehensive handbook. e Lectures cover both well-established areas as well as newly developed or emerging material in digital circuits and systems design and analysis. Embedded Systems Design with the Texas Instruments MSP432 32-bit Processor Dung Dang, Daniel J. Pack, and Steven F. Barrett 2017 Fundamentals of Electronics: Book 4 Oscillators and Advanced Electronics Topics omas F. Schubert, Jr., and Ernest M. Kim 2016 Fundamentals of Electronics: Book 3 Active Filters and Amplifier Frequency Response omas F. Schubert, Jr., and Ernest M. Kim 2016 Bad to the Bone: Crafting Electronic Systems with BeagleBone Black, Second Edition Steven Barrett and Jason Kridner 2016 Fundamentals of Electronics: Book 2 omas F. Schubert, Jr., and Ernest M. Kim 2015 Fundamentals of Electronics: Book 1 Electronic Devices and Circuit Applications omas F. -

2019 Embedded Markets Study Integrating Iot and Advanced Technology Designs, Application Development & Processing Environments March 2019

2019 Embedded Markets Study Integrating IoT and Advanced Technology Designs, Application Development & Processing Environments March 2019 Presented By: © 2019 AspenCore All Rights Reserved 2 Preliminary Comments • Results: Data from this study is highly projectable at 95% confidence with +/-3.15% confidence interval. Other consistencies with data from previous versions of this study also support a high level of confidence that the data reflects accurately the EETimes and Embedded.com audience’s usage of advance technologies, software and hardware development tools, chips, operating systems, FPGA vendors, and the entire ecosystem of their embedded development work environment and projects with which they are engaged. • Historical: The EETimes/Embedded.com Embedded Markets Study was last conducted in 2017. This report often compares results for 2019 to 2017 and in some cases to 2015 and earlier. This study was first fielded over 20 years ago and has seen vast changes in technology evolution over that period of time. • Consistently High Confidence: Remarkable consistency over the years has monitored both fast and slow moving market changes. A few surprises are shown this year as well, but overall trends are largely confirmed. • New Technologies and IoT: Emerging markets and technologies are also tracked in this study. New data regarding IoT and advanced technologies (IIoT, embedded vision, embedded speech, VR, AR, machine learning, AI and other cognitive capabilities) are all included. 3 Purpose and Methodology • Purpose: To profile the findings of the 2019 Embedded Markets Study comprehensive survey of the embedded systems markets worldwide. Findings include technology used, all aspects of the embedded development process, IoT, emerging technologies, tools used, work environment, applications developed for, methods/ processes, operating systems used, reasons for using chips and technology, and brands and specific chips being considered by embedded developers. -

Openocd 0.11.0 Released!

OpenOCD 0.11.0 released! https://www.mikrozone.sk/news.php?item.1531 Tak sme sa dočkali! Zhruba po 4 rokoch bola uvoľnená nová verzia. Sťahujte odiaľto: sourceforge.net Skompilované binárky budú (dúfam, že o chvíľu) tu. Kompletnú históriu zmien nájdete tu. Najdôležitejšie zmeny sú tieto: JTAG Layer: - add debug level 4 for verbose I/O debug - bitbang, add read buffer to improve performance - Cadence SystemVerilog Direct Programming Interface (DPI) adapter driver - CMSIS-DAP v2 (USB bulk based) adapter driver - Cypress KitProg adapter driver - FTDI FT232R sync bitbang adapter driver - Linux GPIOD bitbang adapter driver through libgpiod - Mellanox rshim USB or PCIe adapter driver - Nuvoton Nu-Link and Nu-Link2 adapter drivers - NXP IMX GPIO mmap based adapter driver - ST-Link consolidate all versions in single config - ST-Link read properly old USB serial numbers 07.03.2021 1 / 8 OpenOCD 0.11.0 released! https://www.mikrozone.sk/news.php?item.1531 - STLink/V3 support (for ST devices only !) - STM8 SWIM transport - TI XDS110 adapter driver - Xilinx XVC/PCIe adapter driver Target Layer: - 64 bit address support - ARCv2 target support - ARM Cortex-A hypervisor mode support - ARM Cortex-M fast PC sampling support for profiling - ARM generic CTI support - ARM generic mem-ap target support - ARMv7-A MMU tools - ARMv7m traces add TCP stream server - ARMv8 AARCH64 target support and semihosting support - ARMv8 AARCH64 disassembler support through capstone library - ARMv8-M target support - EnSilica eSi-RISC target support, including instruction -

Known Issues Winidea

List of known issues for winIDEA 9.21.9.0.118566 Issue ID Severity Description General Certain function(s) can be missing in the Callstack view when stepping in the body part of the function (MPC5777M application compiled S004073 Medium with GHS). S001177 Medium winIDEA connection stops working after several hours of active debug session. S004061 Medium Call Stack doesn't work (ARM Cortex-M application compiled with GHS compiler). S004058 Medium Cannot view float type variables in Locals view (ARM Cortex-M code compiled with GHS compiler). S003658 Medium Go to... after download operation is not supported for secondary cores. S002844 Low winIDEA becomes unresponsive if CPU Options are changed when winIDEA terminal is connected to SoC and SoC is running. Infineon S003288 Medium winIDEA trace unreliable if interrupt hits on traced function exit (Infineon TC3xx). S004163 Medium winIDEA hangs after writing to Flash memory via memory window (Infineon TC298TP). S004136 Medium Download does not program application correctly to PFlash if PFlash Program Empty Cells option is deselected (Infineon TC3xx). S003996 Medium Reset is not stable (Infineon TLE9844). S003803 Medium Flash Blank Check after Mass Erase does not work if secondary cores are running (Infineon TC298TP). S003792 Medium BlueBox loses control over the CPU when an external target reset is applied (Infineon TC298TF). S003330 Medium Start of trace session over AGBT trace protocol fails with faulty error message (Infineon TC277TE). iSYSTEM FBridge debug sync doesn't work when Infineon TC3xx is configured as a master workspace and used in conjunction with S003225 Medium Infineon AGBT Aurora Active Probe (Infineon TC3xx). -

Evolution of the Communications Processor Board for the Istnanosat

Evolution of the Communications Processor Board for the ISTnanosat Joao˜ Carlos Fonseca Pinto Thesis to obtain the Master of Science Degree in Electronics Engineering Supervisors: Prof. Rui Manuel Rodrigues Rocha Prof. Moises´ Simoes˜ Piedade Examination Committee Chairperson: Prof. Pedro Miguel Pinto Ramos Supervisor: Prof. Rui Manuel Rodrigues Rocha Member of the Committee: Prof. Antonio´ Joaquim dos Santos Romao˜ Serralheiro November 2019 Declarac¸ao˜ Declaro que o presente documento e´ um trabalho original da minha autoria e que cumpre todos os requisitos do Codigo´ de Conduta e Boas Praticas´ da Universidade de Lisboa. Declaration I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa. Agradecimentos Em primeiro lugar, uma palavra de agradecimento aos meus orientadores, professor Rui Rocha e professor Moises´ Piedade, por todo o suporte, dedicac¸ao,˜ ensinamentos e conhecimentos transmitidos, bem como pelas cr´ıticas e revisoes˜ necessarias´ ao trabalho realizado nesta dissertac¸ao˜ de mestrado. A` equipa ISTnanosat, um obrigado pelos conselhos, apoio e companheirismo durante esta etapa, cuja progressao˜ se deve muito a voces.ˆ Aos meus pais, Manuela e Fernando Pinto, e aos meus irmaos,˜ Pedro e Antonio´ Pinto, por me ajudarem a crescer cientificamente e suportarem a minha vida, bem como pela motivac¸ao˜ e sacrif´ıcio dedicados a mim. Sem vocesˆ nada disto seria poss´ıvel. Ao Leite, Tomazio,´ Tiago, Lu´ıs, Antonio´ e Guilherme, pelo apoio e camaradagem durante todo o meu percurso universitario.´ Convosco tudo ficou bem mais facil.´ A` minha namorada, Joana Chumbo, pela pacienciaˆ e compaixao˜ que dedicaste a mim durante o nosso tempo. -

Winidea Build 9.17.0 Test Report Executed Tests

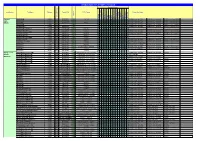

winIDEA build 9.17.0 Test Report Executed tests Architecture Test Name Platform Target CPU POD / Target Debug Tool Setup Passed fitIDEA Test Stand Emulation Type Debug Trigger Trace Coverage Profiler iTest DAQ Flash Port Trace User SoftwareTrace Hot Attach Renesas RX63 Jlink OCD RX63NB OK ZTE0262 ● ● Renesas V850 / RH850 V850Fx3 iCARD OCD 70F3373 OK ITV850FX2 ,rv:A1 ,sn:39604 ● ● ● IC30007 ,rv:G1 ,sn:100002 IC30126 ,rv:A3 ,sn:37390 V850Fx3 iC5000 OCD 70F3380 OK ITV850FX2 ,rv:A1 ,sn:39604 ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 V850Fx3 iC5500 OCD 70F3380 OK ITV850FX2 ,rv:A1 ,sn:39604 ● ● ● ● iC55000, rv:B, SN80714 iC60020, rv:C, sn:77313 V850Fx3 iC5700 OCD 70F3380 OK ITV850FX2 ,rv:A1 ,sn:39604 ● ● ● ● V850Fx4 iC5000 OCD 70F4010 ES2.1 OK V850E2K/Fx4 ● ● ● ● iC5000-1, rv:F1, sn66983 IC50020, rv:F2, sn:66935 V850Fx4 iC5500 OCD 70F4010 ES2.1 OK V850E2K/Fx4 ● ● ● ● iC55000, rv:B, SN80714 iC60020, rv:C, sn:77313 V850Fx4 iC5700 OCD 70F4010 ES2.1 OK V850E2K/Fx4 ● ● ● ● V850Fx4L iC5000 OCD 70F3580 ES2.0 OK V850E2K/Fx4-L ● ● ● ● iC5000-1, rv:G1, sn64718 IC50020, rv:F2, sn:64775 V850Fx4L iC5000 OCD 70F3585 OK Emulation adapter ZTE9001 ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 V850Fx4L iC5000 OCD 70F3572 ES1.0 OK ZTE0173 ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 RH850/E1M iC5000 OCD R7F701Z12 OK ZTE1159 ● ● ● iC50000 ,rv:E4 ,sn:71209 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, sn:69830 RH850/F1K iC5000 OCD R7F7015874 OK ● ● ● ● ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, -

Texas Instruments MSP432: Cortex-M4 Training Using the MSP432 Launchpad ARM Keil MDK 5 Toolkit Spring 2015 V 1.0 [email protected]

Texas Instruments MSP432: Cortex-M4 Training Using the MSP432 LaunchPad ARM Keil MDK 5 Toolkit Spring 2015 V 1.0 [email protected] Introduction: The latest version of this document is here: www.keil.com/appnotes/docs/apnt_276.asp ® ® The purpose of this lab is to introduce you to the TI MSP432 processor using the ARM Keil MDK toolkit featuring the IDE μVision®. At the end of this tutorial, you will be able to confidently work with this processor and Keil MDK. We recommend you obtain the new Getting Started MDK 5: manual from here: www.keil.com/mdk5/. Keil MDK supports TI Cortex-M processors. Check the Keil Device Database® on www.keil.com/dd2 for the complete list. Software Packs for MSP432, LM3S, LM4F and Tiva C are available on www.keil.com/dd2/pack/. See www.keil.com/ti for more details. Keil also has TI 8051 support. Cortex-A: Cortex-A processors are supported by ARM DS-5™. DS-5 is Linux and Android aware. www.arm.com/ds5. Keil MDK-Lite™ is a free evaluation version that limits code size to 32 Kbytes. Nearly all Keil examples will compile within this 32K limit. The addition of a valid license number will turn it into a specific commercial version. RTX RTOS: All variants of MDK contain the full version of RTX with Source Code. See www.keil.com/rl-arm/kernel.asp. Why Use Keil MDK ? MDK provides these features particularly suited for TI Cortex-M users: 1. µVision IDE with Integrated Debugger, Flash programmer and the ARM® Compiler/assembler/linker toolchain. -

TI MSP432: Cortex™-M4 Tutorial with ETM Using the MSP-EXP432E401Y

™ TI MSP432: Cortex -M4 Tutorial with ETM Using the MSP-EXP432E401Y LaunchPad Board and Winter 2017 V 0.8 [email protected] ARM Keil MDK 5 Toolkit The latest version of this document is here: www.keil.com/appnotes/docs/apnt_309.asp Introduction: The MSP432P401 lab is here: www.keil.com/appnotes/docs/apnt_276.asp The purpose of this lab is to introduce you to the TI MSP432 processor using the ARM® Keil® MDK toolkit featuring the IDE μVision®. This tutorial features ETM Instruction trace with Keil ULINKpro and power monitoring with the Keil ULINKplus. At the end of this tutorial, you will be able to confidently work with this processor and Keil MDK. Keil MDK supports TI Cortex-M processors. Check the Keil Device Database® on www.keil.com/dd2 for the complete list. Software Packs for MSP432, LM3S, LM4F and Tiva C are available here: www.keil.com/dd2/pack/. See www.keil.com/TI for more details. Keil also has TI 8051 support. DS-5™ supports TI Cortex-A. www.arm.com/ds5. Keil MDK-Lite™ is a free evaluation version that limits code size to 32 Kbytes. Nearly all Keil examples will compile within this 32K limit. The addition of a valid license number will turn MDK into a specific commercial version. Why Use Keil MDK ? MDK provides these features particularly suited for TI Cortex-M users: 1. µVision IDE with Integrated Debugger, Flash programmer and the ARM Compiler/assembler/linker toolchain. MDK is a complete turn-key "out-of-the-box" tool solution. 2. -

Wearables for Therapy Adherence

european www.electronics-eetimes.com April 2015 business press Wearables for therapy adherence Special focus: Optoelectronics Iconic Insights: Jaguar Land Rover’s Wolfgang Ziebart 150107_FRSH_EET_EU_Snipe.indd 1 12/30/14 3:29 PM 150401_COVB_EET_EU.indd 1 3/30/15 11:34 AM APRIL 2015 opinion DESIGN & PRODUCTS 4 Big data sets drones to fly SPECIAL FOCUSES: 50 Power grids - How many EVs can be charged - OPTOELECTRONICS simultaneoulsy? 22 Headlight control through eye-tracking Controlling your headlamp with a move of your eyes: neWS & TECHNOLOGY What sounds like Sci-Fi can soon be reality. Carmaker Opel is developing a technology 6 Sensor data predict failure of large machines that controls direction and bright- ness of the vehicle’s headlights 6 Printed NFC for context-aware by tracking the driver’s eyes. gameplay 22 Nanolaser enables on-chip photonics 7 Philips offloads LED lighting components unit for USD2.8bn 23 Tandem photovoltaics for record efficiencies? Researchers from Massachusetts 7 Cadence and ARM strategic partners on IP Institute of Technology (MIT) and Stanford University are exploring 8 3D Qualcomm SoCs by 2016 ways to create solar cells using The future of three-dimensional (3D) low-cost manufacturing methods. very large scale integration (VLSI) for system-on-chips (SoCs) will not stack 24 A new candidate for ultra-thin optoelectronics: die connected by through-silicon-vias DNA-peptide (TSVs), but will build them on a single layered die. 24 Ag nanodiscs to boost MoS2’s LED performance 10 Iconic Insights: The car’s the star… - WEARABLE & IMPLANTABLE ELECTRONICS Group Engineering Director at Jaguar Land Rover, Wolfgang Ziebart 28 Electronic patch increases therapy adherence discusses the impact of the fast- This poor adherence to medication moving world of electronics on the was reported by WHO back in 2003 more sedate environment of to result in increased morbidity and automotive manufacture. -

Winidea Build 9.17.39.78401 Test Report

winIDEA build 9.17.39.78401 Test Report Executed tests Architecture Test Name Platform Target CPU POD / Target Debug Tool Setup Passed Emulation TypeEmulation Debug TraceTrigger Coverage Profiler iTest DAQ Flash UserTrace Port SoftwareTrace Module I/O CAN2/LIN2 ADIO HotAttach Licensing Renesas RH850/E1M iC5000 OCD R7F701Z12 OK ZTE1159 ● ● ● ● ● iC50000 ,rv:E4 ,sn:71209 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, sn:69830 V850 RH850/F1K iC5000 OCD R7F7015874 OK ● ● ● ● ● ● ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, sn:69830 RH850 RH850/P1x iC5000 OCD R7F701310 OK ZTE0365 ● ● ● ● ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, sn:69830 RH850/D1M iC5000 OCD OK ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, sn:69830 RH850/P1H-C iC5000 OCD R7F701372 OK ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:A2, sn:69830 RH850/P1H-C (Aurora) iC6000 OCD R7F701370A OK ZTE1195 ● ● ● ● ● RH850/F1H Nexus iC5000 OCD R7F7015152 OK ZTE0434 ● ● ● ● ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:B1, sn:75693 RH850/F1H Nexus DDR iC5000 OCD R7F7015152 OK ZTE0434 ● ● ● ● ● ● ● ● ● iC50000 ,rv:E4 ,sn:64442 iC50020 ,rv:F1 ,sn:65680 IC50171, rv.:B1, sn:75693 RH850/F1H Nexus iC5500 OCD R7F7015152 OK ZTE0434 ● ● ● ● ● ● ● ● ● iC55000, rv:B, SN80714 iC60020, rv:C, sn:77313 IC50171, rv.:B1, sn:75693 RH850/F1H Nexus iC5700 OCD R7F7015152 OK ZTE0434 ● ● ● ● ● ● ● ● ● RH850/F1H Nexus DDR iC5700 OCD R7F7015152 OK ZTE0434 ● ● ● ● ● ● ●