Ipr2015-01021

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memory Expert Knowledge

Memory Expert Knowledge As the density increased throughout the 1970’s and in the Memory Experts 1980’s, Japanese DRAM manufacturers, who could sell The friendly team of Memory Experts at Mr Memory higher quality modules at lower prices, overtook IBM. 9 y have on average ears experience. They are fully Traditionally DRAM modules have an asynchronous knowledgeable on all things memory. interface, which means that they respond as quickly as Have a read through just some of that knowledge... possible to changes In control inputs. What is DRAM? SDRAM History DRAM stands for Dynamic Random Access Memory. This is the memory that you use in Desktops, Laptops, Synchronous Dynamic Random Access Memory Servers and other devices. A computer stores quickly (SDRAM) is memory that is synchronised with the System accessible data in the form of 0’s and 1’s. It is dynamic Bus (which connects all the major components of a because it refreshes its capacitor charge periodically computer system). Unlike DRAM, SDRAM waits for a with new electricity, compared to the older SRAM (Static clock signal before responding to control inputs. Random Access Memory). Data is stored in the SDRAM is organised into a grid structure (Banks) with capacitors within an integrated circuit (also known as a rows (Word lines) and columns (Bit lines). Data stored is Chip). in blocks and are defined by the coordinates of the row DRAM memory is a volatile memory – which means it and column of the specific information. loses its data very quickly once the power is removed. SDRAM was universally accepted in 1993, with the This is different from NAND Flash Memory used in invention of the Samsung KM48SL2000. -

Dynamic Rams from Asynchrounos to DDR4

Dynamic RAMs From Asynchrounos to DDR4 PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sun, 10 Feb 2013 17:59:42 UTC Contents Articles Dynamic random-access memory 1 Synchronous dynamic random-access memory 14 DDR SDRAM 27 DDR2 SDRAM 33 DDR3 SDRAM 37 DDR4 SDRAM 43 References Article Sources and Contributors 48 Image Sources, Licenses and Contributors 49 Article Licenses License 50 Dynamic random-access memory 1 Dynamic random-access memory Dynamic random-access memory (DRAM) is a type of random-access memory that stores each bit of data in a separate capacitor within an integrated circuit. The capacitor can be either charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. Since capacitors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically. Because of this refresh requirement, it is a dynamic memory as opposed to SRAM and other static memory. The main memory (the "RAM") in personal computers is dynamic RAM (DRAM). It is the RAM in laptop and workstation computers as well as some of the RAM of video game consoles. The advantage of DRAM is its structural simplicity: only one transistor and a capacitor are required per bit, compared to four or six transistors in SRAM. This allows DRAM to reach very high densities. Unlike flash memory, DRAM is volatile memory (cf. non-volatile memory), since it loses its data quickly when power is removed. The transistors and capacitors used are extremely small; billions can fit on a single memory chip. -

(12) United States Patent (10) Patent No.: US 8,782,350 B2 Lee Et Al

US008782350B2 (12) United States Patent (10) Patent No.: US 8,782,350 B2 Lee et al. (45) Date of Patent: Jul. 15, 2014 (54) CIRCUIT PROVIDING LOAD SOLATION (56) References Cited AND NOSE REDUCTION U.S. PATENT DOCUMENTS (75) Inventors: Hyun Lee, Ladera Ranch, CA (US); 3,660,675 A 5/1972 Andrews, Jr. Jayesh R. Bhakta, Cerritos, CA (US); 9, 1973 McCormicket al. Jeffrey C. Solomon, Irvine, CA (US); 3,757,235 A Mario Jesus Martinez, Laguna Niguel, (Continued) CA (US); Chi-She Chen, Walnut, CA (US) FOREIGN PATENT DOCUMENTS EP 1816 570 A2 8, 2007 (73) Assignee: Netlist, Inc., Irvine, CA (US) JP 09237492 9, 1997 (*) Notice: Subject to any disclaimer, the term of this (Continued) patent is extended or adjusted under 35 OTHER PUBLICATIONS U.S.C. 154(b) by 206 days. Der-Chang et al. “A parallel built-in self-diagnostic method for (21) Appl. No.: 13/412,243 embedded memoryarrays”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Apr. 2002, vol. 21, Issue (22) Filed: Mar. 5, 2012 4, pp. 449-465. (65) Prior Publication Data (Continued) US 2012/O250386 A1 Oct. 4, 2012 Primary Examiner — Gurte Bansal Related U.S. Application Data (74) Attorney, Agent, or Firm — Jamie J. Zheng, Esq. (63) Continuation of application No. 12/422,853, filed on (57) ABSTRACT Apr. 13, 2009, now Pat. No. 8,154,901. Certain embodiments described herein include a memory (60) Provisional application No. 61/044,839, filed on Apr. module having a printed circuit board including at least one 14, 2008, provisional application No. -

Understanding and Improving the Latency of DRAM-Based Memory Systems

Understanding and Improving the Latency of DRAM-Based Memory Systems Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Kevin K. Chang M.S., Electrical & Computer Engineering, Carnegie Mellon University B.S., Electrical & Computer Engineering, Carnegie Mellon University arXiv:1712.08304v1 [cs.AR] 22 Dec 2017 Carnegie Mellon University Pittsburgh, PA May, 2017 Copyright ©2017, Kevin K. Chang Abstract Over the past two decades, the storage capacity and access bandwidth of main memory have improved tremendously, by 128x and 20x, respectively. These improvements are mainly due to the continuous technology scaling of DRAM (dynamic random-access memory), which has been used as the physical substrate for main memory. In stark contrast with capacity and bandwidth, DRAM latency has remained almost constant, reducing by only 1.3x in the same time frame. Therefore, long DRAM latency continues to be a critical performance bot- tleneck in modern systems. Increasing core counts, and the emergence of increasingly more data-intensive and latency-critical applications further stress the importance of providing low-latency memory access. In this dissertation, we identify three main problems that contribute significantly to long latency of DRAM accesses. To address these problems, we present a series of new techniques. Our new techniques significantly improve both system performance and energy efficiency. We also examine the critical relationship between supply voltage and latency in modern DRAM chips and develop new mechanisms that exploit this voltage-latency trade-off to improve energy efficiency. First, while bulk data movement is a key operation in many applications and operating systems, contemporary systems perform this movement inefficiently, by transferring data from DRAM to the processor, and then back to DRAM, across a narrow off-chip channel. -

Which DDR SDRAM Memory to Use and When

WHITE PAPER Which DDR SDRAM Memory to Use and When Author Overview Vadhiraj Sankaranarayanan Memory performance is a critical component for achieving the desired system performance in Sr. Technical Marketing Manager, a wide range of applications from cloud computing and artificial intelligence (AI) to automotive Synopsys and mobile. Dual Data Rate Synchronous Dynamic Random-access Memory (DDR SDRAM) or simply DRAM has emerged as the de facto memory technology for the main memory due to its many advantages: high density with simplistic architecture using a capacitor as a storage element, low latency and high performance, almost infinite access endurance, and low power. The Joint Electron Device Engineering Council (JEDEC) has defined several DRAM categories of standards to meet the power, performance, and area requirements of each application. Selecting the right memory solution is often the most critical decision for obtaining the optimal system performance. This whitepaper provides an overview of the JEDEC memory standards to help SoC designers select the right memory solution, including IP, that best fits their application requirements. DDR DRAM Standards The primary function of main memory in an SoC is to feed the host – CPUs and GPUs – with the necessary data or instructions as quickly and reliably as possible. While the demand for high performance is increasing, more cores and functionality are added to the System-on-Chip (SoC) that is growing the need to keep the overall silicon footprint small and system power down. DDR DRAMs meet these memory requirements better than any other storage technologies overall, by offering a dense, high-performance, low-power memory solution. -

Memory Technology Evolution Technology Profile, 3Rd Edition

Memory technology evolution technology profile, 3rd edition System memory is arguably the most important component in servers and workstations. Processors use system memory to temporarily store the operating system, mission-critical applications, and the data they use and manipulate. Applications cannot effectively use the full computing power of the processor if the processor must wait for data from system memory. Therefore, both the performance of the applications and reliability of the data are intrinsically tied to system memory. These factors have driven the evolution of system memory from asynchronous dynamic random access memory (DRAM) technologies to high-bandwidth synchronous DRAM (SDRAM) technologies. Still, system memory bandwidth has not kept pace with improvements in processor performance. This technology profile describes SDRAM and identifies some of the newest memory technologies that HP is evaluating for servers and workstations. For more information, read the HP technology brief “Memory technology evolution: an overview of system memory technologies” available on www.hp.com. SDRAM The Joint Electronic Device Engineering Council (JEDEC)—the electronics industry standards agency— developed the SDRAM standard to speed up system memory. By using a memory bus clock to synchronize the input and output signals on the memory chips, SDRAM simplifies the memory controller and reduces the latency from CPU to memory. SDRAM accelerates data retrieval and increases memory capacity also by use of burst mode access, multiple memory banks, greater bandwidth, and register logic chips (registers). Although use of SDRAM improves overall system performance, there remains a growing performance gap between the memory and processor. That gap must be filled by more advanced memory technologies, including three generations of Double Data Rate (DDR) SDRAM, Rambus DRAM, and a new bi-directional serial interface called Fully Buffered DIMM. -

DDR3 Design Requirements for Keystone Devices

Application Report SPRABI1C–August 2011–Revised January 2018 DDR3 Design Requirements for KeyStone Devices .......................................................................................... High-Performance and Multicore Processors ABSTRACT This application report provides implementation instructions for the DDR3 interface incorporated in the Texas Instruments (TI) KeyStone series of DSP devices. The DDR3 interface supports 1600 MT/s and lower memory speeds in a variety of topologies. For supported speeds, see the specific-device data manual. This document assumes that you have a familiarization with DRAM implementation concepts and constraints. Contents 1 Introduction ................................................................................................................... 2 2 Background ................................................................................................................... 2 3 Migrating Designs from DDR2 to DDR3 (Features and Comparisons)............................................... 2 4 Prerequisites.................................................................................................................. 6 5 Package Selection ......................................................................................................... 13 6 Physical Design and Implementation .................................................................................... 14 7 Simulation and Modeling ................................................................................................. -

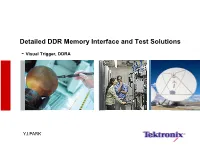

Burst Length : A0~A2 2

Detailed DDR Memory Interface and Test Solutions - Visual Trigger, DDRA YJ.PARK AGENDA . DRAM Technologies – DDR Memory Trends – DDR theory – Visual trigger – DDRA Band Group #1 |A| |A| Band #1 Band #2 Band #3 t DAC t f DDR Memory Trends Memory Technology – Quick Overview . DRAM - dominant memory technology – Computer system memory SDRAM Standards – Server, desktop, laptop Data – Dynamic, volatile memory, plug-in DIMMs SDRAM Rate Clock VDD – Embedded systems MT/S MHz V – Cell phones, printers, cars DDR-266 266 133 2.5 – Fixed memory configuration DDR-333 333 166 2.5 – DRAM driven by faster processors, faster data DDR-400 400 200 2.5 rates DDR2-400 400 200 1.8 – DDR3 now available at 1600 (1.6Gb/s) data rates – DDR3 over 2000 emerging(overclocked) DDR2-533 533 267 1.8 – DDR4 ~3200MT/S DDR2-667 667 334 1.8 . DRAM variants DDR2-800 800 400 1.8 – LPDDR – Low Power DDR DDR2-1066 1066 533 1.8 – Power savings for portable computing DDR3-800 800 400 1.5 – GDDR – Graphic DDR DDR3-1066 1066 533 1.5 – Optimized for Speed - faster access DDR3-1333 1333 667 1.5 DDR3-1600 1600 800 1.5 SDRAM Standards DDR Memory Trends . DDR Market Adoption – DDR2 Widely available in many speeds, densities, form factors – DDR3 speeds from 800MT/s to 1600MT/s(over 2000MT/s) – DDR3 higher rates under development . DDR4 specification expected to be released by Mid to late 2012 timeframe . High speed measurements techniques and higher performance measurement tools need to be applied . Parallel buses reaching the speeds of serial technology : Memory Clock speeds reaching >1GHz – Tighter timing margins – Crosstalk, impedance, and jitter management Courtesy Samsung DDR Analog Verification & Debug Signal Access - Probing . -

An Overview of System Memory Technologies Technology Brief, 9Th Edition

Memory technology evolution: an overview of system memory technologies Technology brief, 9th edition Introduction ......................................................................................................................................... 2 Basic DRAM operation ......................................................................................................................... 2 DRAM storage density and power consumption ................................................................................... 4 Memory access time ......................................................................................................................... 4 System bus timing ............................................................................................................................. 4 Memory bus speed ........................................................................................................................... 5 Burst mode access ............................................................................................................................ 5 SDRAM technology .............................................................................................................................. 5 Bank interleaving ............................................................................................................................. 6 Increased bandwidth ........................................................................................................................ 6 Registered SDRAM modules -

Next Generation Memory Interfaces - Deserializer

Next Generation Memory Interfaces - Deserializer Miron Veryanskiy Kyle Dillon Kalika Saxena Sinan Liu Chenyang Xu Elad Alon Vladimir Stojanovic Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2015-111 http://www.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-111.html May 14, 2015 Copyright © 2015, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Acknowledgement Thank you dearly Elad Alon and Vladimir Stojanovic. It has been nothing short of an absolutely incredible journey working on this capstone under both of your supervision. I want to thank my team, Kyle Dillon, Sinan Liu, Kalika Saxena, Chenyang Xu for being right there in the ranks along my side. I want to thank all of my friends and family who believed in my abilities, and encouraged me to pursue my ambitions. You saw in more in me than I can comfortably accept credit for. Finally, I would like to thank UC Berkeley and its extraordinary community. The experiences and lessons that I learned during my time at Cal will forever be with me. I will carry these lessons with me far beyond the boundaries of your gates. University of California, Berkeley College of Engineering MASTER OF ENGINEERING - SPRING 2015 Electrical Engineering & Computer Science Integrated Circuits & Physical Electronics NEXT GENERATION MEMORY INTERFACES - DESERIALIZER MIRON VERYANSKIY This Masters Project Paper fulfills the Master of Engineering degree requirement. -

(12) United States Patent (10) Patent No.: US 8,990.489 B2 Amidi Et Al

US00899.0489B2 (12) United States Patent (10) Patent No.: US 8,990.489 B2 Amidi et al. (45) Date of Patent: Mar. 24, 2015 (54) MULTI-RANK MEMORY MODULE THAT (56) References Cited EMULATES A MEMORY MODULE HAVINGA DIFFERENT NUMBER OF RANKS U.S. PATENT DOCUMENTS 4,249,253 A 2f1981 Gentili et al. (75) Inventors: Hossein Amidi, Lake Forest, CA (US); 4,368,515 A 1/1983 Nielsen Kelvin A. Marino, Laguna Hills, CA 4,392.212 A 7/1983 Miyasaka et al. (US); Satyadev Kolli, Milpitas, CA (US) 4,571,676 A 2f1986 Mantellina et al. 4,592,011 A 5/1986 Mantellina et al. Assignee: SMART Modular Technologies, Inc., 4,633,429 A 12/1986 Lewandowski et al. (73) 4,670,748 A 6, 1987 Williams Newark, CA (US) 4.866,603 A 9, 1989 Chiba 4,958,322 A 9/1990 Kosugi et al. (*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 (Continued) U.S.C. 154(b) by 0 days. FOREIGN PATENT DOCUMENTS (21) Appl. No.: 13/568,694 JP 09237492 A 9, 1997 JP 1032O270 A 12/1998 Filed: Aug. 7, 2012 (22) (Continued) (65) Prior Publication Data OTHER PUBLICATIONS US 2013/OO36264 A1 Feb. 7, 2013 “8M-Word by 64-bit Synchronous Dynamic RAM Module Unbuf Related U.S. Application Data fered Type', NEC Corporation, MOS Integrated Circuit MC-458CB646. (1997), 16 pgs. (63) Continuation of application No. 10/752,151, filed on Jan. 5, 2004, now Pat. No. 8,250,295. (Continued) (51) Int. -

Improving System Energy Efficiency with Memory Rank Subsetting

Improving System Energy Efficiency with Memory Rank Subsetting JUNG HO AHN, SeoulNationalUniversity NORMAN P. JOUPPI, Hewlett-Packard Labs CHRISTOS KOZYRAKIS and JACOB LEVERICH, Stanford University ROBERT S. SCHREIBER, Hewlett-Packard Labs VLSI process technology scaling has enabled dramatic improvements in the capacity and peak bandwidth of DRAM devices. However, current standard DDRx DIMM memory interfaces are not well tailored to achieve high energy efficiency and performance in modern chip-multiprocessor-based computer systems. Their suboptimal performance and energy inefficiency can have a significant impact on system-wide efficiency since much of the system power dissipation is due to memory power. New memory interfaces, better suited for future many-core systems, are needed. In response, there are recent proposals to enhance the energy efficiency of main-memory systems by dividing a memory rank into subsets, and making a subset rather than a whole rank serve a memory request. We holistically assess the effectiveness of rank subsetting from system-wide performance, energy- efficiency, and reliability perspectives. We identify the impact of rank subsetting on memory power and processor performance analytically, compare two promising rank-subsetting proposals, Multicore DIMM and mini-rank, and verify our analysis by simulating a chip-multiprocessor system using multithreaded 4 and consolidated workloads. We extend the design of Multicore DIMM for high-reliability systems and show that compared with conventional chipkill approaches, rank subsetting can lead to much higher system-level energy efficiency and performance at the cost of additional DRAM devices. This holistic assessment shows that rank subsetting offers compelling alternatives to existing processor-memory interfaces for future DDR systems.