History of Electronic Computers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

May 21St at the Time, the EDSAC Used IBM 726 Three Small Cathode Ray Tube Börje Langefors Screens to Display the State of Its Announced Memory

it played tic-tac-toe (known as Noughts and Crosses in the UK). May 21st At the time, the EDSAC used IBM 726 three small cathode ray tube Börje Langefors screens to display the state of its Announced memory. Each one could draw a May 21, 1952 Born: May 21, 1915; grid of 35 x 16 dots. Douglas re- purposed one of them for his Ystad, Sweden The IBM 726 was the company’s game, and obtained input (i.e. Died: Dec. 13, 2009 first magnetic tape unit, where to place a nought or intended for use with the Langefors developed the cross) via EDSAC’s rotary recently announced IBM 701 ‘infological equation’ in 1980, controller. [April 7], the company’s first which describes the difference electronic computer. between information and data in terms of additional semantic The 726 utilized half-inch tapes background and a with seven tracks. Six were for communication time interval. the data and the seventh was employed as a parity track. Langefors joined SAAB, the Some tapes were 1,200 feet long, Swedish aerospace and defense could store 2.3 MB of data, and company, in 1949 where he IBM claimed that just one could utilized analog devices for replace 12,500 punch cards. calculating wing stresses. The need for more powerful tools The drive could write 100 became evident, and the only characters per inch on a tape Swedish computer of the time, EDSAC CRT Tubes. Computer and read 75 inches per second. the BESK [April 1], was Lab, Univ. of Cambridge. CC BY To withstand the system’s fast insufficient for the task. -

"Computers" Abacus—The First Calculator

Component 4: Introduction to Information and Computer Science Unit 1: Basic Computing Concepts, Including History Lecture 4 BMI540/640 Week 1 This material was developed by Oregon Health & Science University, funded by the Department of Health and Human Services, Office of the National Coordinator for Health Information Technology under Award Number IU24OC000015. The First "Computers" • The word "computer" was first recorded in 1613 • Referred to a person who performed calculations • Evidence of counting is traced to at least 35,000 BC Ishango Bone Tally Stick: Science Museum of Brussels Component 4/Unit 1-4 Health IT Workforce Curriculum 2 Version 2.0/Spring 2011 Abacus—The First Calculator • Invented by Babylonians in 2400 BC — many subsequent versions • Used for counting before there were written numbers • Still used today The Chinese Lee Abacus http://www.ee.ryerson.ca/~elf/abacus/ Component 4/Unit 1-4 Health IT Workforce Curriculum 3 Version 2.0/Spring 2011 1 Slide Rules John Napier William Oughtred • By the Middle Ages, number systems were developed • John Napier discovered/developed logarithms at the turn of the 17 th century • William Oughtred used logarithms to invent the slide rude in 1621 in England • Used for multiplication, division, logarithms, roots, trigonometric functions • Used until early 70s when electronic calculators became available Component 4/Unit 1-4 Health IT Workforce Curriculum 4 Version 2.0/Spring 2011 Mechanical Computers • Use mechanical parts to automate calculations • Limited operations • First one was the ancient Antikythera computer from 150 BC Used gears to calculate position of sun and moon Fragment of Antikythera mechanism Component 4/Unit 1-4 Health IT Workforce Curriculum 5 Version 2.0/Spring 2011 Leonardo da Vinci 1452-1519, Italy Leonardo da Vinci • Two notebooks discovered in 1967 showed drawings for a mechanical calculator • A replica was built soon after Leonardo da Vinci's notes and the replica The Controversial Replica of Leonardo da Vinci's Adding Machine . -

UNIVAC I Computer System

Saved from the Internet on 3/9/2010 Created by Allan Reiter UNIVAC I Computer System After you look at this yellow page go to the blue page to find out how UNIVAC I really worked. My name is Allan Reiter and in 1954 began my career with a company in St Paul, Minnesota called Engineering Research Associates (ERA) that was part of the Remington Rand Corporation. I was hired with 3 friends, Paul S. Lawson, Vernon Sandoz, and Robert Kress. We were buddies who met in the USAF where we were trained and worked on airborne radar on B-50 airplanes. In a way this was the start of our computer career because the radar was controlled by an analog computer known as the Q- 24. After discharge from the USAF Paul from Indiana and Vernon from Texas drove up to Minnesota to visit me. They said they were looking for jobs. We picked up a newspaper and noticed an ad that sounded interesting and decided to check it out. The ad said they wanted people with military experience in electronics. All three of us were hired at 1902 West Minnehaha in St. Paul. We then looked up Robert Kress (from Iowa) and he was hired a few days later. The four of us then left for Philadelphia with three cars and one wife. Robert took his wife Brenda along. This was where the UNIVAC I was being built. Parts of the production facilities were on an upper floor of a Pep Boys building. Another building on Allegheny Avenue had a hydraulic elevator operated with water pressure. -

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

High Performance Decimal Floating-Point Units

UNIVERSIDADE DE SANTIAGO DE COMPOSTELA DEPARTAMENTO DE ELECTRONICA´ E COMPUTACION´ PhD. Dissertation High-Performance Decimal Floating-Point Units Alvaro´ Vazquez´ Alvarez´ Santiago de Compostela, January 2009 To my family A´ mina˜ familia Acknowledgements It has been a long way to see this thesis successfully concluded, at least longer than what I imagined it. Perhaps the moment to thank and acknowledge everyone’s contributions is the most eagerly awaited. This thesis could not have been possible without the support of several people and organizations whose contributions I am very grateful. First of all, I want to express my sincere gratitude to my thesis advisor, Elisardo Antelo. Specially, I would like to emphasize the invaluable support he offered to me all these years. His ideas and contributions have a major influence on this thesis. I would like to thank all people in the Departamento de Electronica´ e Computacion´ for the material and personal help they gave me to carry out this thesis, and for providing a friendly place to work. In particular, I would like to mention to Prof. Javier D. Bruguera and the other staff of the Computer Architecture Group. Many thanks to Paula, David, Pichel, Marcos, Juanjo, Oscar,´ Roberto and my other workmates for their friendship and help. I am very grateful to IBM Germany for their financial support though a one-year research contract. I would like to thank Ralf Fischer, lead of hardware development, and Peter Roth and Stefan Wald, team managers at IBM Deutchland Entwicklung in Boblingen.¨ I would like to extend my gratitude to the FPU design team, in special to Silvia Muller¨ and Michael Kroner,¨ for their help and the warm welcome I received during my stay in Boblingen.¨ I would also like to thank Eric Schwarz from IBM for his support. -

Technical Details of the Elliott 152 and 153

Appendix 1 Technical Details of the Elliott 152 and 153 Introduction The Elliott 152 computer was part of the Admiralty’s MRS5 (medium range system 5) naval gunnery project, described in Chap. 2. The Elliott 153 computer, also known as the D/F (direction-finding) computer, was built for GCHQ and the Admiralty as described in Chap. 3. The information in this appendix is intended to supplement the overall descriptions of the machines as given in Chaps. 2 and 3. A1.1 The Elliott 152 Work on the MRS5 contract at Borehamwood began in October 1946 and was essen- tially finished in 1950. Novel target-tracking radar was at the heart of the project, the radar being synchronized to the computer’s clock. In his enthusiasm for perfecting the radar technology, John Coales seems to have spent little time on what we would now call an overall systems design. When Harry Carpenter joined the staff of the Computing Division at Borehamwood on 1 January 1949, he recalls that nobody had yet defined the way in which the control program, running on the 152 computer, would interface with guns and radar. Furthermore, nobody yet appeared to be working on the computational algorithms necessary for three-dimensional trajectory predic- tion. As for the guns that the MRS5 system was intended to control, not even the basic ballistics parameters seemed to be known with any accuracy at Borehamwood [1, 2]. A1.1.1 Communication and Data-Rate The physical separation, between radar in the Borehamwood car park and digital computer in the laboratory, necessitated an interconnecting cable of about 150 m in length. -

Fully Redundant Decimal Arithmetic

2009 19th IEEE International Symposium on Computer Arithmetic Fully Redundant Decimal Arithmetic Saeid Gorgin and Ghassem Jaberipur Dept. of Electrical & Computer Engr., Shahid Beheshti Univ. and School of Computer Science, institute for research in fundamental sciences (IPM), Tehran, Iran [email protected], [email protected] Abstract In both decimal and binary arithmetic, partial products in multipliers and partial remainders in Hardware implementation of all the basic radix-10 dividers are often represented via a redundant number arithmetic operations is evolving as a new trend in the system (e.g., Binary signed digit [11], decimal carry- design and implementation of general purpose digital save [5], double-decimal [6], and minimally redundant processors. Redundant representation of partial decimal [9]). Such use of redundant digit sets, where products and remainders is common in the the number of digits is sufficiently more than the radix, multiplication and division hardware algorithms, allows for carry-free addition and subtraction as the respectively. Carry-free implementation of the more basic operations that build-up the product and frequent add/subtract operations, with the byproduct of remainder, respectively. In the aforementioned works enhancing the speed of multiplication and division, is on decimal multipliers and dividers, inputs and outputs possible with redundant number representation. are nonredundant decimal numbers. However, a However, conversion of redundant results to redundant representation is used for the intermediate conventional representations entails slow carry partial products or remainders. The intermediate propagation that can be avoided if the results are kept additions and subtractions are semi-redundant in redundant format for later use as operands of other operations in that only one of the operands as well as arithmetic operations. -

An Early Program Proof by Alan Turing F

An Early Program Proof by Alan Turing F. L. MORRIS AND C. B. JONES The paper reproduces, with typographical corrections and comments, a 7 949 paper by Alan Turing that foreshadows much subsequent work in program proving. Categories and Subject Descriptors: 0.2.4 [Software Engineeringj- correctness proofs; F.3.1 [Logics and Meanings of Programs]-assertions; K.2 [History of Computing]-software General Terms: Verification Additional Key Words and Phrases: A. M. Turing Introduction The standard references for work on program proofs b) have been omitted in the commentary, and ten attribute the early statement of direction to John other identifiers are written incorrectly. It would ap- McCarthy (e.g., McCarthy 1963); the first workable pear to be worth correcting these errors and com- methods to Peter Naur (1966) and Robert Floyd menting on the proof from the viewpoint of subse- (1967); and the provision of more formal systems to quent work on program proofs. C. A. R. Hoare (1969) and Edsger Dijkstra (1976). The Turing delivered this paper in June 1949, at the early papers of some of the computing pioneers, how- inaugural conference of the EDSAC, the computer at ever, show an awareness of the need for proofs of Cambridge University built under the direction of program correctness and even present workable meth- Maurice V. Wilkes. Turing had been writing programs ods (e.g., Goldstine and von Neumann 1947; Turing for an electronic computer since the end of 1945-at 1949). first for the proposed ACE, the computer project at the The 1949 paper by Alan M. -

Law and Military Operations in Kosovo: 1999-2001, Lessons Learned For

LAW AND MILITARY OPERATIONS IN KOSOVO: 1999-2001 LESSONS LEARNED FOR JUDGE ADVOCATES Center for Law and Military Operations (CLAMO) The Judge Advocate General’s School United States Army Charlottesville, Virginia CENTER FOR LAW AND MILITARY OPERATIONS (CLAMO) Director COL David E. Graham Deputy Director LTC Stuart W. Risch Director, Domestic Operational Law (vacant) Director, Training & Support CPT Alton L. (Larry) Gwaltney, III Marine Representative Maj Cody M. Weston, USMC Advanced Operational Law Studies Fellows MAJ Keith E. Puls MAJ Daniel G. Jordan Automation Technician Mr. Ben R. Morgan Training Centers LTC Richard M. Whitaker Battle Command Training Program LTC James W. Herring Battle Command Training Program MAJ Phillip W. Jussell Battle Command Training Program CPT Michael L. Roberts Combat Maneuver Training Center MAJ Michael P. Ryan Joint Readiness Training Center CPT Peter R. Hayden Joint Readiness Training Center CPT Mark D. Matthews Joint Readiness Training Center SFC Michael A. Pascua Joint Readiness Training Center CPT Jonathan Howard National Training Center CPT Charles J. Kovats National Training Center Contact the Center The Center’s mission is to examine legal issues that arise during all phases of military operations and to devise training and resource strategies for addressing those issues. It seeks to fulfill this mission in five ways. First, it is the central repository within The Judge Advocate General's Corps for all-source data, information, memoranda, after-action materials and lessons learned pertaining to legal support to operations, foreign and domestic. Second, it supports judge advocates by analyzing all data and information, developing lessons learned across all military legal disciplines, and by disseminating these lessons learned and other operational information to the Army, Marine Corps, and Joint communities through publications, instruction, training, and databases accessible to operational forces, world-wide. -

Algorithms and Architectures for Decimal Transcendental Function Computation

Algorithms and Architectures for Decimal Transcendental Function Computation A Thesis Submitted to the College of Graduate Studies and Research in Partial Fulfillment of the Requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering University of Saskatchewan Saskatoon, Saskatchewan, Canada By Dongdong Chen c Dongdong Chen, January, 2011. All rights reserved. Permission to Use In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis. Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to: Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan Canada S7N 5A9 i Abstract Nowadays, there are many commercial demands for decimal floating-point (DFP) arith- metic operations such as financial analysis, tax calculation, currency conversion, Internet based applications, and e-commerce. -

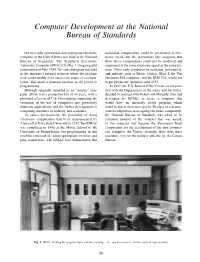

Computer Development at the National Bureau of Standards

Computer Development at the National Bureau of Standards The first fully operational stored-program electronic individual computations could be performed at elec- computer in the United States was built at the National tronic speed, but the instructions (the program) that Bureau of Standards. The Standards Electronic drove these computations could not be modified and Automatic Computer (SEAC) [1] (Fig. 1.) began useful sequenced at the same electronic speed as the computa- computation in May 1950. The stored program was held tions. Other early computers in academia, government, in the machine’s internal memory where the machine and industry, such as Edvac, Ordvac, Illiac I, the Von itself could modify it for successive stages of a compu- Neumann IAS computer, and the IBM 701, would not tation. This made a dramatic increase in the power of begin productive operation until 1952. programming. In 1947, the U.S. Bureau of the Census, in coopera- Although originally intended as an “interim” com- tion with the Departments of the Army and Air Force, puter, SEAC had a productive life of 14 years, with a decided to contract with Eckert and Mauchly, who had profound effect on all U.S. Government computing, the developed the ENIAC, to create a computer that extension of the use of computers into previously would have an internally stored program which unknown applications, and the further development of could be run at electronic speeds. Because of a demon- computing machines in industry and academia. strated competence in designing electronic components, In earlier developments, the possibility of doing the National Bureau of Standards was asked to be electronic computation had been demonstrated by technical monitor of the contract that was issued, Atanasoff at Iowa State University in 1937. -

The ABC of Computing

COMMENT BOOKS & ARTS teamed up with recent graduate Clifford DEPT Berry to develop the system that became S ON known as the Atanasoff–Berry Computer I (ABC). Built on a shoestring budget, the ECT LL O C simple ‘breadboard’ prototype that emerged L A contained significant innovations. These I included the use of vacuum tubes as the com- B./SPEC puting mechanism and operating memory; I V. L V. binary and logical calculation; serial com- I putation; and the use of capacitors as storage memory. By the summer of 1940, Smiley tells us, a second, more-developed prototype was UN STATE IOWA running and Atanasoff and Berry had writ- ten a 35-page manuscript describing it. Other people were working on similar devices. In the United Kingdom and at Princeton University in New Jersey, Turing was investigating practical outlets for the concepts in his 1936 paper ‘On Comput- able Numbers’. In London, British engineer Tommy Flowers was using vacuum tubes as electronic switches for telephone exchanges in the General Post Office. In Germany, Konrad Zuse was working on a floating-point calculator — albeit based on electromechani- cal technology — that would have a 64-word The 1940s Atanasoff–Berry Computer (ABC) was the first to use innovations such as vacuum tubes. storage capacity by 1941. Smiley weaves these stories into the narrative effectively, giving a BIOGRAPHY broad sense of the rich ecology of thought that burgeoned during this crucial period of technological and logical development. The Second World War changed every- The ABC of thing. Atanasoff left Iowa State to work in the Naval Ordnance Laboratory in Washing- ton DC.