ADSP-TS201 Tigersharc Processor Hardware Reference, Revision 1.0, November 2004

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Freenas® 11.0 User Guide

FreeNAS® 11.0 User Guide June 2017 Edition FreeNAS® IS © 2011-2017 iXsystems FreeNAS® AND THE FreeNAS® LOGO ARE REGISTERED TRADEMARKS OF iXsystems FreeBSD® IS A REGISTERED TRADEMARK OF THE FreeBSD Foundation WRITTEN BY USERS OF THE FreeNAS® network-attached STORAGE OPERATING system. VERSION 11.0 CopYRIGHT © 2011-2017 iXsystems (https://www.ixsystems.com/) CONTENTS WELCOME....................................................1 TYPOGRAPHIC Conventions...........................................2 1 INTRODUCTION 3 1.1 NeW FeaturES IN 11.0..........................................3 1.2 HarDWARE Recommendations.....................................4 1.2.1 RAM...............................................5 1.2.2 The OperATING System DeVICE.................................5 1.2.3 StorAGE Disks AND ContrOLLERS.................................6 1.2.4 Network INTERFACES.......................................7 1.3 Getting Started WITH ZFS........................................8 2 INSTALLING AND UpgrADING 9 2.1 Getting FreeNAS® ............................................9 2.2 PrEPARING THE Media.......................................... 10 2.2.1 On FreeBSD OR Linux...................................... 10 2.2.2 On WindoWS.......................................... 11 2.2.3 On OS X............................................. 11 2.3 Performing THE INSTALLATION....................................... 12 2.4 INSTALLATION TROUBLESHOOTING...................................... 18 2.5 UpgrADING................................................ 19 2.5.1 Caveats:............................................ -

Tigersharc DSP Hardware Specification, Revision 1.0.2, Direct Memory Access

7 DIRECT MEMORY ACCESS Figure 7-0. Table 7-0. Listing 7-0. Overview Direct Memory Access (DMA) is a mechanism for transferring data with- out core being involved. The TigerSHARC® DSP’s on-chip DMA controller relieves the core processor of the burden of moving data between internal memory and an external device, external memory, or between link ports and internal or external memory. The fully-integrated DMA controller allows the TigerSHARC® DSP core processor, or an external device, to specify data transfer operations and return to normal processing while the DMA controller carries out the data transfers in the background. The TigerSHARC® DSP DMA competes with other masters for internal memory access. For more information, see “Architecture and Microarchi- tecture Overview” on page 6-7. This conflict is minimized due to the large internal memory bandwidth that is available. The DMA includes 14 DMA channels, four of which are dedicated to external memory devices, eight to link ports, and two to AutoDMA registers. TigerSHARC DSP Hardware Specification 7 - 1 Overview Figure 7-1 shows a block diagram of the TigerSHARC® DSP’s DMA controller. TRANSMITTER RECEIVER TCB TCB REGISTERS REGISTERS Internal DMA DMA CONTROLLER Bus Requests Interface Figure 7-1. DMA Block Diagram Data Transfers — General Information The DMA controller can perform several types of data transfers: • Internal memory ⇒ external memory and memory-mapped periph- erals • Internal memory ⇒ internal memory of other TigerSHARC® DSPs residing on the cluster bus • Internal memory ⇒ host processor • Internal memory ⇒ link port I/O • External memory ⇒ external peripherals 7 - 2 TigerSHARC DSP Hardware Specification Direct Memory Access • External memory ⇒ internal memory • External memory ⇒ link port I/O • Link port I/O ⇒ internal memory • Link port I/O ⇒ external memory • Cluster bus master via AutoDMA registers ⇒ internal memory Internal-to-internal memory transfers are not directly supported. -

Performance, Scalability on the Server Side

Performance, Scalability on the Server Side John VanDyk Presented at Des Moines Web Geeks 9/21/2009 Who is this guy? History • Apple // • Macintosh • Windows 3.1- Server 2008R2 • Digital Unix (Tru64) • Linux (primarily RHEL) • FreeBSD Systems Iʼve worked with over the years. Languages • Perl • Userland Frontier™ • Python • Java • Ruby • PHP Languages Iʼve worked with over the years (Userland Frontier™ʼs integrated language is UserTalk™) Open source developer since 2000 Perl/Python/PHP MySQL Apache Linux The LAMP stack. Time to Serve Request Number of Clients Performance vs. scalability. network in network out RAM CPU Storage These are the basic laws of physics. All bottlenecks are caused by one of these four resources. Disk-bound •To o l s •iostat •vmstat Determine if you are disk-bound by measuring throughput. vmstat (BSD) procs memory page disk faults cpu r b w avm fre flt re pi po fr sr tw0 in sy cs us sy id 0 2 0 799M 842M 27 0 0 0 12 0 23 344 2906 1549 1 1 98 3 3 0 869M 789M 5045 0 0 0 406 0 10 1311 17200 5301 12 4 84 3 5 0 923M 794M 5219 0 0 0 5178 0 27 1825 21496 6903 35 8 57 1 2 0 931M 784M 909 0 0 0 146 0 12 955 9157 3570 8 4 88 blocked plenty of RAM, idle processes no swapping CPUs A disk-bound FreeBSD machine. b = blocked for resources fr = pages freed/sec cs = context switches avm = active virtual pages in = interrupts flt = memory page faults sy = system calls per interval vmstat (RHEL5) # vmstat -S M 5 25 procs ---------memory-------- --swap- ---io--- --system- -----cpu------ r b swpd free buff cache si so bi bo in cs us sy id wa st 1 0 0 1301 194 5531 0 0 0 29 1454 2256 24 20 56 0 0 3 0 0 1257 194 5531 0 0 0 40 2087 2336 34 27 39 0 0 2 0 0 1183 194 5531 0 0 0 53 1658 2763 33 28 39 0 0 0 0 0 1344 194 5531 0 0 0 34 1807 2125 29 19 52 0 0 no blocked busy but not processes overloaded CPU in = interrupts/sec cs = context switches/sec wa = time waiting for I/O Solving disk bottlenecks • Separate spindles (logs and databases) • Get rid of atime updates! • Minimize writes • Move temp writes to /dev/shm Overview of what weʼre about to dive into. -

Xcode Package from App Store

KH Computational Physics- 2016 Introduction Setting up your computing environment Installation • MAC or Linux are the preferred operating system in this course on scientific computing. • Windows can be used, but the most important programs must be installed – python : There is a nice package ”Enthought Python Distribution” http://www.enthought.com/products/edudownload.php – C++ and Fortran compiler – BLAS&LAPACK for linear algebra – plotting program such as gnuplot Kristjan Haule, 2016 –1– KH Computational Physics- 2016 Introduction Software for this course: Essentials: • Python, and its packages in particular numpy, scipy, matplotlib • C++ compiler such as gcc • Text editor for coding (for example Emacs, Aquamacs, Enthought’s IDLE) • make to execute makefiles Highly Recommended: • Fortran compiler, such as gfortran or intel fortran • BLAS& LAPACK library for linear algebra (most likely provided by vendor) • open mp enabled fortran and C++ compiler Useful: • gnuplot for fast plotting. • gsl (Gnu scientific library) for implementation of various scientific algorithms. Kristjan Haule, 2016 –2– KH Computational Physics- 2016 Introduction Installation on MAC • Install Xcode package from App Store. • Install ‘‘Command Line Tools’’ from Apple’s software site. For Mavericks and lafter, open Xcode program, and choose from the menu Xcode -> Open Developer Tool -> More Developer Tools... You will be linked to the Apple page that allows you to access downloads for Xcode. You wil have to register as a developer (free). Search for the Xcode Command Line Tools in the search box in the upper left. Download and install the correct version of the Command Line Tools, for example for OS ”El Capitan” and Xcode 7.2, Kristjan Haule, 2016 –3– KH Computational Physics- 2016 Introduction you need Command Line Tools OS X 10.11 for Xcode 7.2 Apple’s Xcode contains many libraries and compilers for Mac systems. -

David Gwynne <[email protected]>

firewalling with OpenBSD's pf and pfsync David Gwynne <[email protected]> Thursday, 17 January 13 introduction ‣ who am i? ‣ what is openbsd? ‣ what are pf and pfsync? ‣ how do i use them? ‣ ask questions whenever you want Thursday, 17 January 13 who am i? ‣ infrastructure architect in EAIT at UQ ‣ i do stuff, including run the firewalls ‣ a core developer in openbsd ‣ i generally play with storage ‣ but i play with the network stack sometimes Thursday, 17 January 13 what is openbsd? ‣ open source general purpose unix-like operating system ‣ descended from the original UNIX by way of berkeley and netbsd ‣ aims for “portability, standardization, correctness, proactive security and integrated cryptography.” ‣ supports various architectures/platforms Thursday, 17 January 13 what is openbsd? ‣ one source tree for everything ‣ kernel, userland, doco ‣ bsd/isc/mit style licenses on all code (with some historical exceptions) ‣ 6 month dev cycle resulting in a release ‣ 3rd party software via a ports tree ‣ emergent focus on network services Thursday, 17 January 13 what is openbsd? ‣ it is very aggressive ‣ changes up and down the stack (compiler to kernel) to make a harsher, stricter, and less predictable runtime environment ‣ minimal or no backward compatibility as things move forward ‣ whole tree is checked for new bugs ‣ randomise as much as possible all over Thursday, 17 January 13 what is openbsd? ‣ it is extremely conservative ‣ tree must compile and work at all times ‣ big changes go in at the start of the cycle ‣ we’re not afraid to back stuff out ‣ peer review is necessary ‣ we do back away from some tweaks for the sake of usability Thursday, 17 January 13 what is pf? ‣ short for packet filter ‣ the successor to IP Filter (ipf) ‣ ipf was removed due to license issues ‣ the exec summary is that it is a stateful filter for IP (v4 and v6) traffic ‣ does a little bit more than that though.. -

Unix and Linux System Administration and Shell Programming

Unix and Linux System Administration and Shell Programming Unix and Linux System Administration and Shell Programming version 56 of August 12, 2014 Copyright © 1998, 1999, 2000, 2001, 2002, 2003, 2004, 2005, 2006, 2007, 2009, 2010, 2011, 2012, 2013, 2014 Milo This book includes material from the http://www.osdata.com/ website and the text book on computer programming. Distributed on the honor system. Print and read free for personal, non-profit, and/or educational purposes. If you like the book, you are encouraged to send a donation (U.S dollars) to Milo, PO Box 5237, Balboa Island, California, USA 92662. This is a work in progress. For the most up to date version, visit the website http://www.osdata.com/ and http://www.osdata.com/programming/shell/unixbook.pdf — Please add links from your website or Facebook page. Professors and Teachers: Feel free to take a copy of this PDF and make it available to your class (possibly through your academic website). This way everyone in your class will have the same copy (with the same page numbers) despite my continual updates. Please try to avoid posting it to the public internet (to avoid old copies confusing things) and take it down when the class ends. You can post the same or a newer version for each succeeding class. Please remove old copies after the class ends to prevent confusing the search engines. You can contact me with a specific version number and class end date and I will put it on my website. version 56 page 1 Unix and Linux System Administration and Shell Programming Unix and Linux Administration and Shell Programming chapter 0 This book looks at Unix (and Linux) shell programming and system administration. -

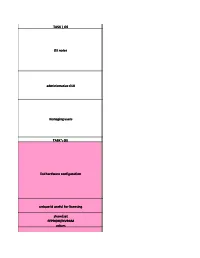

TASK \ OS TASK \ OS TASK \ OS Show/Set EEPROM

TASK \ OS OS notes administrative GUI managing users TASK \ OS list hardware configuration unique id useful for licensing show/set EEPROM/NVRAM values add device without reboot remove device tape device stdin/ stdout/ stderr X kvm config TASK \ OS read a disk label whole disk in partition label a disk partition a disk TASK \ OS kernel show/set kernel parameters limit physical memory loaded kernel modules load module unload module make disk bootable startup scripts start/ stop/ config services shutdown (& power off if possible) run levels 1 *=normal states for more detail see www.phildev.net/runlevels.html show runlevel 1 time zone info check swap space bind process to CPU TASK \ OS "normal" filesystem volume-based filesystem file system description volume manipulation create filesystem create non-0-length empty file mount CDROM eject CDROM create/mount ISO image ACL management Fibre Channel / SAN TASK \ OS NFS share definitions NFS share command NFS information name resolution order show network interface info change IP start DHCP client ping one packet sniff network route definitions telnetd, ftpd banner set date/time (from net: ntp or other) TASK \ OS auditing encrypted passwords in min password length allow/deny root logins firewall config TASK \ OS show installed software file is in which package add software precompiled binaries of GPLware and freeware C compiler show patch level and/or patches patch tool configure/show runtime linking fortran-2000.com/ ArnaudRecipes/ sharedlib.html link library path tracing utility define user defaults csh global .login default syslog and messages system error reporting tool performance monitoring match process to file or port X pop-up Wikipedia FAQs (see also faqs.org) mailing list mailing list archives man pages www.freebsd.org/ cgi/man.cgi newsgroup(s) and forums groups.google user groups magazines vendor home page vendor docs and patches (see also man pages) vendor phone (US) wikis FreeBSD Derived from 4.4BSD-Lite and 386BSD. -

NEWSLETTER April 2009

NEWSLETTER April 2009 In dieser Ausgabe: Produkte: Produkte: Die erste OEM-Version von SigmaPlot SigmaPlot Graphing API ermöglicht Integration von SigmaPlot Graphik- Funktionen in andere Anwendungen Artikel: “SigmaPlot 11 - jetzt auch mit Statistik” Dr. Thomas W. Beneke, Dr. Wolfgang W. Schwippert, in: PhysikJournal ”SigmaPlot 11: Now with Total SigmaStat Integration” John A. Wass, PhD, in: Scientific Computing International „User-defined transforms - useful feature of SigmaPlot“ Gerald Pöch, PhD, und Douglas A. Dawson, PhD, Download: kostenlose Demo-CD Veranstaltungen: Systat Software Online-Seminare Tech Tipps: Histogramm mit unregelmäßigen Intervallgrenzen Produkte Erste OEM-Version von SigmaPlot SigmaPlot Graphing API ermöglicht Integration von SigmaPlot Graphik-Funktionen in andere Anwendungen Systat Software, führender Hersteller wissenschaftlicher Softwareprogramme und –services, hat mit dem SigmaPlot Graphing API erstmalig eine eigenständige OEM-Version von SigmaPlot entwickelt, mit der Anwendungsentwickler SigmaPlots umfangreiche Graphik- Funktionen in ihre eigenen Programme oder Instrumente integrieren können. So können Anwendungen ohne weiteren Entwicklungsaufwand mit einem umfangreichen graphischen Funktionsangebot ausgestattet werden, das über 100 2D- und 3D-Graphtypen aufweist. Ebenso lassen sich Aufgaben wie routinemäßige Analysen durch den Einsatz individuell gestalteter Arbeitsbabläufe automatisieren. Seit über 20 Jahren auf dem Markt, wird SigmaPlot heute von weltweit mehr als 150.000 Wissenschaftlern, Forschern und -

Siarsv2 PF - Packet Filter

SIARSv2 PF - Packet Filter Peter N.M. Hansteen & Matthieu Herrb 18 octobre 2018 Agenda 1 Introduction 2 Utilisation simple 3 Syntaxe des règles 4 Quelques exemples de défense active avec PF 5 Exploitation quotidienne : logs, statistiques 6 Pfsync & Carp : ajout de redondance SIARSv2 - PF 2/62 Agenda 1 Introduction 2 Utilisation simple 3 Syntaxe des règles 4 Quelques exemples de défense active avec PF 5 Exploitation quotidienne : logs, statistiques 6 Pfsync & Carp : ajout de redondance SIARSv2 - PF 3/62 Qu’est-ce que PF ? Filtre de Paquets réseau niveau 3 Intervient sur le trafic entrant ou sortant d’une interface Permet de : I bloquer/autoriser le paquet à continuer son chemin I placer un label sur le paquet I modifier le paquet (NAT, ...) I re-diriger le paquet vers une autre destination SIARSv2 - PF 4/62 Filtrage à état (stateful) Les protocoles réseau sont gérés par des automates (exemple: TCP) PF suit l’état de l’automate pour les protocoles connus Cela permet de : I détecter les paquets qui violent le protocole I limiter la complexité des règles de filtrage en laissant passer automatiquement les paquets valides du protocole. I contrôler les ressources utilisées par le filtre SIARSv2 - PF 5/62 Règles de PF Stockées dans /etc/pf.conf S’appliquent au niveau 3 (IP, ICMP, TCP, UDP, ...) Lues dans l’ordre où elles apparaissent La dernière règle qui matche un paquet s’applique. (Attention : différent de Cisco / Linux ...) Si une règle modifie un paquet, le paquet modifié est utilisé en entrée des règles suivantes. Les tables permettent de traiter des listes dynamiques d’adresses IP SIARSv2 - PF 6/62 PF - traduction d’adresses réécriture des adresses source : NAT/PAT vers I une adresse unique I un pool d’adresses réécriture des adresses destination : redirection vers I un relais applicatif (hors du noyau) I équilibrage de charge traductions en cours stockées dans la table d’états des connexions. -

Contents in Detail

CONTENTS IN DETAIL FOREWORD by Bob Beck (from the first edition) xv ACKNOWLEDGMENTS xvii INTRODUCTION xix This Is Not a HOWTO ............................................... xx What This Book Covers .............................................. xx 1 BUILDING THE NETWORK YOU NEED 1 Your Network: High Performance, Low Maintenance, and Secure ................. 1 Where the Packet Filter Fits In .......................................... 3 The Rise of PF ..................................................... 3 If You Came from Elsewhere ........................................... 6 Pointers for Linux Users ........................................ 6 Frequently Answered Questions About PF............................ 7 A Little Encouragement: A PF Haiku ...................................... 9 2 PF CONFIGURATION BASICS 11 The First Step: Enabling PF ........................................... 12 Setting Up PF on OpenBSD .................................... 12 Setting Up PF on FreeBSD ..................................... 13 Setting Up PF on NetBSD ...................................... 15 A Simple PF Rule Set: A Single, Stand-Alone Machine ........................ 16 A Minimal Rule Set .......................................... 16 Testing the Rule Set . 18 Slightly Stricter: Using Lists and Macros for Readability........................ 18 A Stricter Baseline Rule Set..................................... 19 Reloading the Rule Set and Looking for Errors........................ 20 Checking Your Rules ......................................... 21 -

Proceedings of the General Track: 2004 USENIX Annual Technical Conference

USENIX Association Proceedings of the General Track: 2004 USENIX Annual Technical Conference Boston, MA, USA June 27–July 2, 2004 © 2004 by The USENIX Association All Rights Reserved For more information about the USENIX Association: Phone: 1 510 528 8649 FAX: 1 510 548 5738 Email: [email protected] WWW: http://www.usenix.org Rights to individual papers remain with the author or the author's employer. Permission is granted for noncommercial reproduction of the work for educational or research purposes. This copyright notice must be included in the reproduced paper. USENIX acknowledges all trademarks herein. Making the “Box” Transparent: System Call Performance as a First-class Result Yaoping Ruan and Vivek Pai Department of Computer Science Princeton University {yruan,vivek}@cs.princeton.edu Abstract and other networked systems, using kernel integration to For operating system intensive applications, the ability of avoid performance problems becomes unrealistic. As a re- designers to understand system call performance behavior sult, examining the interaction between operating systems is essential to achieving high performance. Conventional and user processes remains a useful area of investigation. performance tools, such as monitoring tools and profilers, Much of the earlier work focusing on the kernel-user in- collect and present their information off-line or via out-of- terface centered around developing new system calls that band channels. We believe that making this information are more closely tailored to the needs of particular appli- first-class and exposing it to applications via in-band chan- cations. In particular, zero-copy I/O [17, 31] and scal- nels on a per-call basis presents opportunities for perfor- able event delivery [9, 10, 23] are examples of techniques mance analysis and tuning not available via other mecha- that have been adopted in mainstream operating systems, nisms. -

The Book of PF Covers the Most • Stay in Control of Your Traffic with Monitoring and Up-To-Date Developments in PF, Including New Content PETER N.M

EDITION3RD BUILD A Covers OpenBSD 5.6, MORE SECURE FreeBSD 10.x, and NETWORK EDITION NETWORK 3RD NetBSD 6.x WITH PF THETHE BOOKBOOK THE BOOK OF PF OF THE BOOK THE BOOK OF PF OF THE BOOK OFOF PFPF OpenBSD’s stateful packet filter, PF, is the heart of • Build adaptive firewalls to proactively defend against A GUIDE TO THE the OpenBSD firewall. With more and more services attackers and spammers NO-NONSENSE placing high demands on bandwidth and an increas- OPENBSD FIREWALL • Harness OpenBSD’s latest traffic-shaping system ingly hostile Internet environment, no sysadmin can to keep your network responsive, and convert your afford to be without PF expertise. existing ALTQ configurations to the new system The third edition of The Book of PF covers the most • Stay in control of your traffic with monitoring and up-to-date developments in PF, including new content PETER N.M. HANSTEEN visualization tools (including NetFlow) on IPv6, dual stack configurations, the “queues and priorities” traffic-shaping system, NAT and redirection, The Book of PF is the essential guide to building a secure wireless networking, spam fighting, failover provision- network with PF. With a little effort and this book, you’ll ing, logging, and more. be well prepared to unlock PF’s full potential. You’ll also learn how to: ABOUT THE AUTHOR • Create rule sets for all kinds of network traffic, whether Peter N.M. Hansteen is a consultant, writer, and crossing a simple LAN, hiding behind NAT, traversing sysadmin based in Bergen, Norway. A longtime DMZs, or spanning bridges or wider networks Freenix advocate, Hansteen is a frequent lecturer on OpenBSD and FreeBSD topics, an occasional • Set up wireless networks with access points, and contributor to BSD Magazine, and the author of an lock them down using authpf and special access often-slashdotted blog (http://bsdly.blogspot.com/ ).