Bremner, Duncan James (2015) 25 Years of Network Access Technologies: from Voice to Internet; the Changing Face of Telecommunications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ON Semiconductor Is an Equal Opportunity/Affirmative Action Employer

ON Semiconductor Is Now To learn more about onsemi™, please visit our website at www.onsemi.com onsemi and and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba “onsemi” or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided “as-is” and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. “Typical” parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. -

Chapter 12 Three-Phase Controlled Rectifiers ∫

CHAPTER 12 THREE-PHASE CONTROLLED RECTIFIERS Author : Juan Dixon (Ph.D.) Department of Electrical Engineering Pontificia Universidad Católica de Chile Vicuña Mackenna 4860 Santiago, CHILE. 12.1 INTRODUCTION Three-phase controlled rectifiers have a wide range of applications, from small rectifiers to large High Voltage Direct Current (HVDC) transmission systems. They are used for electro-chemical process, many kinds of motor drives, traction equipment, controlled power supplies, and many other applications. From the point of view of the commutation process, they can be classified in two important categories: Line Commutated Controlled Rectifiers (Thyristor Rectifiers), and Force Commutated PWM Rectifiers. 12.2 LINE COMMUTATED CONTROLLED RECTIFIERS. 12.2.1 Three- phase hal - wavef rectifie r The figure 12.1 shows the three-phase half-wave rectifier topology. To control the load voltage, the half wave rectifier uses three, common-cathode thyristor arrangement. In this figure, the power supply, and the transformer are assumed ideal. The thyristor will conduct (ON state), when the anode-to-cathode voltage vAK is positive, and a firing current pulse iG is applied to the gate terminal. Delaying the firing pulse by an angle a does the control of the load voltage. The firing angle a is measured from the crossing point between the phase supply voltages, as shown in figure 12.2. At that point, the anode-to-cathode thyristor voltage vAK begins to be positive. The figure 12.3 shows that the possible range for gating delay is between a=0° and a=180°, but in real situations, because of commutation problems, the maximum firing angle is limited to around 160°. -

Sensors and Transducers

Sensors and Transducers Sensors and Transducers Third edition Ian R. Sinclair OXFORD AUCKLAND BOSTON JOHANNESBURG MELBOURNE NEW DELHI Newnes An imprint ofButterworth-Heinemann Linacre House, Jordan Hill, Oxford OX2 8DP 225 Wildwood Avenue, Woburn, MA 01801-2041 A division ofReed Educational a nd Professional Publishing Ltd A member ofthe Reed Elsevier plc group First published by BSP Professional Books 1988 Reprinted by Butterworth-Heinemann 1991 Second edition published by Butterworth-Heinemann 1992 Third edition 2001 # I. R. Sinclair 1988, 1992, 2001 All rights reserved. No part ofthis publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use ofthis publication) without the written permission ofthe copyright holder except in accordance with the provisions ofthe Copyright, Designs and Patents Act 1988 or under the terms ofa licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1P 9HE. Applications for the copyright holder's written permission to reproduce any part ofthis publication should be addressed to the publishers British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library ISBN0750649321 Typeset by David Gregson Associates, Beccles, Su¡olk Printed and bound in Great Britain Contents Preface to Third Edition vii Preface to First Edition ix Introduction xi 1 Strain and pressure 1 2 Position, direction, distance -

A Compendium of Electronic Organ Technology

A COMPENDIUM OF ELECTRONIC ORGAN TECHNOLOGY Volume 1: Analogue Organs by C E Pykett A COMPENDIUM OF ELECTRONIC ORGAN TECHNOLOGY Volume 1: Analogue Organs by C E Pykett PhD FInstP Considerable care has been exercised in the preparation of this volume. However the author cannot accept responsibility for any consequences howsoever they may arise. Readers are cautioned against attempting to construct or use electronic equipment which involves mains voltages unless they are fully conversant with the health and safety aspects involved. First edition October 2001 Version 1.5 (January 2003) ACKNOWLEDGMENT Thanks are due to Dr A D Ryder for permission to reproduce the circuit of his CFP oscillator which first appeared in the Electronic Organ Magazine COPYRIGHT This document may not be copied in whole or in part without permission from the author. © Copyright. C E Pykett 2003 ii CONTENTS Foreword v Chapter 1. Analogue Organs 1 Chapter 2. A Divider Organ - 5 Top Octave Generators for the Swell Department Chapter 3. Swell Keying Circuits 13 Chapter 4. Top Octave Generators and Keying for the 21 Great and Pedal Departments Chapter 5. Tone Forming Filters 25 Chapter 6. Output Channels, Amplifiers, Loudspeakers, 51 Phase Shifters and Swell Pedals Chapter 7. Key Contacts and Couplers 57 Chapter 8. Free Phase Organs 59 Chapter 9. Free Phase Oscillators 63 Chapter 10. Tone Forming for CFP Oscillators 71 Chapter 11. Free Phase Organ Miscellaneous Topics 73 Diagrams 75 Appendix 1. The reproduction of very low frequencies 109 Appendix 2. Phase shift vibrato and chorus 121 Appendix 3. A multichannel chorus processor 125 Appendix 4. -

Users Guide for the Non-Inverted LM3875 Kit Written by Brian Bell and Sandy H

Users Guide for the Non-Inverted LM3875 Kit Written by Brian Bell and Sandy H. 1 (26) Users Guide for the Non-Inverted LM3875 Kit (also known as the Gainclone kit) 1 INTRODUCTION.......................................................................................................................................... 2 1.1 HISTORY ................................................................................................................................................... 3 1.2 TERMINOLOGY USED IN THIS DOCUMENT................................................................................................. 4 2 BUILDING INSTRUCTIONS FOR THE KIT ........................................................................................... 5 2.1 PREMIUM KIT CONTENTS ......................................................................................................................... 5 2.2 BASIC KIT CONTENTS............................................................................................................................... 5 2.3 SOLDERING TIPS ....................................................................................................................................... 6 2.4 ASSEMBLING THE AMPLIFIER PCB........................................................................................................... 7 2.5 ASSEMBLING THE RECTIFIER PCB ......................................................................................................... 13 2.6 PICTURE OF FINISHED PCBS .................................................................................................................. -

Carbone Monoxide (CO) Detection Device Based on the Nickel Antimonate Oxide and a DC Electronic Circuit

applied sciences Article Carbone Monoxide (CO) Detection Device Based on the Nickel Antimonate Oxide and a DC Electronic Circuit José Trinidad Guillen Bonilla 1,2,* ,Héctor Guillén Bonilla 3, Verónica María Rodríguez Betancourtt 4, Antonio Casillas Zamora 3, Jorge Alberto Ramírez Ortega 3, Lorenzo Gildo Ortiz 5, María Eugenia Sánchez Morales 6 , Oscar Blanco Alonso 5 and Alex Guillén Bonilla 7,* 1 Departamento de Electrónica, Centro Universitario de Ciencias Exactas e Ingenierías (C.U.C.E.I.), Universidad de Guadalajara, Blvd. M. García Barragán 1421, Guadalajara 44410, Jalisco, Mexico 2 Departamento de Matemáticas, Centro Universitario de Ciencias Exactas e Ingenierías (C.U.C.E.I.), Universidad de Guadalajara, Blvd. M. García Barragán 1421, Guadalajara 44410, Jalisco, Mexico 3 Departamento de Ingeniería de Proyectos, Centro Universitario de Ciencias Exactas e Ingenierías (C.U.C.E.I.), Universidad de Guadalajara, Blvd. M. García Barragán 1421, Guadalajara 44410, Jalisco, Mexico 4 Departamento de Química, Centro Universitario de Ciencias Exactas e Ingenierías (C.U.C.E.I.), Universidad de Guadalajara, Blvd. M. García Barragán 1421, Guadalajara 44410, Jalisco, Mexico 5 Departamento de Física, Centro Universitario de Ciencias Exactas e Ingenierías (C.U.C.E.I.), Universidad de Guadalajara, Blvd. M. García Barragán 1421, Guadalajara 44410, Jalisco, Mexico 6 Departamento de Ciencias Tecnológicas, Centro Universitario de la Ciénega (CUCienéga), Universidad de Guadalajara, Av. Universidad No. 1115, LindaVista, Ocotlán C.P. 47810, Jalisco, Mexico 7 Departamento de Ciencias Computacionales e Ingenierías, Centro Universitario de los Valles (CUValles), Universidad de Guadalajara, Carretera Guadalajara-Ameca Km. 45.5, Ameca 46600, Jalisco, Mexico * Correspondence: [email protected] (J.T.G.B.); [email protected] (A.G.B.); Tel.: +52-(375)-7580-500 (ext. -

4 S1-Us A-Bo-Le Gist'y

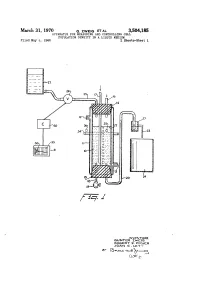

March 31, 1970 G. ZWEG ET All 3,504,185 APPARATUS FOR MEASURING AND CONTROLING CEL POPULATION DENSITY IN A LIQUID MEDIUM Filed May 9, 1968 2. Sheets-Sheet :9 O - 32. 33 : o SAHH 3. ?m WeavroAs, GUNT.R Z. We G ROBERT e. PP-ER JOAn . - 4 S1-us a-bo-le Gist'y. March 31, 1970 G. ZWEG ET All- 3,504,185 APPARATUS FOR MEASURING AND CONTROLLING CELL POPULATION DENSITY IN A LIQUID MEDIUM Filed May 9, 1968 2. Sheets-Sheet 2 N /Ayyam AOes. GUnTER ZWEG RO2ERT E. PPHER JOAN. E. HTT 3,504,185 United States Patent Office Patented Mar. 31, 1970 2 3,504,185 medium to dilute the cultured medium until the cultured APPARATUS FOR MEASURING AND CONTROL medium becomes less turbid again and the output of the LING CELL POPULATION DENSITY IN A LIQUID comparator is no longer energized so that the switch is MEDUM no longer operated and the valve is shut off. Gunter Zweig, Syracuse, Robert E. Pipher, Cortland, and A constant fluid level is maintained in the chamber Joan E. Hitt, Syracuse, N.Y., assignors to Syracuse Uni versity Research Corporation, Syracuse, N.Y., a corpo in which the cultured medium is contained and the over ration of New York flow resulting from dilution is collected for use. Usually Filed May 9, 1968, Ser. No. 727,910 continual agitation of the fluid in the chamber is required nt. C. G01n 21/26 to keep the cells in suspension in the medium and physical U.S. C. 250- 218 S Claims 10 conditions which are necessary for optimum growth speed are maintained in the usual manner. -

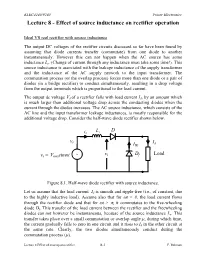

Lecture 8 - Effect of Source Inductance on Rectifier Operation

ELEC4240/9240 Power Electronics Lecture 8 - Effect of source inductance on rectifier operation Ideal VS real rectifier with source inductance The output DC voltages of the rectifier circuits discussed so far have been found by assuming that diode currents transfer (commutate) from one diode to another instantaneously. However this can not happen when the AC source has some inductance Ls. (Change of current through any inductance must take some time!). This source inductance is associated with the leakage inductance of the supply transformer and the inductance of the AC supply network to the input transformer. The commutation process (or the overlap process) forces more than one diode or a pair of diodes (in a bridge rectifier) to conduct simultaneously, resulting in a drop voltage from the output terminals which is proportional to the load current. The output dc voltage Vd of a rectifier falls with load current Id, by an amount which is much larger than additional voltage drop across the conducting diodes when the current through the diodes increases. The AC source inductance, which consists of the AC line and the input transformer leakage inductances, is mostly responsible for the additional voltage drop. Consider the half-wave diode rectifier shown below. D is Ls vs Id IDf D Load vs = Vmaxsinωt ∼ vi f Figure 8.1. Half-wave diode rectifier with source inductance. Let us assume that the load current Id is smooth and ripple-free (i.e., of constant, due to the highly inductive load). Assume also that for ωt > 0, the load current flows through the rectifier diode and that for ωt > π, it commutates to the free-wheeling diode Df. -

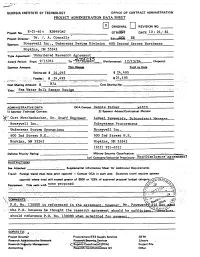

Project Administration Data Sheet

(7, ■■••••••"'". GEORGIA INSTITUTE OF TECHNOLOGY OFFICE OF CONTRACT ADMINISTRATION PROJECT ADMINISTRATION DATA SHEET ORIGINAL E REVISION NO. Project No. E-21-616 R58480A0 GTRIAW DATE 10/ 24/ 84 Project Director: Dr. J. A. Connelly SchooRgt EE Spimisort Honeywell Inc., Underseas System Division 600 Second Street Northeast Hopkins, MN 55343 Type Agreement: Unnumbered Research Agreement Award Period: From 9,'15/84 To (Performance) 12/15/84 (Reports) Sponsor Amount: This Change Total to Date Estima•:ed: $ 24,495 $ 24,495 Fundk: $ 24,495 $24,495 Cost Sharing Amount $ N/A Cost Sharing No: Title: Sea Water Bulk Sensor Design ADMINISTRATIVE DATA OCA Contact Dennis Farmer x41370 1) Sponsor Technical Contact: . 2) Sponsor Admin/Contractual Matters: X/ Curt Motchenbacher, Sr. Staff Engineer LaNeal Pewewardy, Subcontract Man ager Honeywell Inc._. Subsystems Procurement Underseas System Operations Honeywell Inc. 600 2nd Street 600 2nd Street N.E. Hopkins, MN 55343 Hopkins, MN 55343 (612) 931-6511 Defense Priority Rating: Military Security Classification: (or) Company/Industrial Proprietary: Non-;;.Di-scIosUreagre'emenil RESTRICTIONS See Attached Supplemental Information Sheet for Additional Requirements. Travel: Foreign travel must have prior approval — Contact OCA in each case. Domestic travel requires sponsor approval where tstal will exceed greater of $500 or 125% of approved proposal budget category none proposed Equipment: Title vests with 064 (.1 \ COMMENTS:. P.O. No. 130000 is referenced in the a Mr. Pewewar the P.O. because he thought the research agreement should be sufficient. should reference P.O. No. 130000 when submitted for payment. COPIES TO: - Project Director Procurement/E ES Supply Services GTRI Research Administrative Network Services Library . -

THD Mitigation in Line Currents of 6-Pulse Diode Bridge Rectifier Using the Delta-Wye Transformer As a Triplen Harmonic Filter A

16th NATIONAL POWER SYSTEMS CONFERENCE, 15th-17th DECEMBER, 2010 210 THD Mitigation in Line Currents of 6-Pulse Diode Bridge Rectifier Using the Delta-Wye Transformer as a Triplen Harmonic Filter A. N. Arvindan and B. Abinaya Dept. of Electrical & Electronics Engineering, SSN College of Engineering, Anna University (Chennai), India Abstract—The uncontrolled three-phase bridge rectifier has the least line current distortion among six-pulse rectifiers; however, its total harmonic distortion (THD) of 31.08% is unacceptable as per the contemporary power quality standards. This paper seeks to address the issue by elimination of triplen harmonics in the line currents by providing a delta- wye transformer at the ac interface i.e. between the three-phase supply and the diode bridge rectifier. The triplen harmonics circulate in the delta loop of the primary winding but are not manifested in the line currents thus reducing their THD values. The efficacy of the technique is proved by simulations considering the bridge rectifier with and without the delta-wye transformer of vector group Dy1. Experimental results with the Dy1 transformer and without it are presented. Keywords— diode bridge rectifier, improved power quality, total harmonic distortion, triplen harmonics. Fig. 1. An ac utility directly connected to a three-phase diode bridge rectifier feeding an inductive load. I. INTRODUCTION as stipulated by IEEE 519-1992. This paper investigates the HE three-phase diode bridge is, perhaps, the most effect of connecting the six-pulse diode bridge topology to T popular of the six-pulse rectifiers and is extensively the three-phase ac utility via a delta-wye (Δ-Y) transformer used, however, with the stringent contemporary power in terms of trapping the triplen harmonics in the delta loop, quality standards [1], [2] stipulating specific permissible thus eliminating them from the ac utility line currents and levels of total harmonic distortion (THD) at the ac utility also thereby improving the THD at the utility. -

3. Relays Contents

3. Relays Contents 1 Relay 1 1.1 Basic design and operation ...................................... 1 1.2 Types ................................................. 2 1.2.1 Latching relay ......................................... 2 1.2.2 Reed relay ........................................... 3 1.2.3 Mercury-wetted relay ..................................... 3 1.2.4 Mercury relay ......................................... 3 1.2.5 Polarized relay ........................................ 4 1.2.6 Machine tool relay ...................................... 4 1.2.7 Coaxial relay ......................................... 4 1.2.8 Time delay .......................................... 4 1.2.9 Contactor ........................................... 4 1.2.10 Solid-state relay ........................................ 4 1.2.11 Solid state contactor relay ................................... 5 1.2.12 Buchholz relay ........................................ 5 1.2.13 Forced-guided contacts relay ................................. 5 1.2.14 Overload protection relay ................................... 6 1.2.15 Vacuum relays ........................................ 6 1.3 Pole and throw ............................................. 6 1.4 Applications .............................................. 7 1.5 Relay application considerations .................................... 8 1.5.1 Derating factors ........................................ 9 1.5.2 Undesired arcing ....................................... 9 1.6 Protective relays ........................................... -

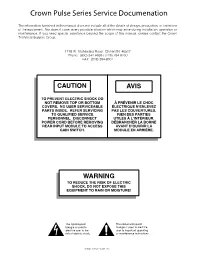

Pulse Service Documentation

Crown Pulse Series Service Documenation The information furnished in this manual does not include all of the details of design, production, or variations of the equipment. Nor does it cover every possible situation which may arise during installation, operation or maintenance. If you need special assistance beyond the scope of this manual, please contact the Crown Technical Support Group. 1718 W. Mishawaka Road Elkhart IN 46517 Phone: (800) 342-6939 / (219) 294-8200 FAX: (219) 294-8301 CAUTION AVIS TO PREVENT ELECTRIC SHOCK DO NOT REMOVE TOP OR BOTTOM À PRÉVENIR LE CHOC COVERS. NO USER SERVICEABLE ÉLECTRIQUE N’ENLEVEZ PARTS INSIDE. REFER SERVICING PAS LES COUVERTURES. TO QUALIFIED SERVICE RIEN DES PARTIES PERSONNEL. DISCONNECT UTILES À L’INTÉRIEUR. POWER CORD BEFORE REMOVING DÉBRANCHER LA BORNE REAR INPUT MODULE TO ACCESS AVANT D’OUVRIR LA GAIN SWITCH. MODULE EN ARRIÈRE. WARNING TO REDUCE THE RISK OF ELECTRIC SHOCK, DO NOT EXPOSE THIS EQUIPMENT TO RAIN OR MOISTURE! The lightning bolt The exclamation point triangle is used to triangle is used to alert the alert the user to the user to important operating risk of electric shock. or maintenance instructions. ©2005 Crown Audio, Inc. Cautions and Warnings Lightning Bolt Symbol: Exclamation Mark Symbol: This symbol is used to alert the user This symbol is used to alert the user to to the presence of dangerous make special note of important voltages and the possible risk of operating or maintenance instructions. electric shock. DANGER: The outputs of the amplifier can produce LETHAL energy levels! Be very careful when making connections. Do not attempt to change output wiring until the amplifier has been off at least 10 seconds.