Appendix a Data Transfer in Digital Aircraft Systems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Fly-By-Wire - Wikipedia, the Free Encyclopedia 11-8-20 下午5:33 Fly-By-Wire from Wikipedia, the Free Encyclopedia

Fly-by-wire - Wikipedia, the free encyclopedia 11-8-20 下午5:33 Fly-by-wire From Wikipedia, the free encyclopedia Fly-by-wire (FBW) is a system that replaces the Fly-by-wire conventional manual flight controls of an aircraft with an electronic interface. The movements of flight controls are converted to electronic signals transmitted by wires (hence the fly-by-wire term), and flight control computers determine how to move the actuators at each control surface to provide the ordered response. The fly-by-wire system also allows automatic signals sent by the aircraft's computers to perform functions without the pilot's input, as in systems that automatically help stabilize the aircraft.[1] Contents Green colored flight control wiring of a test aircraft 1 Development 1.1 Basic operation 1.1.1 Command 1.1.2 Automatic Stability Systems 1.2 Safety and redundancy 1.3 Weight saving 1.4 History 2 Analog systems 3 Digital systems 3.1 Applications 3.2 Legislation 3.3 Redundancy 3.4 Airbus/Boeing 4 Engine digital control 5 Further developments 5.1 Fly-by-optics 5.2 Power-by-wire 5.3 Fly-by-wireless 5.4 Intelligent Flight Control System 6 See also 7 References 8 External links Development http://en.wikipedia.org/wiki/Fly-by-wire Page 1 of 9 Fly-by-wire - Wikipedia, the free encyclopedia 11-8-20 下午5:33 Mechanical and hydro-mechanical flight control systems are relatively heavy and require careful routing of flight control cables through the aircraft by systems of pulleys, cranks, tension cables and hydraulic pipes. -

Teledyne Lecroy Product Line Card

Product Line Card OSCILLOSCOPES Learn More: teledynelecroy.com/oscilloscope LabMaster 10 Zi-A WaveMaster 8 Zi-B (SDA Models) (SDA/DDA 8 Zi-B) Bandwidth 20 GHz to 65 GHz 4 GHz to 30 GHz Resolution 8-bit resolution, 8-bit resolution, 11-bit with enhanced resolution 11-bit with enhanced resolution Rise Time 6.5 ps to 19.3 ps 15.5 ps to 95 ps Channels Up to 80, 4, (Analog+Digital+Sensor) 80 + 18 4 + 18 Display 15.3" WXGA Touch Screen 15.3" WXGA Touch Screen Standard Memory 32 Mpts/Ch 32 Mpts/Ch (64 Mpts/Ch) (64 Mpts/Ch) Maximum Memory† Up to 1024 Mpts Up to 512 Mpts Sample Rate Up to 160 GS/s Up to 80 GS/s MSO Characteristics† 3 GHz, 12.5 GS/s, 3 GHz, 12.5 GS/s, (Digital Channels) 18 Ch 18 Ch Trigger Types Edge, Width, Glitch, Pattern, Runt, Slew Rate, Edge, Width, Glitch, Pattern, Video, HDTV, Interval (Period), Dropout, Qualified, Cascade (Sequence) Trigger, Runt, Slew Rate, Interval (Period), Dropout, Qualified, Cascade High-speed Serial Trigger† (Sequence) Trigger, High-speed Serial Trigger† † Serial Data TD: 80-bit NRZ, 8b/10b, 64b/66b TD: 80-bit NRZ, 8b/10b, 64b/66b, RS-232, UART Trigger (T) D: 64b66b, 8b/10b, ARINC 429, Audio, TD or TDME: 100Base-T1, CAN, CAN FD, CAN FD Symbolic, Decode (D) CAN, CAN FD, CAN FD Symbolic, DigRF 3G, DigRF v4, I2C, LIN, MIL-STD-1553, SPI, Measure / Graph (M) ENET, ENET 10G, Fibre Channel, I2C, LIN, TD or TDxx: Audio (TDG), FlexRay (TDMP) Eye Diagram (E) Manchester, MDIO, MIL-STD-1553, NRZ, PCIe, RS-232. -

ICE PROTECTION Incomplete

ICE PROTECTION GENERAL The Ice and Rain Protection Systems allow the aircraft to operate in icing conditions or heavy rain. Aircraft Ice Protection is provided by heating in critical areas using either: Hot Air from the Pneumatic System o Wing Leading Edges o Stabilizer Leading Edges o Engine Air Inlets Electrical power o Windshields o Probe Heat . Pitot Tubes . Pitot Static Tube . AOA Sensors . TAT Probes o Static Ports . ADC . Pressurization o Service Nipples . Lavatory Water Drain . Potable Water Rain removal from the Windshields is provided by two fully independent Wiper Systems. LEADING EDGE THERMAL ANTI ICE SYSTEM Ice protection for the wing and horizontal stabilizer leading edges and the engine air inlet lips is ensured by heating these surfaces. Hot air supplied by the Pneumatic System is ducted through perforated tubes, called Piccolo tubes. Each Piccolo tube is routed along the surface, so that hot air jets flowing through the perforations heat the surface. Dedicated slots are provided for exhausting the hot air after the surface has been heated. Each subsystem has a pressure regulating/shutoff valve (PRSOV) type of Anti-icing valve. An airflow restrictor limits the airflow rate supplied by the Pneumatic System. The systems are regulated for proper pressure and airflow rate. Differential pressure switches and low pressure switches monitor for leakage and low pressures. Each Wing's Anti Ice System is supplied by its respective side of the Pneumatic System. The Stabilizer Anti Ice System is supplied by the LEFT side of the Pneumatic System. The APU cannot provide sufficient hot air for Pneumatic Anti Ice functions. -

Chapter 76 Engine Controls

ENGINE CONTROLS XL-2 AIRPLANE CHAPTER 76 ENGINE CONTROLS P/N 135A-970-100 Chapter 76 REVISION ~ Page 1 of 18 ENGINE CONTROLS XL-2 AIRPLANE Copyright © 2009 All rights reserved. The information contained herein is proprietary to Liberty Aerospace, Incorporated. It is prohibited to reproduce or transmit in any form or by any means, electronic or mechanical, including photocopying, recording, or use of any information storage and retrieval system, any portion of this document without express written permission of Liberty Aerospace Incorporated. Chapter 76 P/N 135A-970-100 Page 2 of 18 REVISION ~ ENGINE CONTROLS XL-2 AIRPLANE Table of Contents SECTION 76-00 GENERAL 5 SECTION 00-01 FADEC SYSTEM DESCRIPTION AND FUNCTIONAL OVERVIEW 6 SECTION 00-02 HEALTH STATUS ANNUNCIATOR AND POWER TRANSFER CHECK PROCEDURES 7 FADEC POWER TRANSFER CHECK 8 SECTION 76-10 POWER CONTROL 11 SECTION 10-01 POWER (THROTTLE) CABLE REMOVAL AND REPLACEMENT 12 THROTTLE CABLE REMOVAL 13 THROTTLE CABLE INSTALLATION 14 THROTTLE CABLE RIGGING PROCEDURE 15 SECTION 76-20 EMERGENCY SHUTDOWN 17 P/N 135A-970-100 Chapter 76 REVISION ~ Page 3 of 18 ENGINE CONTROLS XL-2 AIRPLANE PAGE LEFT INTENTIONALLY BLANK. Chapter 76 P/N 135A-970-100 Page 4 of 18 REVISION ~ ENGINE CONTROLS XL-2 AIRPLANE Section 76-00 General This chapter provides a descriptive overview of the control systems for the IOF- 240-B engine installed on the airplane. Detailed information for routine line maintenance for each engine subsection or system is provided in the appropriate chapter. More detailed information for repairs and maintenance on systems and components specific to the IOF-240B engine FADEC system are provided in the current release of the Teledyne Continental Motors Maintenance Manual for IOF- 240-B series engines, TCM p/n: M-22. -

ARINC Protocol Tutorial

ARINC Protocol Tutorial Copyrights ARINC Protocol Tutorial Manual Copyright 2000 Condor Engineering, Inc. This software product is copyrighted and all rights are reserved. The distribution and sale of this product are intended for the use of the original purchaser only per the terms of the License Agreement. This ARINC Protocol Tutorial Manual is copyrighted and all rights are reserved. This document may not, in whole or part, be; copied; photocopied; reproduced; translated; reduced or transferred to any electronic medium or machine-readable form without prior consent in writing from Condor Engineering, Inc. Microsoft is a registered trademark of Microsoft Corporation Windows is a registered trademark of Microsoft Corporation ARINC Protocol Tutorial (1600100-0027) Document Date: 07 June, 2000 Document Revision: 1.04 Condor Engineering, Inc. 101 W. Anapamu Street Santa Barbara, CA 93101 (805) 965-8000 (805) 963-9630 (fax) [email protected] (email) http:\www.condoreng.com Contents and Tables Contents Chapter 1 ARINC 429 Tutorial Introduction....................................................................................................1 About ARINC................................................................................................2 What is ARINC 429?...............................................................................2 ARINC 429 Usage ...................................................................................3 ARINC 429 Electrical Characteristics..........................................................3 -

Ensure Increased Reliability with ARINC 429 IP Core for FPGA

Ensure increased reliability with ARINC 429 IP Core for FPGA DO-254 compliant offering with multichannel ARINC 429 transmitter/receiver core Overview Cyient IP Core Features ARINC 429 specification defines the standard • Developed according to DO-254 (DAL-A) requirements for the transfer of engineering data guidelines between avionics systems on commercial aircraft • Two transmitters and eight receivers with supporting high speeds of up to 100 kHz as well loopback mode for self -testing as speeds as low as 12.5 kHz. The ARINC protocol • Portable to Microsemi, Intel/Altera, Lattice, or supports more than 46 meters. Xilinx FPGA families The Cyient ARINC 429 IP Core is developed for • Supports standard line drivers and receivers FPGA with multiple transmitters and receivers and • Parity checking for Tx and Rx is compliant with Design Assurance Level (DAL) • Programmable labels (up to eight different labels) A requirements. It receives data from an external • Programmable label filtering and SDI check microcontroller through SPI lines and transmits • SPI interface to the microcontroller 32-bit data word (encoded serial data) through the ARINC line driver. ARINC429 IP Core receives • Programmable data rates for each channel: 12.5 serial data from the ARINC line receiver and or 100 kbps transmits 32-bit decoded data word to an external • Detection of parity, label, SDI, and data errors microcontroller. Fig. 1 | ARINC 429 Board FPGA RX FIFO RxHi 8 Arinc ARINC RX RxLow Line Receivers Parity Check SDI & Label Check SPI TX FIFO Micro Controller Micro TxHi 2 Arinc ARINC TX Tx Low Line Control and Status Registers and Status Control Drivers Parity Gen Error Injection Fig. -

Arinc 429 Converter Logic & Interface

NEXSYS® Component Technology ARINC 429 CONVERTER LOGIC & INTERFACE The ARINC 429 Converter component is an 8-pin logic and interface device developed (IN 1) (GND) (RXA) (FAIL) as a part of our NEXSYS® Component Technology. This single-bit, single-label ARINC 429 Converter can replace the need for a dedicated ARINC converter box. The ARINC 429 (RXB) (IN 2) (28 V) (OUT) Converter can be configured inside a VIVISUN® High Capacity switch body or inside a stand- alone NEXSYS Module for use behind the panel. The ARINC 429 Converter can be combined SR429/1M with electromechanical switches and other NEXSYS components to create a custom configuration that uniquely addresses the designer’s specific functional requirements. The ARINC 429 Converter is designed and tested in accordance with MIL-PRF-22885 and DO-160. SR429/1M • Industry first innovation - ARINC 429 converter inside VIVISUN annunciator, switch or NEXSYS Module • Simple unit with no software, firmware or programmable logic • No external decoder box required to achieve annunciation based on data bit • Accommodates two additional discrete inputs to provide “fail” monitoring • Includes watchdog timer with selectable buffer times to monitor validity of incoming ARINC data stream • Ideally suited for ADS-B out pilot interface requirements • Included in MIL-PRF-22885/108 VIVISUN® High Capacity Body as shown contains ARINC 429 Converter, single switch pole and 4-pin NEXSYS component NEXSYS® Module as shown contains ARINC 429 Converter Data Sheet: DS-4291M-17 www.appliedavionics.com OVERVIEW ARINC 429 CONVERTER ARINC 429 Converter (SR429/1M) Figure 1: Block Diagram The ARINC 429 Converter (SR429/1M) component can be configured inside a VIVISUN® annunciator, switch or NEXSYS® Module. -

The Market for Aviation APU Engines

The Market for Aviation APU Engines Product Code #F644 A Special Focused Market Segment Analysis by: Aviation Gas Turbine Forecast Analysis 2 The Market for Aviation APU Engines 2011 - 2020 Table of Contents Executive Summary .................................................................................................................................................2 Introduction................................................................................................................................................................2 Methodology ..............................................................................................................................................................2 Trends..........................................................................................................................................................................3 The Competitive Environment...............................................................................................................................3 Market Statistics .......................................................................................................................................................3 Table 1 - The Market for Aviation APU Engines Unit Production by Headquarters/Company/Program 2011 - 2020 ..................................................5 Table 2 - The Market for Aviation APU Engines Value Statistics by Headquarters/Company/Program 2011 - 2020.................................................10 Figure 1 - The Market -

Fly-By-Wire: Getting Started on the Right Foot and Staying There…

Fly-by-Wire: Getting started on the right foot and staying there… Imagine yourself getting into the cockpit of an aircraft, finishing your preflight checks, and taxiing out to the runway ready for takeoff. You begin the takeoff roll and start to rotate. As you lift off, you discover your side stick controller is not responding correctly to your commands. Panic sets in, and you feel that you’ve lost total control of the aircraft. Thanks to quick action from your second in command, he takes over and stabilizes the aircraft so that you both can plan to return to the airport under reversionary mode. This situation could have been a catastrophe. This happened in August of 2001. A Lufthansa Airbus A320 came within less than two feet and a few seconds of crashing during takeoff on a planned flight from Frankfurt to Paris. Preliminary reports indicated that maintenance was performed on the captain’s sidestick controller immediately before the incident. This had inadvertently created a situation in which control inputs were reversed. The case reveals that at least two "filters," or safety defenses, were breached, leading to a near-crash shortly after rotation at Frankfurt’s Runway 18. Quick action by the first officer prevented a catastrophe. Lufthansa Technik personnel found a damaged pin on one segment of the four connector segments (with 140 pins on each) at the "rack side," as it were, of the avionics mount. This incident prompted an article to be published in the 2003 November-December issue of the Flight Safety Mechanics Bulletin. The report detailed all that transpired during the maintenance and subsequent release of the aircraft. -

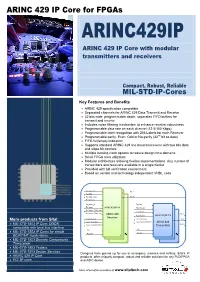

MIL-STD-1553 IP Core

ARINC 429 IP Core for FPGAs ARINC429IP ARINC 429 IP Core with modular transmitters and receivers Compact, Robust, Reliable MIL-STD-IP-Cores Key Features and Benefits ARINC 429 specification compatible Separated channels for ARINC 429 Data Transmit and Receive 32 bits wide, programmable depth, separated FIFO buffers for transmit and receive Includes noise filtering mechanism to enhance receiver robustness Programmable data rate on each channel (12.5/100 Kbps) Programmable label recognition with 256 Labels for each Receiver Programmable parity: Even, Odd or No-parity (32nd bit as data) FIFO full/empty indication Supports standard ARINC 429 line drivers/receivers with two bits data and slope bit controls Multiple running clock options to reduce design time domains Small FPGA area utilization Modular architecture allowing flexible implementations. Any number of transmitters and receivers available in a single Netlist. Provided with full verification environment Based on vendor and technology independent VHDL code Rx_Data_rd RX_P Rx_Data Rx_Data_valid RX_N Rx_Control Rx_Label_w Tx_Data e Rx_Label ARINC429IP-RX Tx_Data_we Rx_Labels_Table_rdy ARINC429IP-R Tx_Control Rx_Labels_Table_rst ARINC 429 TX_P Tx_FIFO_Full ARINC429IP-TX ReceiverARINC 429 More products from Sital: Rx_FIFO_Full Receiver Tx_FIFO_Empty TX_N Rx_FIFO_Empty Tx_FIFO_NumOfWords ARINCA 429 MIL-STD-1553 IP Core, DDC® Slope Rx_FIFO_NumOfWords Transmitter compatible with local bus interface Clk MIL-STD-1553 IP Cores for simple Clk ResetN ResetN BC/RT/MT Applications. 1 1 2 2 MIL-STD-1553 Discrete Components n m Transceiver MIL-STD-1553 Testers. MIL-STD-1553 Design Services Designed from ground up for use in aerospace, avionics and military, Sital's IP ARINC 429 IP Core products, offer uniquely compact, robust and reliable solutions for any PLD/FPGA PCI IP core and ASIC device. -

C-130J Super Hercules Whatever the Situation, We'll Be There

C-130J Super Hercules Whatever the Situation, We’ll Be There Table of Contents Introduction INTRODUCTION 1 Note: In general this document and its contents refer RECENT CAPABILITY/PERFORMANCE UPGRADES 4 to the C-130J-30, the stretched/advanced version of the Hercules. SURVIVABILITY OPTIONS 5 GENERAL ARRANGEMENT 6 GENERAL CHARACTERISTICS 7 TECHNOLOGY IMPROVEMENTS 8 COMPETITIVE COMPARISON 9 CARGO COMPARTMENT 10 CROSS SECTIONS 11 CARGO ARRANGEMENT 12 CAPACITY AND LOADS 13 ENHANCED CARGO HANDLING SYSTEM 15 COMBAT TROOP SEATING 17 Paratroop Seating 18 Litters 19 GROUND SERVICING POINTS 20 GROUND OPERATIONS 21 The C-130 Hercules is the standard against which FLIGHT STATION LAYOUTS 22 military transport aircraft are measured. Versatility, Instrument Panel 22 reliability, and ruggedness make it the military Overhead Panel 23 transport of choice for more than 60 nations on six Center Console 24 continents. More than 2,300 of these aircraft have USAF AVIONICS CONFIGURATION 25 been delivered by Lockheed Martin Aeronautics MAJOR SYSTEMS 26 Company since it entered production in 1956. Electrical 26 During the past five decades, Lockheed Martin and its subcontractors have upgraded virtually every Environmental Control System 27 system, component, and structural part of the Fuel System 27 aircraft to make it more durable, easier to maintain, Hydraulic Systems 28 and less expensive to operate. In addition to the Enhanced Cargo Handling System 29 tactical airlift mission, versions of the C-130 serve Defensive Systems 29 as aerial tanker and ground refuelers, weather PERFORMANCE 30 reconnaissance, command and control, gunships, Maximum Effort Takeoff Roll 30 firefighters, electronic recon, search and rescue, Normal Takeoff Distance (Over 50 Feet) 30 and flying hospitals. -

ARINC Protocol Summary

ARINC Protocol Summary Part Number: 10011-00000-A1 Cage Code: 4RK27 ● NAICS: 334119 Alta Data Technologies LLC 4901 Rockaway Blvd, Building A Rio Rancho, NM 87124 USA (tel) 505-994-3111 ● www.altadt.com i CUSTOMER NOTES: Document Information: Rev A1 – Release Date: 7 April 2010 Note to the Reader and End-User: This document is provided for information only and is copyrighted by Alta Data Technologies. While Alta strives to provide the most accurate information, there may be errors and omissions in this document. Alta disclaims all liability in document errors and any product usage. By using an Alta product, the customer or end user agrees (1) to accept Alta’s Standard Terms and Conditions of Sale, Standard Warranty and Software License and (2) to not hold Alta Members, Employees, Contractors or Sales & Support Representatives responsible for any loss or legal liability, tangible or intangible, from any document errors or any product usage. The product described in this document is not US ITAR controlled. Use of Alta products or documentation in violation of local usage, waste discard and export control rules, or in violation of US ITAR regulations, voids product warranty and shall not be supported. This document may be distributed to support government programs and projects. Third party person, company or consultant distribution is not allowed without Alta’s written permission. AltaCore, AltaCore-1553, AltaCore-ARINC, AltaAPI, AltaView and AltaRTVal are Trademarks of Alta Data Technologies LLC, Rio Rancho, New Mexico USA Contact: We welcome comments and suggestions. Please contact us at 888-429-1553 (toll free in US) or 505- 994-3111 or visit our web site for support submit forms at www.altadt.com or email us at [email protected] or [email protected].