Vhdl Implementation and Verification of Arinc-429 Core

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Teledyne Lecroy Product Line Card

Product Line Card OSCILLOSCOPES Learn More: teledynelecroy.com/oscilloscope LabMaster 10 Zi-A WaveMaster 8 Zi-B (SDA Models) (SDA/DDA 8 Zi-B) Bandwidth 20 GHz to 65 GHz 4 GHz to 30 GHz Resolution 8-bit resolution, 8-bit resolution, 11-bit with enhanced resolution 11-bit with enhanced resolution Rise Time 6.5 ps to 19.3 ps 15.5 ps to 95 ps Channels Up to 80, 4, (Analog+Digital+Sensor) 80 + 18 4 + 18 Display 15.3" WXGA Touch Screen 15.3" WXGA Touch Screen Standard Memory 32 Mpts/Ch 32 Mpts/Ch (64 Mpts/Ch) (64 Mpts/Ch) Maximum Memory† Up to 1024 Mpts Up to 512 Mpts Sample Rate Up to 160 GS/s Up to 80 GS/s MSO Characteristics† 3 GHz, 12.5 GS/s, 3 GHz, 12.5 GS/s, (Digital Channels) 18 Ch 18 Ch Trigger Types Edge, Width, Glitch, Pattern, Runt, Slew Rate, Edge, Width, Glitch, Pattern, Video, HDTV, Interval (Period), Dropout, Qualified, Cascade (Sequence) Trigger, Runt, Slew Rate, Interval (Period), Dropout, Qualified, Cascade High-speed Serial Trigger† (Sequence) Trigger, High-speed Serial Trigger† † Serial Data TD: 80-bit NRZ, 8b/10b, 64b/66b TD: 80-bit NRZ, 8b/10b, 64b/66b, RS-232, UART Trigger (T) D: 64b66b, 8b/10b, ARINC 429, Audio, TD or TDME: 100Base-T1, CAN, CAN FD, CAN FD Symbolic, Decode (D) CAN, CAN FD, CAN FD Symbolic, DigRF 3G, DigRF v4, I2C, LIN, MIL-STD-1553, SPI, Measure / Graph (M) ENET, ENET 10G, Fibre Channel, I2C, LIN, TD or TDxx: Audio (TDG), FlexRay (TDMP) Eye Diagram (E) Manchester, MDIO, MIL-STD-1553, NRZ, PCIe, RS-232. -

ARINC Protocol Tutorial

ARINC Protocol Tutorial Copyrights ARINC Protocol Tutorial Manual Copyright 2000 Condor Engineering, Inc. This software product is copyrighted and all rights are reserved. The distribution and sale of this product are intended for the use of the original purchaser only per the terms of the License Agreement. This ARINC Protocol Tutorial Manual is copyrighted and all rights are reserved. This document may not, in whole or part, be; copied; photocopied; reproduced; translated; reduced or transferred to any electronic medium or machine-readable form without prior consent in writing from Condor Engineering, Inc. Microsoft is a registered trademark of Microsoft Corporation Windows is a registered trademark of Microsoft Corporation ARINC Protocol Tutorial (1600100-0027) Document Date: 07 June, 2000 Document Revision: 1.04 Condor Engineering, Inc. 101 W. Anapamu Street Santa Barbara, CA 93101 (805) 965-8000 (805) 963-9630 (fax) [email protected] (email) http:\www.condoreng.com Contents and Tables Contents Chapter 1 ARINC 429 Tutorial Introduction....................................................................................................1 About ARINC................................................................................................2 What is ARINC 429?...............................................................................2 ARINC 429 Usage ...................................................................................3 ARINC 429 Electrical Characteristics..........................................................3 -

Ensure Increased Reliability with ARINC 429 IP Core for FPGA

Ensure increased reliability with ARINC 429 IP Core for FPGA DO-254 compliant offering with multichannel ARINC 429 transmitter/receiver core Overview Cyient IP Core Features ARINC 429 specification defines the standard • Developed according to DO-254 (DAL-A) requirements for the transfer of engineering data guidelines between avionics systems on commercial aircraft • Two transmitters and eight receivers with supporting high speeds of up to 100 kHz as well loopback mode for self -testing as speeds as low as 12.5 kHz. The ARINC protocol • Portable to Microsemi, Intel/Altera, Lattice, or supports more than 46 meters. Xilinx FPGA families The Cyient ARINC 429 IP Core is developed for • Supports standard line drivers and receivers FPGA with multiple transmitters and receivers and • Parity checking for Tx and Rx is compliant with Design Assurance Level (DAL) • Programmable labels (up to eight different labels) A requirements. It receives data from an external • Programmable label filtering and SDI check microcontroller through SPI lines and transmits • SPI interface to the microcontroller 32-bit data word (encoded serial data) through the ARINC line driver. ARINC429 IP Core receives • Programmable data rates for each channel: 12.5 serial data from the ARINC line receiver and or 100 kbps transmits 32-bit decoded data word to an external • Detection of parity, label, SDI, and data errors microcontroller. Fig. 1 | ARINC 429 Board FPGA RX FIFO RxHi 8 Arinc ARINC RX RxLow Line Receivers Parity Check SDI & Label Check SPI TX FIFO Micro Controller Micro TxHi 2 Arinc ARINC TX Tx Low Line Control and Status Registers and Status Control Drivers Parity Gen Error Injection Fig. -

Arinc 429 Converter Logic & Interface

NEXSYS® Component Technology ARINC 429 CONVERTER LOGIC & INTERFACE The ARINC 429 Converter component is an 8-pin logic and interface device developed (IN 1) (GND) (RXA) (FAIL) as a part of our NEXSYS® Component Technology. This single-bit, single-label ARINC 429 Converter can replace the need for a dedicated ARINC converter box. The ARINC 429 (RXB) (IN 2) (28 V) (OUT) Converter can be configured inside a VIVISUN® High Capacity switch body or inside a stand- alone NEXSYS Module for use behind the panel. The ARINC 429 Converter can be combined SR429/1M with electromechanical switches and other NEXSYS components to create a custom configuration that uniquely addresses the designer’s specific functional requirements. The ARINC 429 Converter is designed and tested in accordance with MIL-PRF-22885 and DO-160. SR429/1M • Industry first innovation - ARINC 429 converter inside VIVISUN annunciator, switch or NEXSYS Module • Simple unit with no software, firmware or programmable logic • No external decoder box required to achieve annunciation based on data bit • Accommodates two additional discrete inputs to provide “fail” monitoring • Includes watchdog timer with selectable buffer times to monitor validity of incoming ARINC data stream • Ideally suited for ADS-B out pilot interface requirements • Included in MIL-PRF-22885/108 VIVISUN® High Capacity Body as shown contains ARINC 429 Converter, single switch pole and 4-pin NEXSYS component NEXSYS® Module as shown contains ARINC 429 Converter Data Sheet: DS-4291M-17 www.appliedavionics.com OVERVIEW ARINC 429 CONVERTER ARINC 429 Converter (SR429/1M) Figure 1: Block Diagram The ARINC 429 Converter (SR429/1M) component can be configured inside a VIVISUN® annunciator, switch or NEXSYS® Module. -

MIL-STD-1553 IP Core

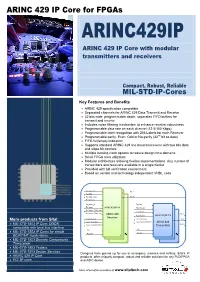

ARINC 429 IP Core for FPGAs ARINC429IP ARINC 429 IP Core with modular transmitters and receivers Compact, Robust, Reliable MIL-STD-IP-Cores Key Features and Benefits ARINC 429 specification compatible Separated channels for ARINC 429 Data Transmit and Receive 32 bits wide, programmable depth, separated FIFO buffers for transmit and receive Includes noise filtering mechanism to enhance receiver robustness Programmable data rate on each channel (12.5/100 Kbps) Programmable label recognition with 256 Labels for each Receiver Programmable parity: Even, Odd or No-parity (32nd bit as data) FIFO full/empty indication Supports standard ARINC 429 line drivers/receivers with two bits data and slope bit controls Multiple running clock options to reduce design time domains Small FPGA area utilization Modular architecture allowing flexible implementations. Any number of transmitters and receivers available in a single Netlist. Provided with full verification environment Based on vendor and technology independent VHDL code Rx_Data_rd RX_P Rx_Data Rx_Data_valid RX_N Rx_Control Rx_Label_w Tx_Data e Rx_Label ARINC429IP-RX Tx_Data_we Rx_Labels_Table_rdy ARINC429IP-R Tx_Control Rx_Labels_Table_rst ARINC 429 TX_P Tx_FIFO_Full ARINC429IP-TX ReceiverARINC 429 More products from Sital: Rx_FIFO_Full Receiver Tx_FIFO_Empty TX_N Rx_FIFO_Empty Tx_FIFO_NumOfWords ARINCA 429 MIL-STD-1553 IP Core, DDC® Slope Rx_FIFO_NumOfWords Transmitter compatible with local bus interface Clk MIL-STD-1553 IP Cores for simple Clk ResetN ResetN BC/RT/MT Applications. 1 1 2 2 MIL-STD-1553 Discrete Components n m Transceiver MIL-STD-1553 Testers. MIL-STD-1553 Design Services Designed from ground up for use in aerospace, avionics and military, Sital's IP ARINC 429 IP Core products, offer uniquely compact, robust and reliable solutions for any PLD/FPGA PCI IP core and ASIC device. -

ARINC Protocol Summary

ARINC Protocol Summary Part Number: 10011-00000-A1 Cage Code: 4RK27 ● NAICS: 334119 Alta Data Technologies LLC 4901 Rockaway Blvd, Building A Rio Rancho, NM 87124 USA (tel) 505-994-3111 ● www.altadt.com i CUSTOMER NOTES: Document Information: Rev A1 – Release Date: 7 April 2010 Note to the Reader and End-User: This document is provided for information only and is copyrighted by Alta Data Technologies. While Alta strives to provide the most accurate information, there may be errors and omissions in this document. Alta disclaims all liability in document errors and any product usage. By using an Alta product, the customer or end user agrees (1) to accept Alta’s Standard Terms and Conditions of Sale, Standard Warranty and Software License and (2) to not hold Alta Members, Employees, Contractors or Sales & Support Representatives responsible for any loss or legal liability, tangible or intangible, from any document errors or any product usage. The product described in this document is not US ITAR controlled. Use of Alta products or documentation in violation of local usage, waste discard and export control rules, or in violation of US ITAR regulations, voids product warranty and shall not be supported. This document may be distributed to support government programs and projects. Third party person, company or consultant distribution is not allowed without Alta’s written permission. AltaCore, AltaCore-1553, AltaCore-ARINC, AltaAPI, AltaView and AltaRTVal are Trademarks of Alta Data Technologies LLC, Rio Rancho, New Mexico USA Contact: We welcome comments and suggestions. Please contact us at 888-429-1553 (toll free in US) or 505- 994-3111 or visit our web site for support submit forms at www.altadt.com or email us at [email protected] or [email protected]. -

DESIGN SPECIFICATION MODEL, CDI-500, P/N 50-0010-XX COURSE DEVIATION INDICATOR Document # 97040005 SKYLIGHT AVIONICS 38629 6Th S

DESIGN SPECIFICATION MODEL, CDI-500, P/N 50-0010-XX COURSE DEVIATION INDICATOR Document # 97040005 SKYLIGHT AVIONICS 38629 6th ST. EAST PALMDALE, CA 93550 (661) 265-0497 SKYLIGHT AVIONICS DESIGN SPECIFICATION MODEL CDI-500, P/N 50-0010-XX DOC # 97040005, REV: New, Date 03/20/02 Index Section Title Page (i) Operating Instructions 1 (ii) Equipment Limitations 2 (iii) Installation Procedures 3 (iv) Install Specification: Physical 4 (v) Install Specification: Electrical 4 (vi) Specifications 5,6,7 (vii) System Equipment - Major Components 8 (viii) Environmental Qualification Form 9, 10 Illustrations Section Title Page (i-1) Operation P/N 50-0010-XX 1 (iv-1) Mechanical Installation Drawing 4 (v-1) Electrical Installation Drawing 4 (vii-1) Interconnect Block Diagram 8 Page i SKYLIGHT AVIONICS DESIGN SPECIFICATION MODEL CDI-500, P/N 50-0010-XX DOC # 97040005, REV: New, Date 03/20/02 (i) Operating Instructions 1. General The CDI-500 indicator only displays information received from the Flight Management System and has no control over it. The indicator has no "OFF/ON" switch and becomes operational upon application of Aircraft Avionics Bus Power. 2. Warning Flags 1. Alphanumeric Display reads “ FLAG “ HSI status input is missing or invalid. 2. GPS warn lit, GPS status is missing or invalid. 3. Navigation Mode A B CDI C E BRG115 2 5 1 DIS D O N FMS GPSTRM APR TEST FR SX MSG WPT DIM F G H I JK L M P/N 50-0010-(XX), Illustration (i-1) Course Deviation Bar Graph and Numeric Display A. On Course / Center Line (Green LED, OFF Course Intensity Decreases). -

G5 Electronic Flight Instrument Pilot's Guide for Certified Aircraft Blank Page SYSTEM OVERVIEW

G5 Electronic Flight Instrument Pilot's Guide for Certified Aircraft Blank Page SYSTEM OVERVIEW FLIGHT INSTRUMENTS AFCS ADDITIONAL FEATURES INDEX Blank Page © 2017 Garmin Ltd. or its subsidiaries. All rights reserved. This manual reflects the operation of System Software version 5.00 or later. Some differences in operation may be observed when comparing the information in this manual to earlier or later software versions. Garmin International, Inc., 1200 East 151st Street, Olathe, Kansas 66062, U.S.A. Garmin AT, Inc.,2345 Turner Road SE, Salem, OR 97302, U.S.A. Garmin (Europe) Ltd., Liberty House, Hounsdown Business Park, Southampton, Hampshire SO40 9LR U.K. Garmin Corporation, No. 68, Zhangshu 2nd Road, Xizhi District, New Taipei City, Taiwan Web Site Address: www.garmin.com Except as expressly provided herein, no part of this manual may be reproduced, copied, transmitted, disseminated, downloaded or stored in any storage medium, for any purpose without the express written permission of Garmin. Garmin hereby grants permission to download a single copy of this manual and of any revision to this manual onto a hard drive or other electronic storage medium to be viewed for personal use, provided that such electronic or printed copy of this manual or revision must contain the complete text of this copyright notice and provided further that any unauthorized commercial distribution of this manual or any revision hereto is strictly prohibited. Garmin® is a registered trademark of Garmin Ltd. or its subsidiaries. This trademark may not be used without the express permission of Garmin. December, 2017 190-01112-12 Rev. A Printed in the U.S.A. -

VPX339 Data Sheet

VPX 339 Multi-Channel, Multi-Protocol Key Features Avionics, MIL-STD- • Comprehensive multi-protocol support • 1553/ARINC429/RINC717, Support for MIL-STD-1553A/B, MIL-STD-1760 • Support for ARINC 429, ARINC 575, ARINC 717, ARINC 825 • IRIG-B and IRIG-106 Chapter 10 MIL-STD-1553 MT • Full line rate on all channels simultaneously • Up to 8 programmable RS-232/422/485 channels • Up to 10 Avionics/Digital discrete I/O • 48-bit/100 ns Time Stamp • Option for I/O to the P2 or the Front • Health Management through dedicated Processor Benefits • Advanced MIL-STD-1553 technology from DDC coupled to VadaTech OpenVPX expertise VPX339 • DMA engine reduces CPU load • Flexible implementation of numerous avionic standard protocols • Full system supply from industry leader • AS9100 and ISO9001 certified company 1 VPX339 – Multi-Channel, Multi-Protocol Avionics, MIL-STD-1553/ARINC429/ARINC717, 3U VPX [email protected] | www.vadatech.com VPX339 The VPX339 is based on the Data Device Corporation (DDC), BU-67118 multi- channel, multi-protocol avionics product. It utilizes the world’s most advanced MIL-STD-1553 technology. The module is low power, high MTBF, and high performance. Option to route the I/O to the front or the P2 connector. The module can output MIL-STD-1553A/B, IRIG106, ARINC 429, CAN bus/ARINC 825 channels, discrete I/O, ARINC-717, etc. The module has an onboard DMA engine for low CPU utilization. IRIG-106 Chapter 10, Tx inhibit, and ARINC 717 which are ideal for flight data recorders. The module is ideal for applications such as mission-computers, displays and LRUs, digital data recorders, radar systems/situational awareness, commercial aerospace, flyable avionics/UAVs, data loading and data monitors. -

Partner Directory Wind River Partner Program

PARTNER DIRECTORY WIND RIVER PARTNER PROGRAM The Internet of Things (IoT), cloud computing, and Network Functions Virtualization are but some of the market forces at play today. These forces impact Wind River® customers in markets ranging from aerospace and defense to consumer, networking to automotive, and industrial to medical. The Wind River® edge-to-cloud portfolio of products is ideally suited to address the emerging needs of IoT, from the secure and managed intelligent devices at the edge to the gateway, into the critical network infrastructure, and up into the cloud. Wind River offers cross-architecture support. We are proud to partner with leading companies across various industries to help our mutual customers ease integration challenges; shorten development times; and provide greater functionality to their devices, systems, and networks for building IoT. With more than 200 members and still growing, Wind River has one of the embedded software industry’s largest ecosystems to complement its comprehensive portfolio. Please use this guide as a resource to identify companies that can help with your development across markets. For updates, browse our online Partner Directory. 2 | Partner Program Guide MARKET FOCUS For an alphabetical listing of all members of the *Clavister ..................................................37 Wind River Partner Program, please see the Cloudera ...................................................37 Partner Index on page 139. *Dell ..........................................................45 *EnterpriseWeb -

SN3500 Installation Manual Page Ii

SN3500 Primary Navigation Display with Reversionary Attitude Mode And LNAV Roll Steering Installation Manual Sandel Avionics, Inc. 2401 Dogwood Way Vista, CA 92081 Phone (760) 727- 4900 FAX (760) 727- 4899 Website: www.sandel.com Email: [email protected] 82005-IM-T [This page intentionally left blank] 82005-IM-T Sandel SN3500 Installation Manual Page ii Table of Contents 1 General Information ....................................................................................................... 1-1 1.1 Introduction .................................................................................................................................................. 1-1 1.1.1 EXPORT CONTROL NOTICE ............................................................................................................. 1-1 1.2 Equipment Description ............................................................................................................................... 1-1 1.2.1 Features ................................................................................................................................................. 1-1 1.3 Installation Planning ................................................................................................................................... 1-2 1.3.1 Installation Planning Cycle .................................................................................................................... 1-2 1.3.2 Post Installation Summary .................................................................................................................... -

Rugged MIL-STD-1553 and ARINC 429 Boards and Solutions Article

COTS Rugged modules and boards for MIL-STD-1553 and ARINC 429 standards By George Los, Data Device Corporation This article describes the MIL-STD-1553 and ARINC 429 standards and their differences in detail, and introduces a wide range of components, test boards, rugged embedded boards, rugged small form factor boards and software corresponding to these standards. Figure 1. Various DDC MIL- STD-1553 and ARINC 429 boards n MIL-STD-1553 is a protocol standard that ARINC 429 has been thought to be the lower- and can add MIL-STD-1553 or ARINC 429 defines the electrical and functional character - cost, lower-reliability alternative for 1553 for for those applications requiring it is becoming istics of a serial data bus that has been mainly commercial aircraft. However the lower speed, very popular. This is a common approach used in military aircraft. The bus architecture lack of redundancy, and inferior lightning pro - with standard PMC or PC/104-Plus type form of MIL-STD-1553 allows for reduced size and tection in the bus adds cost to system architects factor boards. The PC/104-Plus form factor is weight of systems and the wiring that inter - who must find ways to meet high-level safety- a small and compact design that is well suited connects them, is inherently reliable, and in - critical standards. Conversely, 1553 inherent for small embedded applications and rapid corporates redundancies that make it a safe reliability, robustness, maturity, and superior prototyping in the lab. The card is only 3.575 data bus solution. Since 1978 it has served as EMI performance, combined with recent com - inches x 3.775 inches (90mm x 96mm) and the primary command and control intercon - petitive prices, has allowed 1553 to be used on uses a stacking concept where one card sits on nect in military aircraft.