DATA NETWORK EVALUATION CRITERIA REPORT July 2009 6

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Last Time Today Response Time Vs. RM Computing Response Time More Second-Priority Task I Response Time

Last Time Today Priority-based scheduling Response time analysis Static priorities Blocking terms Dynamic priorities Priority inversion Schedulable utilization And solutions Rate monotonic rule: Keep utilization below 69% Release jitter Other extensions Response Time vs. RM Computing Response Time Rate monotonic result WC response time of highest priority task R Tells us that a broad class of embedded systems meet their 1 time constraints: R1 = C 1 • Scheduled using fixed priorities with RM or DM priority Hopefully obvious assignment • Total utilization not above 69% WC response time of second-priority task R 2 However, doesn’t give very good feedback about what is Case 1: R 2 ≤ T1 going on with a specific system • R2 = C 2 + C 1 Response time analysis R T T Tells us for each task, what is the longest time between R1 2 1 2 when it is released and when it finishes Then these can be compared with deadlines 1 1 Gives insight into how close the system is to meeting / not 2 meeting its deadline Is more precise (rejects fewer systems) More Second-Priority Task i Response Time Case 2: T 1 < R 2 ≤ 2T 1 General case: R = C + 2C Ri 2 2 1 Ri = Ci + ∑ Cj j ∀j∈hp (i) T R1 T1 R2 2T 1 T2 1 1 1 hp(i) is the set of tasks with priority higher than I 2 2 Only higher-priority tasks can delay a task Case 3: 2T 1 < R 2 ≤ 3T 1 Problem with using this equation in practice? R2 = C 2 + 3C 1 General case of the second-priority task: R2 = C 2 + ceiling ( R 2 / T 1 ) C 1 1 Computing Response Times Response Time Example Rewrite -

Preemption-Based Avoidance of Priority Inversion for Java

Preemption-Based Avoidance of Priority Inversion for Java Adam Welc Antony L. Hosking Suresh Jagannathan [email protected] [email protected] [email protected] Department of Computer Sciences Purdue University West Lafayette, IN 47906 Abstract their actions via mutual exclusion locks. The resulting programming model is reasonably simple, Priority inversion occurs in concurrent programs when but unfortunately unwieldy for large-scale applications. A low-priority threads hold shared resources needed by some significant problem with using low-level, lock-based syn- high-priority thread, causing them to block indefinitely. chronization primitives is priority inversion. We propose a Shared resources are usually guarded by low-level syn- new solution for priority inversion that exploits close coop- chronization primitives such as mutual-exclusion locks, eration between the compiler and the run-time system. Our semaphores, or monitors. There are two existing solu- approach is applicable to any language that offers the fol- tions to priority inversion. The first, establishing high- lowing mechanisms: level scheduling invariants over synchronization primitives to eliminate priority inversion a priori, is difficult in practice • Multithreading: concurrent threads of control execut- and undecidable in general. Alternatively, run-time avoid- ing over objects in a shared address space. ance mechanisms such as priority inheritance still force • Synchronized sections: lexically-delimited blocks high-priority threads to wait until desired resources are re- of code, guarded by dynamically-scoped monitors. leased. Threads synchronize on a given monitor, acquiring it We describe a novel compiler and run-time solution to on entry to the block and releasing it on exit. -

Teledyne Lecroy Product Line Card

Product Line Card OSCILLOSCOPES Learn More: teledynelecroy.com/oscilloscope LabMaster 10 Zi-A WaveMaster 8 Zi-B (SDA Models) (SDA/DDA 8 Zi-B) Bandwidth 20 GHz to 65 GHz 4 GHz to 30 GHz Resolution 8-bit resolution, 8-bit resolution, 11-bit with enhanced resolution 11-bit with enhanced resolution Rise Time 6.5 ps to 19.3 ps 15.5 ps to 95 ps Channels Up to 80, 4, (Analog+Digital+Sensor) 80 + 18 4 + 18 Display 15.3" WXGA Touch Screen 15.3" WXGA Touch Screen Standard Memory 32 Mpts/Ch 32 Mpts/Ch (64 Mpts/Ch) (64 Mpts/Ch) Maximum Memory† Up to 1024 Mpts Up to 512 Mpts Sample Rate Up to 160 GS/s Up to 80 GS/s MSO Characteristics† 3 GHz, 12.5 GS/s, 3 GHz, 12.5 GS/s, (Digital Channels) 18 Ch 18 Ch Trigger Types Edge, Width, Glitch, Pattern, Runt, Slew Rate, Edge, Width, Glitch, Pattern, Video, HDTV, Interval (Period), Dropout, Qualified, Cascade (Sequence) Trigger, Runt, Slew Rate, Interval (Period), Dropout, Qualified, Cascade High-speed Serial Trigger† (Sequence) Trigger, High-speed Serial Trigger† † Serial Data TD: 80-bit NRZ, 8b/10b, 64b/66b TD: 80-bit NRZ, 8b/10b, 64b/66b, RS-232, UART Trigger (T) D: 64b66b, 8b/10b, ARINC 429, Audio, TD or TDME: 100Base-T1, CAN, CAN FD, CAN FD Symbolic, Decode (D) CAN, CAN FD, CAN FD Symbolic, DigRF 3G, DigRF v4, I2C, LIN, MIL-STD-1553, SPI, Measure / Graph (M) ENET, ENET 10G, Fibre Channel, I2C, LIN, TD or TDxx: Audio (TDG), FlexRay (TDMP) Eye Diagram (E) Manchester, MDIO, MIL-STD-1553, NRZ, PCIe, RS-232. -

Real-Time Operating Systems (RTOS)

Real-Time Operating Systems (RTOS) 101 Real-Time System Characteristics RTOS Architecture Rate Monotonic • A real-time system is a computer system which is required by its specification to adhere to: Scheduling (RMS) – functional requirements (behavior) • A priority is assigned based on the inverse of its pe- – temporal requirements (timing constraints, deadlines) riod • Specific deterministic timing (temporal ) requirements – Shorter execution periods = higher priority – “Deterministic" timing means that RTOS services consume only – Longer execution periods = lower priority known and expected amounts of time. • Common way to assign fixed priorities • Small size (footprint) – If there is a fixed-priority schedule that meets all dead- lines, then RMS will produce a feasible schedule Types of Real-Time Systems • Simple to understand and implement • A generic real-time system requires that results be produced RTOS Task Services • P1 is assigned a higher priority than P2. within a specified deadline period. • An embedded system is a computing device that is part of a • Scheduling and Dispatching larger system. • Inter-task Communication • A safety-critical system is a real-time system with catastro- phic results in case of failure. • Memory System Management • A hard real-time system guarantees that real-time tasks be Earliest Deadline First (EDF) • Input / Output System Management completed within their required deadlines. Failure to meet a single deadline may lead to a critical catastrophic system • Scheduling Time Management & Timers failure such as physical damage or loss of life. • Priorities are assigned according to deadlines: • Error Management • A firm real-time system tolerates a low occurrence of missing – the earlier the deadline, the higher the priority a deadline. -

ARINC Protocol Tutorial

ARINC Protocol Tutorial Copyrights ARINC Protocol Tutorial Manual Copyright 2000 Condor Engineering, Inc. This software product is copyrighted and all rights are reserved. The distribution and sale of this product are intended for the use of the original purchaser only per the terms of the License Agreement. This ARINC Protocol Tutorial Manual is copyrighted and all rights are reserved. This document may not, in whole or part, be; copied; photocopied; reproduced; translated; reduced or transferred to any electronic medium or machine-readable form without prior consent in writing from Condor Engineering, Inc. Microsoft is a registered trademark of Microsoft Corporation Windows is a registered trademark of Microsoft Corporation ARINC Protocol Tutorial (1600100-0027) Document Date: 07 June, 2000 Document Revision: 1.04 Condor Engineering, Inc. 101 W. Anapamu Street Santa Barbara, CA 93101 (805) 965-8000 (805) 963-9630 (fax) [email protected] (email) http:\www.condoreng.com Contents and Tables Contents Chapter 1 ARINC 429 Tutorial Introduction....................................................................................................1 About ARINC................................................................................................2 What is ARINC 429?...............................................................................2 ARINC 429 Usage ...................................................................................3 ARINC 429 Electrical Characteristics..........................................................3 -

Ensure Increased Reliability with ARINC 429 IP Core for FPGA

Ensure increased reliability with ARINC 429 IP Core for FPGA DO-254 compliant offering with multichannel ARINC 429 transmitter/receiver core Overview Cyient IP Core Features ARINC 429 specification defines the standard • Developed according to DO-254 (DAL-A) requirements for the transfer of engineering data guidelines between avionics systems on commercial aircraft • Two transmitters and eight receivers with supporting high speeds of up to 100 kHz as well loopback mode for self -testing as speeds as low as 12.5 kHz. The ARINC protocol • Portable to Microsemi, Intel/Altera, Lattice, or supports more than 46 meters. Xilinx FPGA families The Cyient ARINC 429 IP Core is developed for • Supports standard line drivers and receivers FPGA with multiple transmitters and receivers and • Parity checking for Tx and Rx is compliant with Design Assurance Level (DAL) • Programmable labels (up to eight different labels) A requirements. It receives data from an external • Programmable label filtering and SDI check microcontroller through SPI lines and transmits • SPI interface to the microcontroller 32-bit data word (encoded serial data) through the ARINC line driver. ARINC429 IP Core receives • Programmable data rates for each channel: 12.5 serial data from the ARINC line receiver and or 100 kbps transmits 32-bit decoded data word to an external • Detection of parity, label, SDI, and data errors microcontroller. Fig. 1 | ARINC 429 Board FPGA RX FIFO RxHi 8 Arinc ARINC RX RxLow Line Receivers Parity Check SDI & Label Check SPI TX FIFO Micro Controller Micro TxHi 2 Arinc ARINC TX Tx Low Line Control and Status Registers and Status Control Drivers Parity Gen Error Injection Fig. -

Real-Time Operating System (RTOS)

Real-Time Operating System ELC 4438 – Spring 2016 Liang Dong Baylor University RTOS – Basic Kernel Services Task Management • Scheduling is the method by which threads, processes or data flows are given access to system resources (e.g. processor time, communication bandwidth). • The need for a scheduling algorithm arises from the requirement for most modern systems to perform multitasking (executing more than one process at a time) and multiplexing (transmit multiple data streams simultaneously across a single physical channel). Task Management • Polled loops; Synchronized polled loops • Cyclic Executives (round-robin) • State-driven and co-routines • Interrupt-driven systems – Interrupt service routines – Context switching void main(void) { init(); Interrupt-driven while(true); } Systems void int1(void) { save(context); task1(); restore(context); } void int2(void) { save(context); task2(); restore(context); } Task scheduling • Most RTOSs do their scheduling of tasks using a scheme called "priority-based preemptive scheduling." • Each task in a software application must be assigned a priority, with higher priority values representing the need for quicker responsiveness. • Very quick responsiveness is made possible by the "preemptive" nature of the task scheduling. "Preemptive" means that the scheduler is allowed to stop any task at any point in its execution, if it determines that another task needs to run immediately. Hybrid Systems • A hybrid system is a combination of round- robin and preemptive-priority systems. – Tasks of higher priority can preempt those of lower priority. – If two or more tasks of the same priority are ready to run simultaneously, they run in round-robin fashion. Thread Scheduling ThreadPriority.Highest ThreadPriority.AboveNormal A B ThreadPriority.Normal C ThreadPriority.BelowNormal D E F ThreadPriority.Lowest Default priority is Normal. -

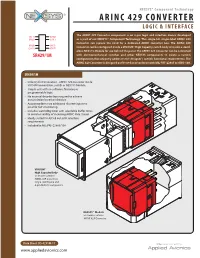

Arinc 429 Converter Logic & Interface

NEXSYS® Component Technology ARINC 429 CONVERTER LOGIC & INTERFACE The ARINC 429 Converter component is an 8-pin logic and interface device developed (IN 1) (GND) (RXA) (FAIL) as a part of our NEXSYS® Component Technology. This single-bit, single-label ARINC 429 Converter can replace the need for a dedicated ARINC converter box. The ARINC 429 (RXB) (IN 2) (28 V) (OUT) Converter can be configured inside a VIVISUN® High Capacity switch body or inside a stand- alone NEXSYS Module for use behind the panel. The ARINC 429 Converter can be combined SR429/1M with electromechanical switches and other NEXSYS components to create a custom configuration that uniquely addresses the designer’s specific functional requirements. The ARINC 429 Converter is designed and tested in accordance with MIL-PRF-22885 and DO-160. SR429/1M • Industry first innovation - ARINC 429 converter inside VIVISUN annunciator, switch or NEXSYS Module • Simple unit with no software, firmware or programmable logic • No external decoder box required to achieve annunciation based on data bit • Accommodates two additional discrete inputs to provide “fail” monitoring • Includes watchdog timer with selectable buffer times to monitor validity of incoming ARINC data stream • Ideally suited for ADS-B out pilot interface requirements • Included in MIL-PRF-22885/108 VIVISUN® High Capacity Body as shown contains ARINC 429 Converter, single switch pole and 4-pin NEXSYS component NEXSYS® Module as shown contains ARINC 429 Converter Data Sheet: DS-4291M-17 www.appliedavionics.com OVERVIEW ARINC 429 CONVERTER ARINC 429 Converter (SR429/1M) Figure 1: Block Diagram The ARINC 429 Converter (SR429/1M) component can be configured inside a VIVISUN® annunciator, switch or NEXSYS® Module. -

Guaranteeing Real-Time Performance Using Rate Monotonic Analysis

Carnegie Mellon University Software Engineering Institute Guaranteeing Real-Time Performance Using Rate Monotonic Analysis Embedded Systems Conference September 20-23, 1994 Presented by Ray Obenza Software Engineering Institute Carnegie Mellon University Pittsburgh PA 15213 Sponsored by the U.S. Department of Defense Carnegie Mellon University Software Engineering Institute Rate Monotonic Analysis Introduction Periodic tasks Extending basic theory Synchronization and priority inversion Aperiodic servers Case study: BSY-1 Trainer 1 Introduction Carnegie Mellon University Software Engineering Institute Purpose of Tutorial Introduce rate monotonic analysis Explain how to perform the analysis Give some examples of usage Convince you it is useful 2 Introduction Carnegie Mellon University Software Engineering Institute Tutorial Format Lecture Group exercises Case study Questions welcome anytime 3 Introduction Carnegie Mellon University Software Engineering Institute RMARTS Project Originally called Real-Time Scheduling in Ada Project (RTSIA). • focused on rate monotonic scheduling theory • recognized strength of theory was in analysis Rate Monotonic Analysis for Real-Time Systems (RMARTS) • focused on analysis supported by (RMS) theory • analysis of designs regardless of language or scheduling approach used Project focused initially on uniprocessor systems. Work continues in distributed processing systems. 4 Introduction Carnegie Mellon University Software Engineering Institute Real-Time Systems Timing requirements • meeting deadlines Periodic -

RTOS Northern Real Time Applications (NRTA)

By N.J. Keeling, Director of Marketing, RTOS Northern Real Time Applications (NRTA). Missed it! - How Priority Inversion messes up real-time performance and how the Priority Ceiling Protocol puts it right. In hard real-time systems it is important that everything runs on-time, every time. To do this efficiently it is necessary to make sure urgent things are done before less urgent things. When code is developed using a real-time operating system (RTOS) that offers pre-emptive scheduling, each task can be allocat- ed a level of priority. The best way to set the priority of each task is according to the urgency of the task: the most urgent task gets the highest priority (this ordering scheme is known as Deadline Monotonic). PRE-EMPTIVE MULTI-TASKING there is a requirement for data to be shared between ulti-tasking through use of an RTOS sched- the various tasks in the application. Clearly this is a typ- uler enables the processor to be shared ical situation: imagine an I/O data stream that is imple- M between a number of tasks in an applica- mented with two tasks. The first (called H) is a high pri- tion. In most priority schemes the scheduler is pre- ority task and drives communications hardware. It emptive: a task of a higher priority will 'break in' on the takes data from a buffer and places it onto a network. execution of lower priority tasks and take over the The task needs to run and finish by a short deadline, processor until it finishes or is pre-empted in its turn by which is why it has a high priority. -

Multitasking and Real-Time Scheduling

Multitasking and Real-time Scheduling EE8205: Embedded Computer Systems http://www.ee.ryerson.ca/~courses/ee8205/ Dr. Gul N. Khan http://www.ee.ryerson.ca/~gnkhan Electrical and Computer Engineering Ryerson University Overview • RTX - Preemptive Scheduling • Real-time Scheduling Techniques . Fixed-Priority and Earliest Deadline First Scheduling • Utilization and Response-time Analysis • Priority Inversion • Sporadic and Aperiodic Process Scheduling Chapter 6 of the Text by Wolf, Chapter 13 of Text by Burns and Wellings and Keil-RTX documents © G. Khan Embedded Computer Systems–EE8205: Real-time Scheduling Page: 1 Priority-driven Scheduling Rules: • each process has a fixed priority (1 lowest); • highest-priority ready process gets CPU; • process continues until done. Processes • P1: priority 3, execution time 10 • P2: priority 2, execution time 30 • P3: priority 1, execution time 20 P3 ready t=18 P2 ready t=0 P1 ready t=15 P2 P1 P2 P3 time 0 10 20 30 40 50 60 © G. Khan Embedded Computer Systems–EE8205: Real-time Scheduling Page: 2 RTX Scheduling Options RTX allows us to build an application with three different kernel- scheduling options: • Pre-Emptive scheduling Each task has a different priority and will run until it is pre- empted or has reached a blocking OS call. • Round-Robin scheduling Each task has the same priority and will run for a fixed period, or time slice, or until has reached a blocking OS call. • Co-operative multi-tasking Each task has the same priority and the Round-Robin is disabled. Each task will run until it reached a blocking OS call or uses the os_tsk_pass() call. -

Lock-Free Programming

Lock-Free Programming Geoff Langdale L31_Lockfree 1 Desynchronization ● This is an interesting topic ● This will (may?) become even more relevant with near ubiquitous multi-processing ● Still: please don’t rewrite any Project 3s! L31_Lockfree 2 Synchronization ● We received notification via the web form that one group has passed the P3/P4 test suite. Congratulations! ● We will be releasing a version of the fork-wait bomb which doesn't make as many assumptions about task id's. – Please look for it today and let us know right away if it causes any trouble for you. ● Personal and group disk quotas have been grown in order to reduce the number of people running out over the weekend – if you try hard enough you'll still be able to do it. L31_Lockfree 3 Outline ● Problems with locking ● Definition of Lock-free programming ● Examples of Lock-free programming ● Linux OS uses of Lock-free data structures ● Miscellanea (higher-level constructs, ‘wait-freedom’) ● Conclusion L31_Lockfree 4 Problems with Locking ● This list is more or less contentious, not equally relevant to all locking situations: – Deadlock – Priority Inversion – Convoying – “Async-signal-safety” – Kill-tolerant availability – Pre-emption tolerance – Overall performance L31_Lockfree 5 Problems with Locking 2 ● Deadlock – Processes that cannot proceed because they are waiting for resources that are held by processes that are waiting for… ● Priority inversion – Low-priority processes hold a lock required by a higher- priority process – Priority inheritance a possible solution L31_Lockfree