Pulse Processing: Pulse Shaping

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Timing of Load Switches

Application Report SLVA883–April 2017 Timing of Load Switches Nicholas Carley........................................................................................................... Power Switches ABSTRACT Timing of load switches can vary depending on the operating conditions of the system and feature set of the device. At a glance, these variations can seem complex; but, when broken down, each operating condition and feature has a correlation to a change in timing. This application note goes into detail on how each condition or feature can alter the timing of a load switch so that the variations can be prepared for. Contents 1 Overview and Main Questions ............................................................................................. 2 1.1 Definition of Timing Parameters .................................................................................. 2 1.2 Alternative Timing Methods ....................................................................................... 2 1.3 Why is My Rise Time Different than Expected? ................................................................ 3 1.4 Why is My Fall Time Different than Expected? ................................................................. 3 1.5 Why Do NMOS and PMOS Pass FETs Affect Timing Differently?........................................... 3 2 Effect of System Operating Specifications on Timing................................................................... 5 2.1 Temperature........................................................................................................ -

Electrical Circuits Lab. 0903219 Series RC Circuit Phasor Diagram

Electrical Circuits Lab. 0903219 Series RC Circuit Phasor Diagram - Simple steps to draw phasor diagram of a series RC circuit without memorizing: * Start with the quantity (voltage or current) that is common for the resistor R and the capacitor C, which is here the source current I (because it passes through both R and C without being divided). Figure (1) Series RC circuit * Now we know that I and resistor voltage VR are in phase or have the same phase angle (there zero crossings are the same on the time axis) and VR is greater than I in magnitude. * Since I equal the capacitor current IC and we know that IC leads the capacitor voltage VC by 90 degrees, we will add VC on the phasor diagram as follows: * Now, the source voltage VS equals the vector summation of VR and VC: Figure (2) Series RC circuit Phasor Diagram Prepared by: Eng. Wiam Anabousi - Important notes on the phasor diagram of series RC circuit shown in figure (2): A- All the vectors are rotating in the same angular speed ω. B- This circuit acts as a capacitive circuit and I leads VS by a phase shift of Ө (which is the current angle if the source voltage is the reference signal). Ө ranges from 0o to 90o (0o < Ө <90o). If Ө=0o then this circuit becomes a resistive circuit and if Ө=90o then the circuit becomes a pure capacitive circuit. C- The phase shift between the source voltage and its current Ө is important and you have two ways to find its value: a- b- = - = - D- Using the phasor diagram, you can find all needed quantities in the circuit like all the voltages magnitude and phase and all the currents magnitude and phase. -

System Step and Impulse Response Lab 04 Bruce A

ROSE-HULMAN INSTITUTE OF TECHNOLOGY Department of Electrical and Computer Engineering ECE 300 Signals and Systems Spring 2009 System Step and Impulse Response Lab 04 Bruce A. Ferguson, Bob Throne In this laboratory, you will investigate basic system behavior by determining the step and impulse response of a simple RC circuit. You will also determine the time constant of the circuit and determine its rise time, two common figures of merit (FOMs) for circuit building blocks. Objectives 1. Design an experiment by specifying a test setup, choosing circuit component values, and specifying test waveform details to investigate the step and impulse response. 2. Measure the step response of the circuit and determine the rise time, validating your theoretical calculations. 3. Measure the impulse response of the circuit and determine the time constant, validating your theoretical calculations. Prelab Find and bring a circuit board to the lab so you can build the RC circuit. Background As we introduce the study of systems, it will be good to keep the discussion well grounded in the circuit theory you have spent so much of your energy learning. An important problem in modern high speed digital and wideband analog systems is the response limitations of basic circuit elements in high speed integrated circuits. As simple as it may seem, the lowly RC lowpass filter accurately models many of the systems for which speed problems are so severe. There is a basic need to be able to characterize a circuit independent of its circuit design and layout in order to predict its behavior. Consider the now-overly-familiar RC lowpass filter shown in Figure 1. -

Phasor Analysis of Circuits

Phasor Analysis of Circuits Concepts Frequency-domain analysis of a circuit is useful in understanding how a single-frequency wave undergoes an amplitude change and phase shift upon passage through the circuit. The concept of impedance or reactance is central to frequency-domain analysis. For a resistor, the impedance is Z ω = R , a real quantity independent of frequency. For capacitors and R ( ) inductors, the impedances are Z ω = − i ωC and Z ω = iω L. In the complex plane C ( ) L ( ) these impedances are represented as the phasors shown below. Im ivL R Re -i/vC These phasors are useful because the voltage across each circuit element is related to the current through the equation V = I Z . For a series circuit where the same current flows through each element, the voltages across each element are proportional to the impedance across that element. Phasor Analysis of the RC Circuit R V V in Z in Vout R C V ZC out The behavior of this RC circuit can be analyzed by treating it as the voltage divider shown at right. The output voltage is then V Z −i ωC out = C = . V Z Z i C R in C + R − ω + The amplitude is then V −i 1 1 out = = = , V −i +ω RC 1+ iω ω 2 in c 1+ ω ω ( c ) 1 where we have defined the corner, or 3dB, frequency as 1 ω = . c RC The phasor picture is useful to determine the phase shift and also to verify low and high frequency behavior. The input voltage is across both the resistor and the capacitor, so it is equal to the vector sum of the resistor and capacitor voltages, while the output voltage is only the voltage across capacitor. -

Chapter 4 HW Solution

ME 380 Chapter 4 HW February 27, 2012 Chapter 4 HW Solution Review Questions. 1. Name the performance specification for first order systems. Time constant τ. 2. What does the performance specification for a first order system tell us? How fast the system responds. 5. The imaginary part of a pole generates what part of the response? The un-decaying sinusoidal part. 6. The real part of a pole generates what part of the response? The decay envelope. 8. If a pole is moved with a constant imaginary part, what will the responses have in common? Oscillation frequency. 9. If a pole is moved with a constant real part, what will the responses have in common? Decay envelope. 10. If a pole is moved along a radial line extending from the origin, what will the responses have in common? Damping ratio (and % overshoot). 13. What pole locations characterize (1) the underdamped system, (2) the overdamped system, and (3) the critically damped system? 1. Complex conjugate pole locations. 2. Real (and separate) pole locations. 3. Real identical pole locations. 14. Name two conditions under which the response generated by a pole can be neglected. 1. The pole is \far" to the left in the s-plane compared with the other poles. 2. There is a zero very near to the pole. Problems. Problem 2(a). This is a 1st order system with a time constant of 1/5 second (or 0.2 second). It also has a DC gain of 1 (just let s = 0 in the transfer function). The input shown is a unit step; if we let the transfer function be called G(s), the output is input × transfer function. -

Effect of Source Inductance on MOSFET Rise and Fall Times

Effect of Source Inductance on MOSFET Rise and Fall Times Alan Elbanhawy Power industry consultant, email: [email protected] Abstract The need for advanced MOSFETs for DC-DC converters applications is growing as is the push for applications miniaturization going hand in hand with increased power consumption. These advanced new designs should theoretically translate into doubling the average switching frequency of the commercially available MOSFETs while maintaining the same high or even higher efficiency. MOSFETs packaged in SO8, DPAK, D2PAK and IPAK have source inductance between 1.5 nH to 7 nH (nanoHenry) depending on the specific package, in addition to between 5 and 10 nH of printed circuit board (PCB) trace inductance. In a synchronous buck converter, laboratory tests and simulation show that during the turn on and off of the high side MOSFET the source inductance will develop a negative voltage across it, forcing the MOSFET to continue to conduct even after the gate has been fully switched off. In this paper we will show that this has the following effects: • The drain current rise and fall times are proportional to the total source inductance (package lead + PCB trace) • The rise and fall times arealso proportional to the magnitude of the drain current, making the switching losses nonlinearly proportional to the drain current and not linearly proportional as has been the common wisdom • It follows from the above two points that the current switch on/off is predominantly controlled by the traditional package's parasitic -

5 RC Circuits

Physics 212 Lab Lab 5 RC Circuits What You Need To Know: The Physics In the previous two labs you’ve dealt strictly with resistors. In today’s lab you’ll be using a new circuit element called a capacitor. A capacitor consists of two small metal plates that are separated by a small distance. This is evident in a capacitor’s circuit diagram symbol, see Figure 1. When a capacitor is hooked up to a circuit, charges will accumulate on the plates. Positive charge will accumulate on one plate and negative will accumulate on the other. The amount of charge that can accumulate is partially dependent upon the capacitor’s capacitance, C. With a charge distribution like this (i.e. plates of charge), a uniform electric field will be created between the plates. [You may remember this situation from the Equipotential Surfaces lab. In the lab, you had set-ups for two point-charges and two lines of charge. The latter set-up represents a capacitor.] A main function of a capacitor is to store energy. It stores its energy in the electric field between the plates. Battery Capacitor (with R charges shown) C FIGURE 1 - Battery/Capacitor FIGURE 2 - RC Circuit If you hook up a battery to a capacitor, like in Figure 1, positive charge will accumulate on the side that matches to the positive side of the battery and vice versa. When the capacitor is fully charged, the voltage across the capacitor will be equal to the voltage across the battery. You know this to be true because Kirchhoff’s Loop Law must always be true. -

ELECTRICAL CIRCUIT ANALYSIS Lecture Notes

ELECTRICAL CIRCUIT ANALYSIS Lecture Notes (2020-21) Prepared By S.RAKESH Assistant Professor, Department of EEE Department of Electrical & Electronics Engineering Malla Reddy College of Engineering & Technology Maisammaguda, Dhullapally, Secunderabad-500100 B.Tech (EEE) R-18 MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY II Year B.Tech EEE-I Sem L T/P/D C 3 -/-/- 3 (R18A0206) ELECTRICAL CIRCUIT ANALYSIS COURSE OBJECTIVES: This course introduces the analysis of transients in electrical systems, to understand three phase circuits, to evaluate network parameters of given electrical network, to draw the locus diagrams and to know about the networkfunctions To prepare the students to have a basic knowledge in the analysis of ElectricNetworks UNIT-I D.C TRANSIENT ANALYSIS: Transient response of R-L, R-C, R-L-C circuits (Series and parallel combinations) for D.C. excitations, Initial conditions, Solution using differential equation and Laplace transform method. UNIT - II A.C TRANSIENT ANALYSIS: Transient response of R-L, R-C, R-L-C Series circuits for sinusoidal excitations, Initial conditions, Solution using differential equation and Laplace transform method. UNIT - III THREE PHASE CIRCUITS: Phase sequence, Star and delta connection, Relation between line and phase voltages and currents in balanced systems, Analysis of balanced and Unbalanced three phase circuits UNIT – IV LOCUS DIAGRAMS & RESONANCE: Series and Parallel combination of R-L, R-C and R-L-C circuits with variation of various parameters.Resonance for series and parallel circuits, concept of band width and Q factor. UNIT - V NETWORK PARAMETERS:Two port network parameters – Z,Y, ABCD and hybrid parameters.Condition for reciprocity and symmetry.Conversion of one parameter to other, Interconnection of Two port networks in series, parallel and cascaded configuration and image parameters. -

(ECE, NDSU) Lab 11 – Experiment Multi-Stage RC Low Pass Filters

ECE-311 (ECE, NDSU) Lab 11 – Experiment Multi-stage RC low pass filters 1. Objective In this lab you will use the single-stage RC circuit filter to build a 3-stage RC low pass filter. The objective of this lab is to show that: As more stages are added, the filter becomes able to better reject high frequency noise When plotted on a Bode plot, the gain approaches two asymptotes: the low frequency gain approaches a constant gain of 0dB while the high-frequency gain drops as 20N dB/decade where N is the number of stages. 2. Background The single stage RC filter is a low pass filter: low frequencies are passed (have a gain of one), while high frequencies are rejected (the gain goes to zero). This is a useful filter to remove noise from a signal. Many types of signals are predominantly low-frequency in nature - meaning they change slowly. This includes measurements of temperature, pressure, volume, position, speed, etc. Noise, however, tends to be at all frequencies, and is seen as the “fuzzy” line on you oscilloscope when you amplify the signal. The trick when designing a low-pass filter is to select the RC time constant so that the gain is one over the frequency range of your signal (so it is passed unchanged) but zero outside this range (to reject the noise). 3. Theoretical response One problem with adding stages to an RC filter is that each new stage loads the previous stage. This loading consumes or “bleeds” some current from the previous stage capacitor, changing the behavior of the previous stage circuit. -

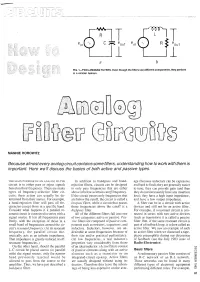

How to Design Analog Filter Circuits.Pdf

a b FIG. 1-TWO LOWPASS FILTERS. Even though the filters use different components, they perform in a similiar fashion. MANNlE HOROWITZ Because almost every analog circuit contains some filters, understandinghow to work with them is important. Here we'll discuss the basics of both active and passive types. THE MAIN PURPOSE OF AN ANALOG FILTER In addition to bandpass and band- age (because inductors can be expensive circuit is to either pass or reject signals rejection filters, circuits can be designed and hard to find); they are generally easier based on their frequency. There are many to only pass frequencies that are either to tune; they can provide gain (and thus types of frequency-selective filter cir- above or below a certain cutoff frequency. they do not necessarily have any insertion cuits; their action can usually be de- If the circuit passes only frequencies that loss); they have a high input impedance, termined from their names. For example, are below the cutoff, the circuit is called a and have a low output impedance. a band-rejection filter will pass all fre- lo~~passfilter, while a circuit that passes A filter can be in a circuit with active quencies except those in a specific band. those frequencies above the cutoff is a devices and still not be an active filter. Consider what happens if a parallel re- higlzpass filter. For example, if a resonant circuit is con- sonant circuit is connected in series with a All of the different filters fall into one . nected in series with two active devices signal source. -

Integer-And Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations

applied sciences Article Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations Roman Sotner 1,* , Ondrej Domansky 1, Jan Jerabek 1 , Norbert Herencsar 1 , Jiri Petrzela 1 and Darius Andriukaitis 2 1 SIX Research Center, Faculty of Electrical Engineering and Communication, Brno University of Technology, Technicka 3082/12, 616 00 Brno, Czech Republic; [email protected] (O.D.); [email protected] (J.J.); [email protected] (N.H.); [email protected] (J.P.) 2 Department of Electronics Engineering, Faculty of Electrical and Electronics Engineering, Kaunas University of Technology, Studentu st. 48-209, LT-51367 Kaunas, Lithuania; [email protected] * Correspondence: [email protected]; Tel.: +420-541-146-560 Received: 14 November 2019; Accepted: 12 December 2019; Published: 19 December 2019 Abstract: This paper targets on the design and analysis of specific types of transfer functions obtained by the summing operation of integer-order and fractional-order two-port responses. Various operations provided by fractional-order, two-terminal devices have been studied recently. However, this topic needs to be further studied, and the topologies need to be analyzed in order to extend the state of the art. The studied topology utilizes the passive solution of a constant-phase element (with order equal to 0.5) implemented by parallel resistor–capacitor circuit (RC) sections operating as a fractional-order two-port. The integer-order part is implemented by operational amplifier-based lossless integrators and differentiators in branches with electronically adjustable gain, useful for time constant tuning. Four possible cases of the fractional-order and integer-order two-port interconnections are analyzed analytically, by PSpice simulations and also experimentally in the frequency range between 10 Hz and 1 MHz. -

Oscillation and Damping in the LRC Circuit

Experiment 2: Oscillation and Damping in the LRC Circuit Introduction In this laboratory you will construct an LRC series circuit and apply a constant voltage over it. You will view the voltage drop over the various elements of the circuit with the oscilloscope. You must change the order of the circuit elements in order to avoid shorting your circuit, but you will only construct one type of circuit throughout this experiment (LRC series). Also, this laboratory does not introduce much new physics to you since many of these topics have been covered in the previous two experiments. On the other hand, this experiment contains several new definitions and a more complicated differential equation, which result in a longer mathematical analysis. 1 Physics 1.1 Review of Kirchhoff’s Law Kirchhoff’s Law states that in any closed loop of a circuit the algebraic sum of the voltages of the elements in that loop will be zero. ―Algebraic‖ simply means signed. Elements in the circuit may either increase (add) voltage or drop (subtract) voltage. 1.2 Voltage Drops Over Various Circuit Elements Resistors, capacitors and inductors have well known voltage drops at direct current (DC) flows through those elements. Ohm’s Law describes that the voltage drop across a resistor is proportional to the current and the resistance: VR IR (1) The voltage drop across a capacitor is proportional to the charge held on either side of the capacitor. The charge is not always useful in equations mainly in terms of current, but luckily the charge on a capacitor is the integrated current over time: Q 1 V Idt (2) C C C An inductor is a tightly wound series of coils through which the current flows.