The Impact of Dennard's Scaling Theory Sscs NL0107 1/8/07 9:54 AM Page 2

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

On-Wafer Fabrication of Cavity Mirrors for Ingan-Based Laser Diode Grown

www.nature.com/scientificreports OPEN On-wafer fabrication of cavity mirrors for InGaN-based laser diode grown on Si Received: 25 January 2018 Junlei He1,2, Meixin Feng1,3, Yaozong Zhong1, Jin Wang1,4, Rui Zhou1,2, Hongwei Gao1,3, Yu Accepted: 17 April 2018 Zhou1,3, Qian Sun1,2,3, Jianxun Liu1, Yingnan Huang1, Shuming Zhang1,2, Huaibing Wang1, Published: xx xx xxxx Masao Ikeda1 & Hui Yang1,2 Direct bandgap III-V semiconductor lasers grown on silicon (Si) are highly desired for monolithic integration with Si photonics. Fabrication of semiconductor lasers with a Fabry–Pérot cavity usually includes facet cleavage, however, that is not compatible with on-chip photonic integration. Etching as an alternative approach holds a great advantage in preparing cavity mirrors with no need of breaking wafer into bars. However, gallium nitride (GaN) sidewalls prepared by dry etching often have a large roughness and etching damages, which would cause mirror loss due to optical scattering and carrier injection loss because of surface non-radiative recombination. A wet chemical polishing process of GaN sidewall facets formed by dry etching was studied in detail to remove the etching damages and smooth the vertical sidewalls. The wet chemical polishing technique combined with dry etching was successfully applied to the on-wafer fabrication of cavity mirrors, which enabled the realization of room temperature electrically injected InGaN-based laser diodes grown on Si. Silicon photonics call for electrically injected semiconductor laser diodes (LDs) as on-chip light sources1–3. When grown on Si, III-nitride (Al, Ga, In)N semiconductors with a direct-band emission wavelength ranging from 0.2 to 1.8 μm ofer a new approach for achieving on-chip lasers4–7. -

A Review of Different Etching Methodologies and Impact of Various Etchants in Wet Etching in Micro Fabrication

ISSN (Online) : 2319 – 8753 ISSN (Print) : 2347 - 6710 International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization, Volume 3, Special Issue 1, February 2014 International Conference on Engineering Technology and Science-(ICETS’14) On 10th & 11th February Organized by Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India A Review of Different Etching Methodologies and Impact of various etchants in Wet Etching in Micro Fabrication Benjamin. J1, Grace Jency. J2, Vijila. G3 Department of ECE, Karunya University, Karunya Nagar, Coimbatore – 641114, India1, 2, 3 Abstract-- The concept of miniaturization was each and every wafer undergo a lot of etching process. introduced because of advancement in science and The material which is used to protect the wafer from the technology during 1980s. These miniaturized etchants is known as the masking material, which is used structures and designs are of high significance for in many etching steps to resist etching. This masking making up with the macroscopic technology, for the material can be a photoresist and it is patterned using sake of interfacing with microscopic world. The photolithography.Etching can also be referred as making fabrication of micro structures and designs which are cavities and these cavities should have specific depth the advanced applications of micro fabrication are according to the purposes. The depth of such cavities used for the process of micromachining structures in produced can be controlled by etching time and the three dimensions as it is essential for interfacing with etching rate. -

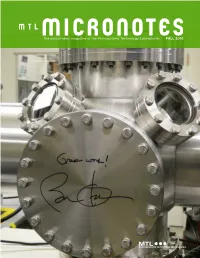

TSMC DAY at MIT 7 MTL DAY at FOXCONN 8 MTL DAY at TEXAS INSTRUMENTS MTL Teams with the DSP MEDICAL ELECTRONIC SYSTEMS Leadership University Program

The annual news magazine of the Microsystems Technology Laboratories FALL 2010 microsystems technology laboratories CONTENTS COLLABORATION AT ITS BEST 1 NOTES FROM THE DIRECTOR page 24 NEWS & EVENTS 2 MTL’S NEW FACULTY Introducing Li-Shiuan Peh & Dana Weinstein. 3 FOXCONN JOINS MIG 4 APPLIED MATERIALS Interactions with MTL in & out of the Fab. 5 BORN IN THE WRONG PLACE Andrea Cuomo of STMicroelectronics shares his company’s unique history. 6 TSMC DAY AT MIT 7 MTL DAY AT FOXCONN 8 MTL DAY AT TEXAS INSTRUMENTS MTL teams with the DSP MEDICAL ELECTRONIC SYSTEMS Leadership University Program. page 30 9 SAMSUNG DAY AT MTL; DR. CHANG-GYU HWANG 10 MIT & MASDAR INSTITUTE MIT & Masdar Institute develop microsystems education & research in the Middle East. 12 MARC2010 13 ENERGY RESEARCHERS FIND OBAMA AN EAGER STUDENT President showed keen interest, quick understanding and warm appreciation, say his hosts. 14 IN THE NEWS 40 GRADUATION WOMEN IN ENGINEERING FEATURE STORIES page 34 24 COLLABORATION AT ITS BEST Everyone wins when MTL and industry join forces. 30 MEDICAL ELECTRONIC SYSTEMS Can Boston become the “Silicon Valley of Medical Electronic Systems?” MTL researchers are working hard to make it happen. WOMEN IN ENGINEERING MIT’s Women’s Technology Program. ON THE COVER 34 Detail of President Barack Obama’s RESEARCH signature on a vacuum pump located in 16 MECHANICAL DEVICES STAMPED ON PLASTIC the Bulovic lab. Microelectromechanical devices gave us the Wii and the digital movie projector. MIT researchers have found a new way to make them. Photo courtesy, Bulovic lab. 18 STRAINING FORWARD Nanowires made of ‘strained silicon’— silicon whose atoms have been pried slightly apart — show how to keep increases in computer power coming. -

Etch Overview for Microsystems Primary Knowledge Participant Guide

Etch Overview for Microsystems Primary Knowledge Participant Guide Description and Estimated Time to Complete This Learning Module introduces the most common etch processes used in the fabrication of microsystems. Activities allow you to demonstrate your understanding of the terminology and basic concepts of these processes. This unit provides an overview of the etch processes as they apply to the fabrication of Microsystems or Microelectromechanical Systems (MEMS). It is designed to provide basic information on the etch processes and how they are used in the fabrication of MEMS. This unit will introduce you to etch terminology, purpose and processes. Additional instructional units provide more in-depth discussion of the topics introduced in this overview. Estimated Time to Complete Allow at least 30 minutes to review. Southwest Center for Microsystems Education (SCME) Page 1 of 21 Fab_Etch_PK00_PG_April2017.docx Etch Overview PK Introduction Pattern Transfer For microsystems fabrication etch is a process that removes select materials from • the wafer's surface, • below the wafer's surface, or • from within the substrate. The etch process normally follows photolithography or deposition during which a protective masking layer is applied to the wafer's surface. The protective masking layer is used to identify the material to be etched and to protect material that is to remain. The figure labeled “Pattern Transfer,” illustrates a mask pattern transferred into a photosensitive layer, shown in red (masking layer), on the wafer's surface (Photolithography Process). During the Etch Process (right), that pattern is transferred into the surface layer, removing exposed areas of the surface layer and leaving areas in the underlying layer open to a subsequent process step. -

High Resolution Inductively Coupled Plasma Etching of 30 Nm Lines and Spaces in Tungsten and Silicon Andrew L

High resolution inductively coupled plasma etching of 30 nm lines and spaces in tungsten and silicon Andrew L. Goodyeara) and Sinclair Mackenzie Oxford Instruments Plasma Technology, North End, Yatton, Bristol, United Kingdom Deirdre L. Olynick and Erik H. Anderson Lawrence Berkeley National Laboratory, Berkeley, California ͑Received 1 June 2000; accepted 23 August 2000͒ Dry etching of 30 nm features was investigated for x-ray and integrated electronics applications. These typically require etching of either a tungsten absorber layer or a silicon mold. Through the use of an inductively coupled plasma source and accurate control over substrate temperature it was possible to achieve highly anisotropic patterning of tungsten and silicon. Densely patterned features as small as 30 nm and at pitches of 70 nm were etched in tungsten and silicon, to depths of 100 and 200 nm, respectively. © 2000 American Vacuum Society. ͓S0734-211X͑00͒18406-9͔ I. INTRODUCTION takes this process further by producing the densely packed fine features with better sidewalls and higher aspect ratios. Patterning of sub-100 nm features has become essential This is critical for the production of the highest resolution for advanced research and development in electronics, op- x-ray optics. tics, and material science applications. This is especially true The etching of these fine features requires advanced and for x-ray applications such as microscopy zone plate lenses. sophisticated processes and equipment. The high ion density, The critical steps in the production of densely packed sub- low pressure ICP etch regime is one of the few ways to 100 nm features for x-ray applications are high resolution provide highly anisotropic profiles with excellent control e-beam lithography and precisely controlled dry etching of over selectivity to mask materials. -

IEEE Spectrum: 25 Microchip

IEEE Spectrum: 25 Microchips That Shook the World http://www.spectrum.ieee.org/print/8747 Sponsored By Select Font Size: A A A 25 Microchips That Shook the World By Brian R. Santo This is part of IEEE Spectrum 's Special Report: 25 Microchips That Shook the World . In microchip design, as in life, small things sometimes add up to big things. Dream up a clever microcircuit, get it sculpted in a sliver of silicon, and your little creation may unleash a technological revolution. It happened with the Intel 8088 microprocessor. And the Mostek MK4096 4-kilobit DRAM. And the Texas Instruments TMS32010 digital signal processor. Among the many great chips that have emerged from fabs during the half-century reign of the integrated circuit, a small group stands out. Their designs proved so cutting-edge, so out of the box, so ahead of their time, that we are left groping for more technology clichés to describe them. Suffice it to say that they gave us the technology that made our brief, otherwise tedious existence in this universe worth living. We’ve compiled here a list of 25 ICs that we think deserve the best spot on the mantelpiece of the house that Jack Kilby and Robert Noyce built. Some have become enduring objects of worship among the chiperati: the Signetics 555 timer, for example. Others, such as the Fairchild 741 operational amplifier, became textbook design examples. Some, like Microchip Technology’s PIC microcontrollers, have sold billions, and are still doing so. A precious few, like Toshiba’s flash memory, created whole new markets. -

Assessing the Impacts of Changes in the Information Technology R&D Ecosystem: Retaining Leadership in an Increasingly Global Environment

This PDF is available from The National Academies Press at http://www.nap.edu/catalog.php?record_id=12174 Assessing the Impacts of Changes in the Information Technology R&D Ecosystem: Retaining Leadership in an Increasingly Global Environment ISBN Committee on Assessing the Impacts of Changes in the Information 978-0-309-11882-8 Technology R & D Ecosystem: Retaining Leadership in an Increasingly Global Environment; National Research Council 204 pages 6 x 9 PAPERBACK (2009) Visit the National Academies Press online and register for... Instant access to free PDF downloads of titles from the NATIONAL ACADEMY OF SCIENCES NATIONAL ACADEMY OF ENGINEERING INSTITUTE OF MEDICINE NATIONAL RESEARCH COUNCIL 10% off print titles Custom notification of new releases in your field of interest Special offers and discounts Distribution, posting, or copying of this PDF is strictly prohibited without written permission of the National Academies Press. Unless otherwise indicated, all materials in this PDF are copyrighted by the National Academy of Sciences. Request reprint permission for this book Copyright © National Academy of Sciences. All rights reserved. Assessing the Impacts of Changes in the Information Technology R&D Ecosystem: Retaining Leadership in an Increasingly Global Environment Committee on Assessing the Impacts of Changes in the Information Technology Research and Development Ecosystem Computer Science and Telecommunications Board Division on Engineering and Physical Sciences Copyright © National Academy of Sciences. All rights reserved. Assessing the Impacts of Changes in the Information Technology R&D Ecosystem: Retaining Leadership in an Increasingly Global Environment THE NATIONAL ACADEMIES PRESS 500 Fifth Street, N.W. Washington, DC 20001 NOTICE: The project that is the subject of this report was approved by the Gov- erning Board of the National Research Council, whose members are drawn from the councils of the National Academy of Sciences, the National Academy of Engi- neering, and the Institute of Medicine. -

MOSTEK 1980 CIRCUITS and SYSTEMS PRODUCT GUIDE Mostek Reserves the Right to Make Changes in Specifications at Any Time and Without Notice

MOSTEK 1980 CIRCUITS AND SYSTEMS PRODUCT GUIDE Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believedto be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek. The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights ofthird parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at anytime and without notice. PRINTED IN USA April 1980 Publication Number Trade Marks Registered® STD No 01009 Copyright © 1980 Mostek Corporation (All rights reserved) II ~~~~~~~;;;;' Table of Contents '~~~~~~;;;;; Table of Contents ................................................... 111 Numerical Index ...................................................VIII Alphabetical Index . ................................................. x Mostek Profile -

RLE Currents | December 1988 (8.9Mb PDF)

Volume 2, Number 1 " December 1988 The Research Laboratory of Electronics at the Massachusetts Institute of Technology MATERIALS RESEARCH: Meeting the Challenge of Microelectronics Technology Since the discovery of the transis- tor at Bell Laboratories in 1947, scien- tists have been challenged by the need to produce materials for highly minia- turized and increasingly fast micro- electronic components. Driven by the technology of the information age, sci- entists have examined the unique properties of semiconductors, funda- mentally exploited new combinations of these novel materials, and devel- oped innovative design techniques to miniaturize electronic components. At the heart of this research is the ever- shrinking and exceedingly complex in- tegrated circuit microchip. In addition, the development of microscaled tran- sistors and other electronic compo- nents has resulted in systems with larg- er and faster capabilities, particularly for information processing and high- speed communication. I Every year since 1960, the number of circuit components on the most ad- Professor Henry I. Smith e.p loins the development of an alignment ststemJbr x-ray vanced microchip has nearly doubled. nanolithography that should be capable of 100-angstrom precision. Under his direction. Today, over 4 million transistors can be RLE's Submicron Structures Laboratory has pioneered new technologies in submicron onto one packed neatly computer structuresfabrication and explored deep -submicron MOSPETs and the exciting new memory or DRAM random (dynamic field of quantum-effect electronics (see related article on page 7.). Working with Prqfes- access memory) chip. The dramatic sor Dimitri Antoniadis and graduate student Ghavam Shahidi, dx. have discovered that miniaturization of electronic compo- the deleterious hot- electron effects seen in silicon MOSFETs with channel lengths below nents over the last forty years has raised 0.25 microns actually decrease at linewidths below 0.15 microns. -

Microcomputers: NQS PUBLICATIONS Introduction to Features and Uses

of Commerce Computer Science National Bureau and Technology of Standards NBS Special Publication 500-110 Microcomputers: NQS PUBLICATIONS Introduction to Features and Uses QO IGf) .U57 500-110 NATIONAL BUREAU OF STANDARDS The National Bureau of Standards' was established by an act ot Congress on March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides; (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau's technical work is per- formed by the National Measurement Laboratory, the National Engineering Laboratory, and the Institute for Computer Sciences and Technology. THE NATIONAL MEASUREMENT LABORATORY provides the national system of physical and chemical and materials measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; conducts materials research leading to improved methods of measurement, standards, and data on the properties of materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; develops, produces, and -

IBM Research Report SOI Series MOSFET for Embedded High

RC24545 (W0805-007) May 1, 2008 Electrical Engineering IBM Research Report SOI Series MOSFET for Embedded High Voltage Applications and Soft-Error Immunity Jin Cai, Tak Ning, Philip Oldiges*, Anthony Chou*, Arvind Kumar*, Werner Rausch*, Wilfried Haensch, Ghavam Shahidi IBM Research Division Thomas J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598 *IBM Semiconductor Research & Development Center Hopewell Junction, NY 12533 Research Division Almaden - Austin - Beijing - Cambridge - Haifa - India - T. J. Watson - Tokyo - Zurich LIMITED DISTRIBUTION NOTICE: This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distribution outside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g. , payment of royalties). Copies may be requested from IBM T. J. Watson Research Center , P. O. Box 218, Yorktown Heights, NY 10598 USA (email: [email protected]). Some reports are available on the internet at http://domino.watson.ibm.com/library/CyberDig.nsf/home . SOI Series MOSFET for Embedded High Voltage Applications and Soft-Error Immunity Jin Cai, Tak Ning, Philip Oldiges*, Anthony Chou*, Arvind Kumar*, Werner Rausch*, Wilfried Haensch and Ghavam Shahidi IBM Research Division, T. J. Watson Research Center, Yorktown Heights, NY 10598 * IBM Semiconductor Research & Development Center, Hopewell Junction, NY 12533 Phone: 914-945-2310; Fax: 914-945-2141; E-mail: [email protected]. -

2015 IEDM Conference Proceedings

2015 IEDM Conference Proceedings For More Information Social Networks: IEDM Online: ieee-iedm.org ieee-iedm.org/social-media Table of Contents Intro .....................................................3 Committees ...........................................3 Topics of Interest ....................................7 Program: Tutorials ................................................8 Short Courses ........................................8 Plenary Session ......................................9 Focus Session ........................................9 Technical Program ................................10 IEDM Luncheon ....................................11 Panel Discussion ..................................11 Entrepreneur’s Luncheon ........................11 Abstracts, Bios for Tutorials, Short Courses & Technical Program ......................Appendix 2020 IEEE International Electron Devices Meeting 2 Intro IEEE International Electron Devices Meeting (IEDM) is the world’s preeminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device technology, design, manufacturing, physics, and modeling. IEDM is the fl agship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation. Digital & Social Media •LinkedIn: https://www.linkedin.com/groups/7475096/ •Twitter: