The Structure of the "THE"-Multiprogramming System

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 1: Introduction What Is an Operating System?

Chapter 1: Introduction What is an Operating System? Mainframe Systems Desktop Systems Multiprocessor Systems Distributed Systems Clustered System Real -Time Systems Handheld Systems Computing Environments Operating System Concepts 1.1 Silberschatz, Galvin and Gagne 2002 What is an Operating System? A program that acts as an intermediary between a user of a computer and the computer hardware. Operating system goals: ) Execute user programs and make solving user problems easier. ) Make the computer system convenient to use. Use the computer hardware in an efficient manner. Operating System Concepts 1.2 Silberschatz, Galvin and Gagne 2002 1 Computer System Components 1. Hardware – provides basic computing resources (CPU, memory, I/O devices). 2. Operating system – controls and coordinates the use of the hardware among the various application programs for the various users. 3. Applications programs – define the ways in which the system resources are used to solve the computing problems of the users (compilers, database systems, video games, business programs). 4. Users (people, machines, other computers). Operating System Concepts 1.3 Silberschatz, Galvin and Gagne 2002 Abstract View of System Components Operating System Concepts 1.4 Silberschatz, Galvin and Gagne 2002 2 Operating System Definitions Resource allocator – manages and allocates resources. Control program – controls the execution of user programs and operations of I/O devices . Kernel – the one program running at all times (all else being application programs). -

Hematopoietic and Lymphoid Neoplasm Coding Manual

Hematopoietic and Lymphoid Neoplasm Coding Manual Effective with Cases Diagnosed 1/1/2010 and Forward Published August 2021 Editors: Jennifer Ruhl, MSHCA, RHIT, CCS, CTR, NCI SEER Margaret (Peggy) Adamo, BS, AAS, RHIT, CTR, NCI SEER Lois Dickie, CTR, NCI SEER Serban Negoita, MD, PhD, CTR, NCI SEER Suggested citation: Ruhl J, Adamo M, Dickie L., Negoita, S. (August 2021). Hematopoietic and Lymphoid Neoplasm Coding Manual. National Cancer Institute, Bethesda, MD, 2021. Hematopoietic and Lymphoid Neoplasm Coding Manual 1 In Appreciation NCI SEER gratefully acknowledges the dedicated work of Drs, Charles Platz and Graca Dores since the inception of the Hematopoietic project. They continue to provide support. We deeply appreciate their willingness to serve as advisors for the rules within this manual. The quality of this Hematopoietic project is directly related to their commitment. NCI SEER would also like to acknowledge the following individuals who provided input on the manual and/or the database. Their contributions are greatly appreciated. • Carolyn Callaghan, CTR (SEER Seattle Registry) • Tiffany Janes, CTR (SEER Seattle Registry) We would also like to give a special thanks to the following individuals at Information Management Services, Inc. (IMS) who provide us with document support and web development. • Suzanne Adams, BS, CTR • Ginger Carter, BA • Sean Brennan, BS • Paul Stephenson, BS • Jacob Tomlinson, BS Hematopoietic and Lymphoid Neoplasm Coding Manual 2 Dedication The Hematopoietic and Lymphoid Neoplasm Coding Manual (Heme manual) and the companion Hematopoietic and Lymphoid Neoplasm Database (Heme DB) are dedicated to the hard-working cancer registrars across the world who meticulously identify, abstract, and code cancer data. -

S5U1C88816P Manual (Peripheral Circuit Board for S1C88816/8F360)

MF1337-02a CMOS 8-BIT SINGLE CHIP MICROCOMPUTER S5U1C88816P Manual (Peripheral Circuit Board for S1C88816/8F360) NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. © SEIKO EPSON CORPORATION 2001 All rights reserved. Configuration of product number Devices S1 C 88104 F 0A01 00 Packing specifications 00 : Besides tape & reel 0A : TCP BL 2 directions 0B : Tape & reel BACK 0C : TCP BR 2 directions 0D : TCP BT 2 directions 0E : TCP BD 2 directions 0F : Tape & reel FRONT 0G : TCP BT 4 directions 0H -

The Effect of Muscular Exercise on the Blood Ammonia Concentration in Man

Yale University EliScholar – A Digital Platform for Scholarly Publishing at Yale Yale Medicine Thesis Digital Library School of Medicine 1959 The effect of muscular exercise on the blood ammonia concentration in man. With particular reference to patients with Laennec's Cirrhosis Scott nI gram Allen Yale University Follow this and additional works at: http://elischolar.library.yale.edu/ymtdl Recommended Citation Allen, Scott nI gram, "The effect of muscular exercise on the blood ammonia concentration in man. With particular reference to patients with Laennec's Cirrhosis" (1959). Yale Medicine Thesis Digital Library. 2334. http://elischolar.library.yale.edu/ymtdl/2334 This Open Access Thesis is brought to you for free and open access by the School of Medicine at EliScholar – A Digital Platform for Scholarly Publishing at Yale. It has been accepted for inclusion in Yale Medicine Thesis Digital Library by an authorized administrator of EliScholar – A Digital Platform for Scholarly Publishing at Yale. For more information, please contact [email protected]. VALE UNIVERSITY LIBRARY 3 9002 067 2 1757 CONCENTRATION IN MAN .A ixMt* MUDD LIBRARY Medical YALE MEDICAL LIBRARY Digitized by the Internet Archive in 2017 with funding from The National Endowment for the Humanities and the Arcadia Fund https://archive.org/details/effectofmuscularOOalle THE EFFECT OF MUSCULAR EXERCISE OH THE BLOOD AMMONIA CONCENTRATION IN MAN With Particular Reference To Patients With Laennec's Cirrhosis by Scott I. Allen, A.B. Nl Pomona College, 1955 A Thesis Submitted to the Faculty of the Yale University School of Medicine In Candidacy for the Degree of Doctor of Medicine Department of Internal. -

Concurrent Objects and Linearizability Concurrent Computaton

Concurrent Objects and Concurrent Computaton Linearizability memory Nir Shavit Subing for N. Lynch object Fall 2003 object © 2003 Herlihy and Shavit 2 Objectivism FIFO Queue: Enqueue Method • What is a concurrent object? q.enq( ) – How do we describe one? – How do we implement one? – How do we tell if we’re right? © 2003 Herlihy and Shavit 3 © 2003 Herlihy and Shavit 4 FIFO Queue: Dequeue Method Sequential Objects q.deq()/ • Each object has a state – Usually given by a set of fields – Queue example: sequence of items • Each object has a set of methods – Only way to manipulate state – Queue example: enq and deq methods © 2003 Herlihy and Shavit 5 © 2003 Herlihy and Shavit 6 1 Pre and PostConditions for Sequential Specifications Dequeue • If (precondition) – the object is in such-and-such a state • Precondition: – before you call the method, – Queue is non-empty • Then (postcondition) • Postcondition: – the method will return a particular value – Returns first item in queue – or throw a particular exception. • Postcondition: • and (postcondition, con’t) – Removes first item in queue – the object will be in some other state • You got a problem with that? – when the method returns, © 2003 Herlihy and Shavit 7 © 2003 Herlihy and Shavit 8 Pre and PostConditions for Why Sequential Specifications Dequeue Totally Rock • Precondition: • Documentation size linear in number –Queue is empty of methods • Postcondition: – Each method described in isolation – Throws Empty exception • Interactions among methods captured • Postcondition: by side-effects -

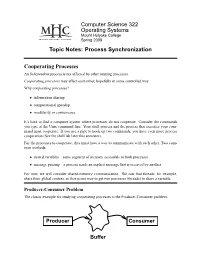

Computer Science 322 Operating Systems Topic Notes: Process

Computer Science 322 Operating Systems Mount Holyoke College Spring 2008 Topic Notes: Process Synchronization Cooperating Processes An Independent process is not affected by other running processes. Cooperating processes may affect each other, hopefully in some controlled way. Why cooperating processes? • information sharing • computational speedup • modularity or convenience It’s hard to find a computer system where processes do not cooperate. Consider the commands you type at the Unix command line. Your shell process and the process that executes your com- mand must cooperate. If you use a pipe to hook up two commands, you have even more process cooperation (See the shell lab later this semester). For the processes to cooperate, they must have a way to communicate with each other. Two com- mon methods: • shared variables – some segment of memory accessible to both processes • message passing – a process sends an explicit message that is received by another For now, we will consider shared-memory communication. We saw that threads, for example, share their global context, so that is one way to get two processes (threads) to share a variable. Producer-Consumer Problem The classic example for studying cooperating processes is the Producer-Consumer problem. Producer Consumer Buffer CS322 OperatingSystems Spring2008 One or more produces processes is “producing” data. This data is stored in a buffer to be “con- sumed” by one or more consumer processes. The buffer may be: • unbounded – We assume that the producer can continue producing items and storing them in the buffer at all times. However, the consumer must wait for an item to be inserted into the buffer before it can take one out for consumption. -

Personal-Computer Systems • Parallel Systems • Distributed Systems • Real -Time Systems

Module 1: Introduction • What is an operating system? • Simple Batch Systems • Multiprogramming Batched Systems • Time-Sharing Systems • Personal-Computer Systems • Parallel Systems • Distributed Systems • Real -Time Systems Applied Operating System Concepts 1.1 Silberschatz, Galvin, and Gagne Ď 1999 What is an Operating System? • A program that acts as an intermediary between a user of a computer and the computer hardware. • Operating system goals: – Execute user programs and make solving user problems easier. – Make the computer system convenient to use. • Use the computer hardware in an efficient manner. Applied Operating System Concepts 1.2 Silberschatz, Galvin, and Gagne Ď 1999 Computer System Components 1. Hardware – provides basic computing resources (CPU, memory, I/O devices). 2. Operating system – controls and coordinates the use of the hardware among the various application programs for the various users. 3. Applications programs – define the ways in which the system resources are used to solve the computing problems of the users (compilers, database systems, video games, business programs). 4. Users (people, machines, other computers). Applied Operating System Concepts 1.3 Silberschatz, Galvin, and Gagne Ď 1999 Abstract View of System Components Applied Operating System Concepts 1.4 Silberschatz, Galvin, and Gagne Ď 1999 Operating System Definitions • Resource allocator – manages and allocates resources. • Control program – controls the execution of user programs and operations of I/O devices . • Kernel – the one program running at all times (all else being application programs). Applied Operating System Concepts 1.5 Silberschatz, Galvin, and Gagne Ď 1999 Memory Layout for a Simple Batch System Applied Operating System Concepts 1.7 Silberschatz, Galvin, and Gagne Ď 1999 Multiprogrammed Batch Systems Several jobs are kept in main memory at the same time, and the CPU is multiplexed among them. -

Energy Estimation of Peripheral Devices in Embedded Systems Ozgur Celebican Vincent J

Energy Estimation of Peripheral Devices in Embedded Systems Ozgur Celebican Vincent J. Mooney III Center for Research on Embedded Tajana Simunic Rosing Center for Research on Embedded Systems and Technology, Hewlett-Packard Labs Systems and Technology, Electrical and Computer Engineering Palo Alto, CA, 94304-1126, USA Electrical and Computer Georgia Institute of Technology (1) 650 725 3647 Engineering Atlanta, GA, 30332-0250, USA [email protected] Georgia Institute of Technology (1) 404 3851722 Atlanta, GA, 30332-0250, USA [email protected] (1) 404 3850437 [email protected] ABSTRACT system. While increasing the energy capacity of the system is one approach to solve the problem, another approach is to optimize the This paper introduces a methodology for estimation of energy energy consumption of the system. A significant ratio of the energy consumption in peripherals such as audio and video devices. consumption for a state-of-the-art embedded system comes from Peripherals can be responsible for significant amount of the energy peripheral devices such as audio, video or network devices. Up to consumption in current embedded systems. We introduce a cycle- now, energy optimization for peripheral devices has been done with accurate energy simulator and profiler capable of simulating restricted methods. One method is to add up datasheet values for peripheral devices. Our energy estimation tool for peripherals can be each component. This method can give a rough estimate but cannot useful for hardware and software energy optimization of multimedia show effects of software. Another method is using prototypes. applications and device drivers. The simulator and profiler use Prototypes can give exact energy and performance numbers, but the cycle-accurate energy and performance models for peripheral devices cost of the prototype and time spent building the prototype is huge. -

Engineering Definitional Interpreters

Reprinted from the 15th International Symposium on Principles and Practice of Declarative Programming (PPDP 2013) Engineering Definitional Interpreters Jan Midtgaard Norman Ramsey Bradford Larsen Department of Computer Science Department of Computer Science Veracode Aarhus University Tufts University [email protected] [email protected] [email protected] Abstract In detail, we make the following contributions: A definitional interpreter should be clear and easy to write, but it • We investigate three styles of semantics, each of which leads to may run 4–10 times slower than a well-crafted bytecode interpreter. a family of definitional interpreters. A “family” is characterized In a case study focused on implementation choices, we explore by its representation of control contexts. Our best-performing ways of making definitional interpreters faster without expending interpreter, which arises from a natural semantics, represents much programming effort. We implement, in OCaml, interpreters control contexts using control contexts of the metalanguage. based on three semantics for a simple subset of Lua. We com- • We evaluate other implementation choices: how names are rep- pile the OCaml to 86 native code, and we systematically inves- x resented, how environments are represented, whether the inter- tigate hundreds of combinations of algorithms and data structures. preter has a separate “compilation” step, where intermediate re- In this experimental context, our fastest interpreters are based on sults are stored, and how loops are implemented. natural semantics; good algorithms and data structures make them 2–3 times faster than na¨ıve interpreters. Our best interpreter, cre- • We identify combinations of implementation choices that work ated using only modest effort, runs only 1.5 times slower than a well together. -

4. Process Synchronization

Lecture Notes for CS347: Operating Systems Mythili Vutukuru, Department of Computer Science and Engineering, IIT Bombay 4. Process Synchronization 4.1 Race conditions and Locks • Multiprogramming and concurrency bring in the problem of race conditions, where multiple processes executing concurrently on shared data may leave the shared data in an undesirable, inconsistent state due to concurrent execution. Note that race conditions can happen even on a single processor system, if processes are context switched out by the scheduler, or are inter- rupted otherwise, while updating shared data structures. • Consider a simple example of two threads of a process incrementing a shared variable. Now, if the increments happen in parallel, it is possible that the threads will overwrite each other’s result, and the counter will not be incremented twice as expected. That is, a line of code that increments a variable is not atomic, and can be executed concurrently by different threads. • Pieces of code that must be accessed in a mutually exclusive atomic manner by the contending threads are referred to as critical sections. Critical sections must be protected with locks to guarantee the property of mutual exclusion. The code to update a shared counter is a simple example of a critical section. Code that adds a new node to a linked list is another example. A critical section performs a certain operation on a shared data structure, that may temporar- ily leave the data structure in an inconsistent state in the middle of the operation. Therefore, in order to maintain consistency and preserve the invariants of shared data structures, critical sections must always execute in a mutually exclusive fashion. -

The Critical Section Problem Problem Description

The Critical Section Problem Problem Description Informally, a critical section is a code segment that accesses shared variables and has to be executed as an atomic action. The critical section problem refers to the problem of how to ensure that at most one process is executing its critical section at a given time. Important: Critical sections in different threads are not necessarily the same code segment! Concurrent Software Systems 2 1 Problem Description Formally, the following requirements should be satisfied: Mutual exclusion: When a thread is executing in its critical section, no other threads can be executing in their critical sections. Progress: If no thread is executing in its critical section, and if there are some threads that wish to enter their critical sections, then one of these threads will get into the critical section. Bounded waiting: After a thread makes a request to enter its critical section, there is a bound on the number of times that other threads are allowed to enter their critical sections, before the request is granted. Concurrent Software Systems 3 Problem Description In discussion of the critical section problem, we often assume that each thread is executing the following code. It is also assumed that (1) after a thread enters a critical section, it will eventually exit the critical section; (2) a thread may terminate in the non-critical section. while (true) { entry section critical section exit section non-critical section } Concurrent Software Systems 4 2 Solution 1 In this solution, lock is a global variable initialized to false. A thread sets lock to true to indicate that it is entering the critical section. -

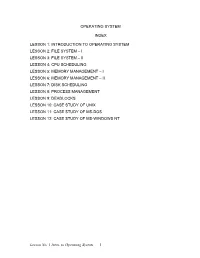

Operating System

OPERATING SYSTEM INDEX LESSON 1: INTRODUCTION TO OPERATING SYSTEM LESSON 2: FILE SYSTEM – I LESSON 3: FILE SYSTEM – II LESSON 4: CPU SCHEDULING LESSON 5: MEMORY MANAGEMENT – I LESSON 6: MEMORY MANAGEMENT – II LESSON 7: DISK SCHEDULING LESSON 8: PROCESS MANAGEMENT LESSON 9: DEADLOCKS LESSON 10: CASE STUDY OF UNIX LESSON 11: CASE STUDY OF MS-DOS LESSON 12: CASE STUDY OF MS-WINDOWS NT Lesson No. 1 Intro. to Operating System 1 Lesson Number: 1 Writer: Dr. Rakesh Kumar Introduction to Operating System Vetter: Prof. Dharminder Kr. 1.0 OBJECTIVE The objective of this lesson is to make the students familiar with the basics of operating system. After studying this lesson they will be familiar with: 1. What is an operating system? 2. Important functions performed by an operating system. 3. Different types of operating systems. 1. 1 INTRODUCTION Operating system (OS) is a program or set of programs, which acts as an interface between a user of the computer & the computer hardware. The main purpose of an OS is to provide an environment in which we can execute programs. The main goals of the OS are (i) To make the computer system convenient to use, (ii) To make the use of computer hardware in efficient way. Operating System is system software, which may be viewed as collection of software consisting of procedures for operating the computer & providing an environment for execution of programs. It’s an interface between user & computer. So an OS makes everything in the computer to work together smoothly & efficiently. Figure 1: The relationship between application & system software Lesson No.