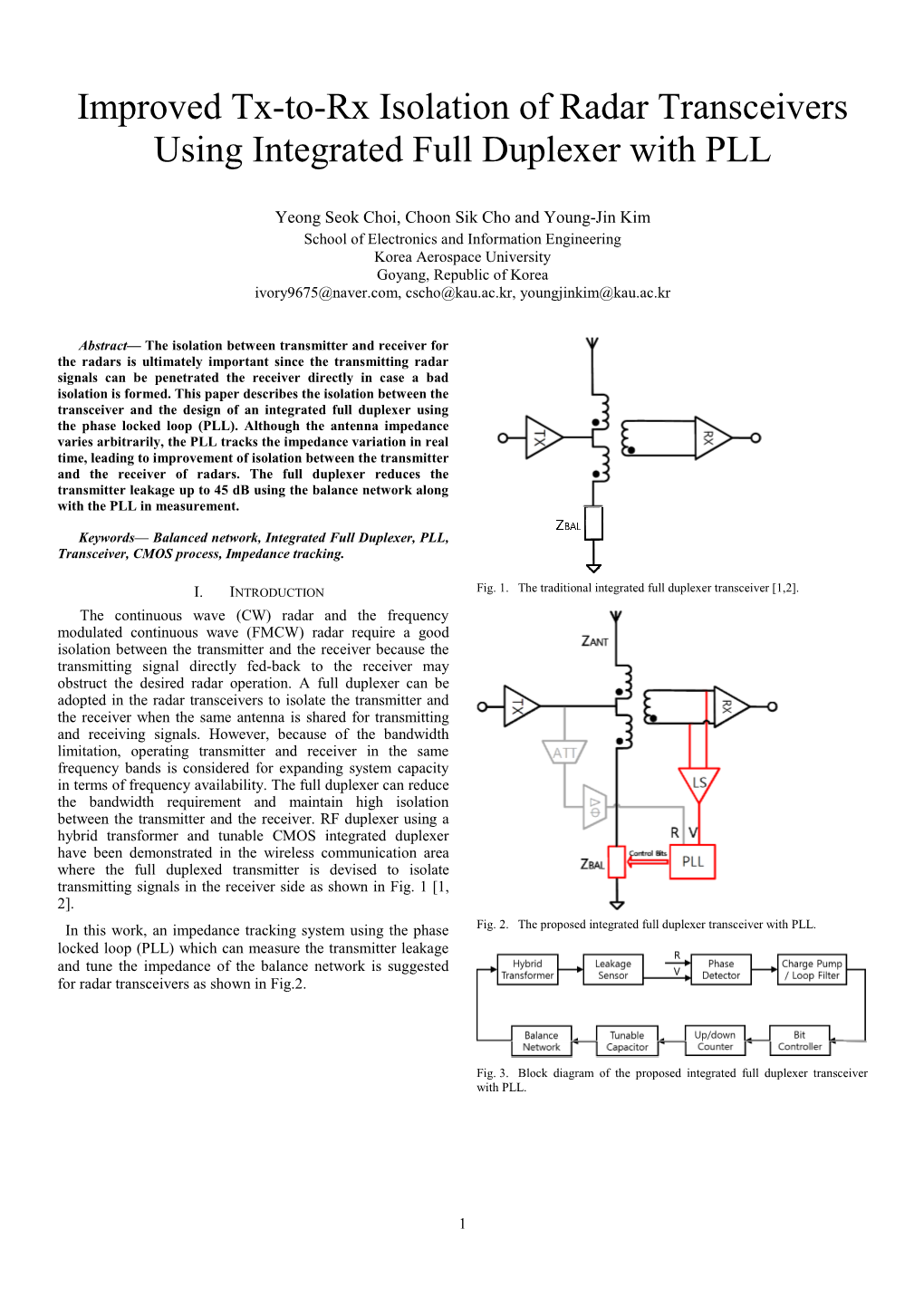

Improved Tx-To-Rx Isolation of Radar Transceivers Using Integrated Full Duplexer with PLL

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Understanding the Cavity Duplexer

i THE CAVITY DUPLEXER John E Portune W6NBC [email protected] rev 2019 NOTE FROM AUTHOR This book was written several years ago and based on hardware-store copper water pipe as the source of home-brew duplexer construction materials. Later I began making from spun-aluminum commercial cake pans. Both require no welding. Unfortunately the price of copper is today much higher. Cake pans, however, are still reasonably priced, readily available and very acceptable as the basis especially for VHF cavities. Because of maximum cavity size limit, copper water pipe may still be indicated for UHF and above. In any case, how a duplexer operates is basic physics. No matter what the material, or whether the duplexer is commercial or home brew, the principles herein are universal to duplexer construction, modification and tuning. This book, however, is not finished. Repeater building is no longer my primary interest in ham radio. Some subjects could be added. But as it contains the essentials, I have placed on the internet incomplete. If you reproduce it, be so kind as to give proper author’s credits. W6NBC January 2019 . ii CHAPTER OUTLINE 1. The Mysterious Duplexer • The black box everybody uses but nobody understands • Keys to understanding it • This is not a cookbook 2. Let’s Make a Cavity • Home-brew 2M aluminum cavity • Example for the entire book • The best way to learn 3. Cavities • Mechanical and electrical properties of cavities • Basic structure of a duplexer • Why use cavities • Getting energy in and out: loops, probes, taps and ports • Three cavity types: Bp, Br, Bp/Br • Creating the other types • Helical resonators for 6M and 10M duplexers 4. -

Two-Way Radio Success

www.IntercomsOnline.com Two-Way Radio Success How to Choose Two-Way Radios and Other Wireless Communication Devices. By David Onslow Copyright 2012, IntercomsOnline.com, all rights reserved 3rd Edition v3.1 For assistance in choosing the right two-way radio or communication product for you, visit www.intercomsonline.com or email us at the following address: 2 www.IntercomsOnline.com Introduction .............................................................................................................................. 5 Types of Two-Way Radios ....................................................................................................... 5 2-Way Radio Range: How Far Can Two-Way Radios Communicate? ..................................... 6 Two-Way Radio Power ........................................................................................................ 7 Radio Frequencies ............................................................................................................... 7 UHF Radio ..........................................................................................................................10 VHF Radio ..........................................................................................................................11 Commercial Digital Two-Way Radios ..................................................................................12 Antennas ................................................................................................................................13 Channel Usage .......................................................................................................................14 -

Raising the Bar for Two-Way Radio System Monitoring

Introducing… MOTOTRBO Next-Generation (See Pages 12-16) Two-Way Radios Outstanding New Features! Wireless Products Catalog. America’s Two-Way Radio Leader! Raising the Bar For Two-Way Radio OF WIR ER EL ID ES V S O S R O P L R U E T System Monitoring I I O M N E S R P BearCom (NOC) 1981-2016 Network Operations Center www.BearCom.com 800.527.1670 AMERICA’S ONLY NATIONWIDE WIRELESS TWO-WAY RADIO DEALER AND INTEGRATOR!800.527.1670 Two-Way Radios are an Excellent Investment for Nearly Any Organization! Every enterprise is looking for effective and economic solutions to: l Increase safety l Add growth l Achieve cost reductions l Streamline operations l Improve service Two-way radios provide enormous value by: Adding safety to protect people. Increasing efficiency to boost Examples how two-way radios productivity. improve accident prevention and Examples how two-way radios emergency response: optimize enterprise productivity: Worker Safety. Improve collaboration. An isolated worker suffers a health Instead of running back-and-forth on emergency. He can activate an alert on large job locations, team members his two-way radio to summon help. If he can stay at their work stations while collapses, the man-down feature sends requesting assistance and getting an instant notification. Many digital radios decisions made from across the site. also have GPS features. Result: Workers are more Result: Saving seconds can productive so jobs stay save a life. on-schedule, which increases profitability. Slip-and-Fall Prevention. The first worker on-scene can notify a Reduce downtime. -

About Duplexers Power

About Dupiexers Ever consider how difficult ordinary conversation would be if our telephone system were a "simplex" system? With a simplex system you talk to the other party, then listen, then talk again, etc. You cannot talk and listen at the same time. If you miss the first part of the other person's message, you have to wait until he is through talking before asking him to repeat it. This "built-in delay" slows down the thought process and makes an exchange of information more difficult, Forturiately, we aren't confronted with this problem because our telephone system is a "duplex" system and we can carryon a natural conversation. But what about our radio system? If a duplex system is superior to a simplex system, why are most of our radio systems simplex? Several reasons, the most common being: (1) A duplex system requires the use of two frequencies (one for trans- mit, one for receive) and only certain radio users can obtain authorization for use of a second frequency. (2) A duplex system requires additional equipment items and the system might be more costly than a simplex system. This booklet has been written (3) Certain unique technical problems must be overcome with a duplex for the many people engaged in system ... and that's what this booklet is all about. two-way r ad i 0 communications who are NOT radio engineers. A non-technical presentation of a The Simplex System. The typical simplex system consists of a trans- rather complex subject has been mitter and receiver operating on the attempted in an effort' to bring same frequency (Fig. -

Battery Life and How to Improve It

Battery Life and How To Improve It Battery and Energy Technologies Technologies Battery Life (and Death) Low Power Cells High Power Cells For product designers, an understanding of the factors affecting battery life is vitally important for managing both product Chargers & Charging performance and warranty liabilities particularly with high cost, high power batteries. Offer too low a warranty period and you won't Battery Management sell any batteries/products. Overestimate the battery lifetime and you could lose a fortune. Battery Testing Cell Chemistries FAQ That batteries have a finite life is due to occurrence of the unwanted chemical or physical changes to, or the loss of, the active materials of which Free Report they are made. Otherwise they would last indefinitely. These changes are usually irreversible and they affect the electrical performance of the cell. Buying Batteries in China Battery life can usually only be extended by preventing or reducing the cause of the unwanted parasitic chemical effects which occur in the cells. Choosing a Battery Some ways of improving battery life and hence reliability are considered below. How to Specify Batteries Battery cycle life is defined as the number of complete charge - discharge cycles a battery can perform before its nominal capacity falls below Sponsors 80% of its initial rated capacity. Lifetimes of 500 to 1200 cycles are typical. The actual ageing process results in a gradual reduction in capacity over time. When a cell reaches its specified lifetime it does not stop working suddenly. The ageing process continues at the same rate as before so that a cell whose capacity had fallen to 80% after 1000 cycles will probably continue working to perhaps 2000 cycles when its effective capacity will have fallen to 60% of its original capacity. -

Enrico Manuzzato Digitally-Controlled Electrical Balance Duplexer for Transmitter-Receiver Isolation in Full-Duplex Radio

ENRICO MANUZZATO DIGITALLY-CONTROLLED ELECTRICAL BALANCE DUPLEXER FOR TRANSMITTER-RECEIVER ISOLATION IN FULL-DUPLEX RADIO Master of Science thesis Examiner: prof. Mikko Valkama Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 9th December 2015 ABSTRACT ENRICO MANUZZATO: Digitally-Controlled Electrical Balance Duplexer for Transmit- ter-Receiver Isolation in Full-Duplex Radio. University of Trento and Tampere University of Technology Professor Mikko Valkama (Tampere University of Technology), Fabrizio Granelli (Uni- versity of Trento) Keywords: Antenna tuning, digital control, electrical balance duplexer, full-duplex ra- dio, hybrid junction, tracking, transmitter-receiver isolation. Today’s traditional radio systems exploit two techniques to transmit and receive which are Time Domain Duplexing (TDD) and Frequency Domain Duplexing (FDD). These two tech- niques allow bidirectional communication exploiting different frequencies or time-slots for the transmission and receiving operations. The ongoing research on wireless communications is currently active under in-band Full-Duplex (FD) radio communications, where co-located transmitter and receiver are operating simultaneously at the same central frequency doubling the spectral efficiency. The main technical challenge consists in suppressing the strong self- interference (SI) which is caused by the transmitting (TX) leakage into the receiving (RX) chain. Thus, FD transceivers need to provide high TX-RX isolation requirements in order to suppress the SI. Different methods are employed to mitigate the effect of the SI pursuing then FD operation. Generally, passive isolation between the TX and RX in the radio frequency (RF) domain can be built on specific antenna technologies or hybrid junction based electrical balance duplexers (EBD). -

The Cavity Duplexer

i THE CAVITY DUPLEXER John E. Portune W6NBC [email protected] Revised January 2019 NOTE FROM THE AUTHOR: This book was written several years ago and based on hardware-store copper water pipe as the source of home-brew duplexer construction materials. Later I began making duplexers from spun-aluminum commercial cake pans. Both require no welding. Unfortunately the price of copper is today much higher. Cake pans, however, are still reasonably priced, readily available and very acceptable as the basis especially for VHF cavities. Because of maximum cavity size limit, copper water pipe may still be indicated for UHF and above. In any case, how a duplexer operates is basic physics. No matter what the material, or whether the duplexer is commercial or home brew, the principles herein are universal to duplexer construction, modification and tuning. This book, however, is not finished. Repeater building is no longer my primary interest in ham radio. Some subjects could be added. But as it contains the essentials, I have placed on the internet incomplete. If you reproduce it, be so kind as to give proper author’s credits. W6NBC January 2019 . ii CHAPTER OUTLINE 1. The Mysterious Duplexer • The black box everybody uses but nobody understands • Keys to understanding it • This is not a cookbook 2. Let’s Make a Cavity • Home-brew 2M aluminum cavity • Example for the entire book • The best way to learn 3. Cavities • Mechanical and electrical properties of cavities • Basic structure of a duplexer • Why use cavities • Getting energy in and out: loops, probes, taps and ports • Three cavity types: Bp, Br, Bp/Br • Creating the other types • Helical resonators for 6M and 10M duplexers 4. -

Understanding the RF Path TABLE of CONTENTS

Understanding the RF path TABLE OF CONTENTS Chapter 1 Introduction: Welcome to RF communications 3 Chapter 2 The solutions, practices and trends: Cell site development 8 Chapter 3 Getting the signal across: Base station antennas 19 Chapter 4 Working within the limits: Co-siting solutions 44 Chapter 5 Talking and listening at the same time: Transmission and receiving isolation systems 59 Chapter 6 Getting from the air to the network: Cables and connectivity 76 Chapter 7 Clearing the connections: Overcoming passive intermodulation (PIM) 97 Chapter 8 Getting the most from every cycle: Spectrum management 105 Chapter 9 The infrastructure behind the call: Backhaul 115 Chapter 10 The next RF architecture evolution: C-RAN 137 Chapter 11 The energy of communications: Powering wireless networks 147 Chapter 12 Successfully planning against failure: Reliability in wireless systems 172 Chapter 13 Extending the network indoors: DAS, C-RAN antenna systems, and small cell solutions 187 Chapter 14 Finding safer ground: Lightning protection 196 Biographies 210 | Appendix A 214 | Glossary 219 www.commscope.com 2 Introduction: Welcome to RF communications Chapter 1 www.commscope.com 3 Introduction: Chapter 1 Welcome to RF communications Microwave backhaul The use of microwave communications to networks. It encompasses indoor wireless solutions that For decades, CommScope has grown up aggregate and transmit allow a mobile user to find a clear connection from alongside the science of communication with cellular voice and data anywhere in a vast building complex, aboard an aloft practical solutions. We have been dedicated to and from the main airliner or from a bullet train zipping through a tunnel network. -

The Historical Development of RADAR Science and Technology I1

Электронный научный журнал «ИССЛЕДОВАНО В РОССИИ» 1347 http://zhurnal.ape.relarn.ru/articles/2009/105e.pdf Scientific investigation, technological development and economical governmental support: the historical development of RADAR science and technology I1 Gorokhov V.G. ([email protected]) Institute for Philosophy of the Russian Academy of Sciences Institute for Technology Assessment and System Analysis of the Forschungszentrum Karlsruhe 1. Methodological Analysis of the History of RADAR Science and Technology as a Scientific and Technological Discipline The subject of methodological analysis in this article will be radar2 science and technology as a special discipline of scientific engineering (as distinct from the engineering industry). This choice is predetermined by the following factors. Firstly, radar theory emerged in the framework of a developed engineering science, and one may speak of its independent evolution as an engineering discipline. It has branched off from another engineering science (radio engineering theory) and did not initially emerge as an applied natural science. And second, the invention of radar resulted in truly revolutionary changes in industrial radio production, as well as in the respective fields of engineering science and practical activity which, in turn, produced a powerful impulse back to radar, turning it, in the latter part of the 20th century, into a modern complex engineering discipline, namely, radar systems engineering. Radar theory is discussed in this article not as much as a specific engineering science, but as a model of development of an engineering discipline. On the one hand, it is an object of systems study; on the other, it has given an impetus in engineering science and activity to the development of methodological principles of the systems approach. -

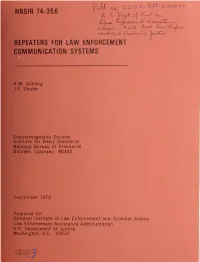

Repeaters for Law Enforcement Communication Systems

NBSIR 74-356 REPEATERS FOR LAW ENFORCEMENT COMMUNICATION SYSTEMS R.M. Jickling J.F. Shafer Electromagnetics Division Institute for Basic Standards National Bureau of Standards Boulder, Colorado 80302 September 1973 Prepared for National Institute of Law Enforcement and Criminal Justice Law Enforcement Assistance Administration U.S. Department of Justice Washington, D.C. 20537 NBSIR 74-356 REPEATERS FOR LAW ENFORCEMENT COMMUNICATION SYSTEMS R.M. Jickling J.F. Shafer Electromagnetics Division Institute for Basic Standards National Bureau of Standards Boulder,. Colorado 80302 September 1973 Prepared for National Institute of Law Enforcement and Criminal Justice Law Enforcement Assistance Administration U.S. Department of Justice Washington, D.C. 20537 U.S. DEPARTMENT OF COMMERCE, Frederick B. Dent, Secretary NATIONAL BUREAU OF STANDARDS. Richard W Roberts Director CONTENTS Page FOREWORD iv ABSTRACT 1 1. INTRODUCTION 1 2. REPEATER SYSTEMS 2 2.1 Repeaters Under Local Control 2 2.2 Repeater Under Remote Control 4 2.3 Repeaters Using Single Antenna and Duplexer- 4 2.4 Repeaters Using Two Antenna Sites 6 2.5 Repeaters Using Voting Receivers 6 2.6 Vehicular Transceiver as a Repeater 8 2.7 Repeaters for Microwave Frequencies 8 3. REPEATER SYSTEM ANCILLARY EQUIPMENT 10 3.1 Transmission Line Components 10 3.2 Failure-Mode Protection Components 12 3.3 Selective Tone-Coding Applications 12 4. REPEATER SYSTEM MEASUREMENTS FOR VHF AND UHF 13 5. GLOSSARY OF TERMS 14 6. ACKNOWLEDGMENT 16 7. REFERENCES 17 8. BIBLIOGRAPHY 18 iii . FOREWORD The National Bureau o£ Standards (NBS) has established a Law Enforcement Standards Laboratory (LESL) for the National Institute of Law Enforcement and Criminal Justice (NILECJ) of the Law Enforcement Assistance Administration, Department of Justice. -

Duplexer, Microstrip Filter, Fractional Bandwidth, Resonators

International Journal of Electromagnetics and Applications 2016, 6(1): 7-12 DOI: 10.5923/j.ijea.20160601.02 Design of Duplexers for Microwave Communication Systems Using Open-loop Square Microstrip Resonators Charles U. Ndujiuba1,*, Samuel N. John1, Taofeek O. Bello2 1Electrical & Information Engineering, Covenant University, Nigeria 2Electrical & Electronics Engineering, University of Lagos, Nigeria Abstract This paper proposes a duplexer design with two microstrip bandpass filters which are designed using Open Loop Square Resonator method and matching between these two bandpass filters using T-junction matching devices. Both seven-pole band-pass filters for the receiver at 1710-1785 MHz and transmitter at 1805-1880 MHz, with fractional bandwidth of 4.29% and 4.07% respectively, of the center frequencies were implemented by resonators and admittance inverters with a 0.1dB ripple in the pass band. Agilent Advance Design Simulation (ADS) EM simulator was used in obtaining the dimensions of the resonators, extraction of coupling coefficients and external quality factors associated with the microstrip design. Results obtained showed a return loss of about 8dB, insertion loss less than 1dB and isolation between transmit and receive filters of about 32dB. The choice of the square open-loop resonators against parallel coupled lines is to avoid the inherent shift in the center frequency of the parallel coupled technique. The designed microstrip duplexer filter showed good agreement with theoretical results. Keywords Duplexer, Microstrip filter, Fractional bandwidth, Resonators defects are particularly serious in duplexers where isolation 1. Introduction between the transmit and receive paths are required to be high, and multiplexers where adjacent channels must be Microwave communication systems require, especially in sharply and accurately defined. -

{TESS+} VHF Training Module 1: Overview of Two-Way VHF/UHF Radio Networks

{TESS+} VHF Training Module 1: Overview of two-way VHF/UHF radio networks Read more about {TESS+}: www.wfp.org/telecommunications-security-standards Email: [email protected] Session objectives • Describe a two-way radio system • Describe the difference between simplex and repeater operations Two-way radio communications • Two-way radio communication is a form of communication where both parties are involved in the transmission of information. • Push-to-talk (PTT) is an important aspect of a two-way radio where a PTT button activates the transmitter. When the button is released the radio switches to receive mode only. Two-way radio communications • Two-way radios are preferred because they are: • Flexible in programming as required and as licensed (VHF: 136-174MHZ) • Open standards • Frequency of use, intended use, location, and number of users will determine the choice of radio. Two-way radio communications - advantages • Advantages of a well-planned two-way radio system: • Instant communication (PTT) • Network independence • Call broadcast • Interoperability (iCOM, Motorola, RoIP: Radio over IP) • Emergency feature built in the device • Flexibility Two-way radio communications - contextual use To establish communication, the signal must be recognised. This is enabled through: - Carrier squelch - Tone squelch: – TPL (Tone Private Line) – SelV (Selective Voice) Two-way radio communications - simplex vs duplex • Two-way radios can operate in two modes: simplex and duplex 1. Simplex mode: – Radio stations communicate with each other directly, on the same frequency – No repeater or other device in between – Depends on the line of sight and radio output power Handheld radio range (simplex): approx. 5 – 7 km Mobile radio range (simplex): approx.