Wideband Automatic Gain Control Design in 130 Nm CMOS Process for Wireless Receiver Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 2 Basic Concepts in RF Design

Chapter 2 Basic Concepts in RF Design 1 Sections to be covered • 2.1 General Considerations • 2.2 Effects of Nonlinearity • 2.3 Noise • 2.4 Sensitivity and Dynamic Range • 2.5 Passive Impedance Transformation 2 Chapter Outline Nonlinearity Noise Impedance Harmonic Distortion Transformation Compression Noise Spectrum Intermodulation Device Noise Series-Parallel Noise in Circuits Conversion Matching Networks 3 The Big Picture: Generic RF Transceiver Overall transceiver Signals are upconverted/downconverted at TX/RX, by an oscillator controlled by a Frequency Synthesizer. 4 General Considerations: Units in RF Design Voltage gain: rms value Power gain: These two quantities are equal (in dB) only if the input and output impedance are equal. Example: an amplifier having an input resistance of R0 (e.g., 50 Ω) and driving a load resistance of R0 : 5 where Vout and Vin are rms value. General Considerations: Units in RF Design “dBm” The absolute signal levels are often expressed in dBm (not in watts or volts); Used for power quantities, the unit dBm refers to “dB’s above 1mW”. To express the signal power, Psig, in dBm, we write 6 Example of Units in RF An amplifier senses a sinusoidal signal and delivers a power of 0 dBm to a load resistance of 50 Ω. Determine the peak-to-peak voltage swing across the load. Solution: a sinusoid signal having a peak-to-peak amplitude of Vpp an rms value of Vpp/(2√2), 0dBm is equivalent to 1mW, where RL= 50 Ω thus, 7 Example of Units in RF A GSM receiver senses a narrowband (modulated) signal having a level of -100 dBm. -

A Wide Range and High Speed Automatic Gain Control

11111,.o 0 c_ SSCL-Preprint-407 = May 1993 "_ Distribution Category: 400 ' E. Tacconi rar_ t.. ' _ C Christiansen or3 ._ A Wide Range and High Speed Automatic Gain Control Superconductl "n g Super Collider Laboratory DISTRIIBLITION OF THIS DOCUMENT IS UNLIMITEi_ Disclaimer Notice This reportwas preparedas an account of work sponsoredby an agency of the UnitedStates Government. Neither the United States Governmentor any agency thereof, nor any of their employees,makesany warranty,expressor implied,or assumesanylegal liabilityor responsibility for the accuracy,completeness,or usefulnessof any information,apparatus,product,or process disclosed,or representsthat its usewouldnotinfringeprivatelyowned rights.Reference hereinto any specificcommercial product,process,or serviceby trade name, trademark, manufacturer,or otherwise, does notnecessarilyconstituteor implyits endorsement,recommendation,or favoring by the United States Government or any agency thereof. The views and opinionsof authors expressed herein donot necessadlystate or reflectthose ofthe UnitedStates Governmentor any agency thereof. Superconducting Super Collider Laboratory is an equal opportunity employer. SSCL-Preprint-407 A Wide Range and High Speed Automatic Gain Control* E. Tacconi and C. Christiansen Superconducting Super Collider Laboratory t 2550 Beckleymeade Ave. Dallas, TX 75237 May 1993 _ _' -12 -. _" *Presented at the 1993 IEEE Particle Accelerator Conference on May 17-20, Washington, D.C. *Operated by the Universities Research Association, Inc., for the U.S. Department of Energy under Contract No. DE-AC35-89ER40486. 131STRIBUI'ION OF THIS DOCUMENT IS UNLIMIT i=-O A Wide Range and High Speed Automatic Gain Control Eugenio J. Tacconit and Carlos F. Christiansen t Superconducting Super Collider Laboratory* 2550 Beckleymeade Avenue Dallas, Texas 75237 Abstract maximum loop gain, and a poor dynamic behavior is obtained Automatic gain control (AGC) techniques have been largely for low-gain operating points. -

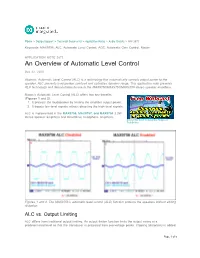

An Overview of Automatic Level Control

Maxim > Design Support > Technical Documents > Application Notes > Audio Circuits > APP 3673 Keywords: MAX9756, ALC, Automatic Level Control, AGC, Automatic Gain Control, Maxim APPLICATION NOTE 3673 An Overview of Automatic Level Control Dec 22, 2005 Abstract: Automatic Level Control (ALC) is a technology that automatically controls output power to the speaker. ALC prevents loudspeaker overload and optimizes dynamic range. This application note presents ALC technology and demonstrates its use in the MAX9756/MAX9757/MAX9758 stereo speaker amplifiers. Maxim's Automatic Level Control (ALC) offers two key benefits (Figures 1 and 2). 1. It protects the loudspeaker by limiting the amplifier output power. 2. It boosts low-level signals without distorting the high-level signals. ALC is implemented in the MAX9756, MAX9757, and MAX9758 2.3W stereo speaker amplifiers and DirectDrive headphone amplifiers. Attend this brief webcast by Maxim on TechOnline Figures 1 and 2. The MAX9756's automatic level control (ALC) function protects the speakers without adding distortion. ALC vs. Output Limiting ALC differs from traditional output limiting. An output-limiter function limits the output swing at a predetermined level so that the transducer is protected from overvoltage peaks. Clipping (distortion) is added Page 1 of 5 at the output signal as a result (Figure 3). An ALC function, however, reduces the gain so that the transducer is protected. No distortion is added (Figure 4). Figure 3. The output limiter clips the output signal in overvoltage conditions and, thus, produces audible distortion. Figure 4. The MAX9756's ALC reduces the amplifier gain in overvoltage conditions so that no distortion is added to the output signal. -

An Empirical Characterization of Concrete Channel and Modulation Schemes with Piezoelectric Transducers Based Transceivers

AN EMPIRICAL CHARACTERIZATION OF CONCRETE CHANNEL AND MODULATION SCHEMES WITH PIEZO ELECTRIC TRANSDUCERS BASED TRANSCEIVERS A Thesis Presented to the Faculty of the Department of Electrical and Computer Engineering University of Houston In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering by Sai Shiva Kailaswar August 2012 AN EMPIRICAL CHARACTERIZATION OF CONCRETE CHANNEL AND MODULATION SCHEMES WITH PIEZOELECTRIC TRANSDUCERS BASED TRANSCEIVERS _______________________________________ Sai Shiva Kailaswar Approved: ______________________________ Chair of the Committee Dr. Rong Zheng, Associate Professor Electrical and Computer Engineering Committee Members: ______________________________ Dr. Zhu Han, Associate Professor Electrical and Computer Engineering ______________________________ Dr. Yuhua Chen, Associate Professor Electrical and Computer Engineering ______________________________ ______________________________ Dr. Suresh Khator, Dr. Badri Roysam, Associate Dean Professor and Chairman Cullen College of Engineering Electrical and Computer Engineering ACKNOWLEDGEMENTS This research would not have been possible without the support of God Almighty and all praise to him. I owe my deepest gratitude to Dr. Rong Zheng for giving me an opportunity to pursue my Master’s thesis under her esteemed guidance. Without her support and assistance, this project would not have been possible. Her timely support, encouragement, and logical thinking have greatly inspired me to keep my spirits high throughout the research. I would like to thank Dr. Zhu Han and Dr. Yuhua Chen for accepting my invitation to serve on my thesis committee. It gives me pleasure to thank all the members of the Wireless System Research Group, especially Mr. Guanbo Zheng. I would like to dedicate my work to my beloved parents, brother, Mr. Kishore Potta, and sister-in-law Mrs. -

UNIVERSITY of CALIFORNIA Los Angeles Wideband Reconfigurable Blocker Tolerant Receiver for Cognitive Radio Applications a Disser

UNIVERSITY OF CALIFORNIA Los Angeles Wideband Reconfigurable Blocker Tolerant Receiver for Cognitive Radio Applications A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering by Qaiser Nehal 2018 c Copyright by Qaiser Nehal 2018 ABSTRACT OF THE DISSERTATION Wideband Reconfigurable Blocker Tolerant Receiver for Cognitive Radio Applications by Qaiser Nehal Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2018 Professor Asad A. Abidi, Chair Cognitive radios (CRs) use \white spaces" in spectrum for communication. This requires front-end circuits that are highly linear when the white space is adjacent to a strong blocker. For example, in the TV spectrum (54 MHz-862 MHz) broadcast transmissions are the block- ers. This work describes the design of a wideband blocker tolerant receiver. First EKV based MOSFET model is used to analyze RF transconductor distortion. Expressions for its IIP3 and P1dB are also given. Derivative superposition based linearization scheme for the RF transconductor is also explained. Second mixer switch nonlinearity is analyzed using EKV. Simple expressions for receiver IIP3 and P1dB are given that provide design insights for linearity optimization. Low phase noise LO design is also described to lower receiver noise figure in the presence of large blockers. Finally, transimpedance amplifier (TIA) large-signal operation is studied using EKV. It is shown that source follower inverter-based TIA transconductor results in higher receiver P1dB. A prototype receiver based on these ideas was designed in 16nm FinFET CMOS. Mea- sured results show that receiver can operate from 100 MHz to 6 GHz and can tolerate up to +12 dBm blockers. -

Gan Essentials™

APPLICATION NOTE AN-010 GaN Essentials™ AN-010: GaN for LDMOS Users NITRONEX CORPORATION 1 JUNE 2008 APPLICATION NOTE AN-010 GaN Essentials: GaN for LDMOS Users 1. Table of Contents 1. TABLE OF CONTENTS................................................................................................................................... 2 2. ABSTRACT......................................................................................................................................................... 3 IMPEDANCE PROFILES.......................................................................................................................................... 3 2.1. INPUT IMPEDANCE .................................................................................................................................... 3 2.2. OUTPUT IMPEDANCE ................................................................................................................................ 4 3. STABILITY ......................................................................................................................................................... 5 4. CAPACITANCE VS. VOLTAGE ................................................................................................................... 6 4.1. TYPICAL CAPACITANCE -VOLTAGE (CV) CHARACTERISTICS ................................................................ 6 4.2. OUTPUT CAPACITANCE COMPARISON BETWEEN GAN AND LDMOS .................................................. 7 5. BIAS CIRCUITS................................................................................................................................................ -

Replacing the Automatic Gain Control Loop in a Mobile, Digital TV Broadcast Receiver by a Software Based Solution

Replacing the automatic gain control loop in a mobile, digital TV broadcast receiver by a software based solution diploma thesis Patrick Boettcher Technische Fachhochschule Wildau Fachbereich Betriebswirtschaft/Wirtschaftsinformatik Date: 09.03.2008 Erstbetreuer: Prof. Dr. Christian Müller Zweitbetreuer: Prof. Dr. Bernd Eylert ii A part of this diploma thesis is not available until April 2010, because it is protected by a lock flag. The complete work can and will be made available by that time. The parts affected are – Chapter 4, – Chapter 5, – Appendix C and – Appendix D. If by that time you cannot find the complete work anywhere, please contact the author. iii Danksagung An dieser Stelle möchte ich all jenen danken, die durch ihre fachliche und persönliche Unterstützung zum Gelingen dieser Diplomarbeit beigetragen haben. Besonderer Dank gebührt meiner Lebenspartnerin Ariane und meinen Eltern, die mir dieses Studium durch ihre Unterstützung ermöglicht haben und mir fortwährend Vorbild und Ansporn waren. Weiterhin bedanke ich mich bei Professor Dr. Christian Müller und Professor Dr. Bernd Eylert für die Betreuung dieser Diplomarbeit. Großer Dank gilt ebenfalls meinen Kollegen bei DiBcom S.A., die mir die Möglichkeit gaben, diese Arbeit zu verfassen und mich technich sehr stark unterstützten. Vor allem möchte ich mich in diesem Zusammenhang bei Jean-Philippe Sibers bedanken, der mir immer mit einer Inspriration zur Seite stand. Gleiches gilt für das „Physical Layer Software Team“: Luc Banda, Frédéric Tarral und Vincent Recrosio. Acknowledgment I want to use this opportunity to thank everyone who supported me personally and professionally to create this diploma thesis. Special thanks appertain to my partner Ariane and my parents, who supported me during my studies and who continuously guided and motivated me. -

Next Topic: NOISE

ECE145A/ECE218A Performance Limitations of Amplifiers 1. Distortion in Nonlinear Systems The upper limit of useful operation is limited by distortion. All analog systems and components of systems (amplifiers and mixers for example) become nonlinear when driven at large signal levels. The nonlinearity distorts the desired signal. This distortion exhibits itself in several ways: 1. Gain compression or expansion (sometimes called AM – AM distortion) 2. Phase distortion (sometimes called AM – PM distortion) 3. Unwanted frequencies (spurious outputs or spurs) in the output spectrum. For a single input, this appears at harmonic frequencies, creating harmonic distortion or HD. With multiple input signals, in-band distortion is created, called intermodulation distortion or IMD. When these spurs interfere with the desired signal, the S/N ratio or SINAD (Signal to noise plus distortion ratio) is degraded. Gain Compression. The nonlinear transfer characteristic of the component shows up in the grossest sense when the gain is no longer constant with input power. That is, if Pout is no longer linearly related to Pin, then the device is clearly nonlinear and distortion can be expected. Pout Pin P1dB, the input power required to compress the gain by 1 dB, is often used as a simple to measure index of gain compression. An amplifier with 1 dB of gain compression will generate severe distortion. Distortion generation in amplifiers can be understood by modeling the amplifier’s transfer characteristic with a simple power series function: 3 VaVaVout=−13 in in Of course, in a real amplifier, there may be terms of all orders present, but this simple cubic nonlinearity is easy to visualize. -

A Wide Range and High Speed Automatic Gain Control Eugenio J

© 1993 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. A Wide Range and High Speed Automatic Gain Control Eugenio J. Tacconit and Carlos F. Christiansen~ Superconducting Super Collider Laboratory* 2550 Beckleymeade Avenue, MS 4004 Dallas, Texas 75237 Abstract The gain of the controlled amplifier is a function of the Automatic gain control (AGC) techniques have been control voltage x(t). Thus, the control system is non linear largely used since the beginning of electronics but in most of and gain loop and stability are usually dependent on the the applications the dynamic responseis slow compared with operating point. The system has to be designed in order to be the carrier frequency. The problem of developing an stable for the maximum loop gain and a poor dynamic automatic gain control having simultaneously high dynamic behavior is obtained for low gain operating points. The effect response‘and wide control range is analyzed in this work. An of the gain control law on the loop gain variation range is ideal gain control law, having the property that the total loop analyzed in the next section. gain remains constant independent of the carrier amplitude, is obtained. The resulting AGC behavior is compared, by It. GAINCONTROL LAW computer simulations, with a linear multiplier AGC. The ideal gain control law can be approximated by using a The output of the variable gain amplifier is given by: transconductanceamplifier. -

Automatic Gain Control and Multi-Style Training for Robust Small-Footprint Keyword Spotting with Deep Neural Networks

AUTOMATIC GAIN CONTROL AND MULTI-STYLE TRAINING FOR ROBUST SMALL-FOOTPRINT KEYWORD SPOTTING WITH DEEP NEURAL NETWORKS Rohit Prabhavalkar1, Raziel Alvarez1, Carolina Parada1, Preetum Nakkiran2∗, Tara N. Sainath1 1Google Inc., Mountain View, USA; 2University of California, Berkeley, Department of EECS, USA fprabhavalkar, raziel, carolinap, [email protected] [email protected] ABSTRACT We explore techniques to improve the robustness of small-footprint keyword spotting models based on deep neural networks (DNNs) in the presence of background noise and in far-field conditions. We find that system performance can be improved significantly, with rel- ative improvements up to 75% in far-field conditions, by employing a combination of multi-style training and a proposed novel formula- tion of automatic gain control (AGC) that estimates the levels of both Fig. 1: Block diagram of DNN-based KWS system proposed in [2]. speech and background noise. Further, we find that these techniques allow us to achieve competitive performance, even when applied to method was shown to significantly outperform a baseline keyword- DNNs with an order of magnitude fewer parameters than our base- filler system. This system is appealing for our task because it can line. be implemented very efficiently to run in real-time on devices, and Index Terms— keyword spotting, automatic gain control, memory and power consumption can be easily adjusted by chang- multi-style training, small-footprint models ing the number of parameters in the DNN. Although the proposed system works extremely well in clean conditions, performance de- grades significantly when speech is corrupted by noise, or when the 1. INTRODUCTION distance between the speaker and the microphone increases (i.e., in far-field conditions). -

Application of AGC Technology in Software Radio

International Journal of Advanced Network, Monitoring and Controls Volume 03, No.04, 2018 Application of AGC Technology in Software Radio Wu Hejing East University of Heilongjiang 150086 e-mail: [email protected] Abstract—The characteristics of software radio are flexibility, (2) openness. Software radio adopts a standardized and openness, scalability. The hardware platform of software radio modular structure. Its hardware can be updated or expanded should be a general platform. This paper discusses automatic with the development of devices and technologies. gain control(AGC) technology in software radio receiver and (3) scalability. Software radio can be upgraded by introduces an AGC algorithm applicable for DSP implement. loading new software. This algorithm is tested in matlab and simulation results are III. ARCHITECTURE OF SOFTWARE RADIO provided. Software radio architecture is the concrete design Keywords-Software Radio; Characteristics; AGC; Matlab structure torealize the concept of software radio. It includes hardware, software and interface protocol. The design I. INTRODUCTION content must take into account the current situation and At present, software radio technology is widely used in long-term development of wireless communication wireless communication, its basic idea is to use hardware as technology. Really unifies each standard. The structure of the basic platform of wireless communication. The A/D ideal software radio is mainly composed of antenna, RF front sampling data of signals are processed by various algorithms, end, broadband A/D-D/A soft converter, General and special and various communication functions are realized by means digital signal processors and various software components. of software. This paper discusses the automatic gain control The antenna of software radio generally covers a wide (AGC) algorithm in software radio. -

5 Steps to Selecting the Right RF Power Amplifier

modular rf 5 Steps to Selecting the Right RF Power Amplifier Jason Kovatch Sr. Development Engineer AR Modular RF, Bothell WA You need an RF power amplifier. You have measured the power of your signal and it is not enough. You may even have decided on a power level in Watts that you think will meet your needs. Are you ready to shop for an amplifier of that wattage? With so many variations in price, size, and efficiency for amplifiers that are all rated at the same number of Watts many RF amplifier purchasers are unhappy with their selection. Some of the unfortunate results of amplifier selection by Watts include: unacceptable distortion or interference, insufficient gain, premature amplifier failure, and wasted money. Following these 5 steps will help you avoid these mistakes. Step 1 - Know Your Signal Step 2 – Do the Math Step 3 - Window Shopping Step 4 - Compare Apples to Apples Step 5 – Shopping for Bells and Whistles Step 1 – Know Your Signal You need to know 2 things about your signal: what type of modulation is on the signal and the actual Peak power of your signal to be amplified. Knowing the modulation is the most important as it defines broad variations in amplifiers that will provide acceptable performance. Knowing the Peak power of your signal will allow you calculate your gain and/or power requirements, as shown in later steps. Signal Modulation and Power- CW, SSB, FM, and PM are Easy To avoid distortion, amplifiers need to be able to faithfully process your signal’s peak power.