Computer Networks

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Introduction to the Ipaddress Module

Introduction to the ipaddress Module An Introduction to the ipaddress Module Overview: This document provides an introduction to the ipaddress module used in the Python language for manipulation of IPv4 and IPv6 addresses. At a high level, IPv4 and IPv6 addresses are used for like purposes and functions. However, since there are major differences in the address structure for each protocol, this tutorial has separated into separate sections, one each for IPv4 and IPv6. In today’s Internet, the IPv4 protocol controls the majority of IP processing and will remain so for the near future. The enhancements in scale and functionality that come with IPv6 are necessary for the future of the Internet and adoption is progressing. The adoption rate, however, remains slow to this date. IPv4 and the ipaddress Module: The following is a brief discussion of the engineering of an IPv4 address. Only topics pertinent to the ipaddress module are included. A IPv4 address is composed of 32 bits, organized into four eight bit groupings referred to as “octets”. The word “octet” is used to identify an eight-bit structure in place of the more common term “byte”, but they carry the same definition. The four octets are referred to as octet1, octet2, octet3, and octet4. This is a “dotted decimal” format where each eight-bit octet can have a decimal value based on eight bits from zero to 255. IPv4 example: 192.168.100.10 Every packet in an IPv4 network contains a separate source and destination address. As a unique entity, a IPv4 address should be sufficient to route an IPv4 data packet from the source address of the packet to the destination address of the packet on a IPv4 enabled network, such as the Internet. -

The Essentials of Computer Organization and Architecture / Linda Null, Julia Lobur

the essentials of Linda Null and Julia Lobur JONES AND BARTLETT COMPUTER SCIENCE the essentials of Linda Null Pennsylvania State University Julia Lobur Pennsylvania State University World Headquarters Jones and Bartlett Publishers Jones and Bartlett Publishers Jones and Bartlett Publishers International 40 Tall Pine Drive Canada Barb House, Barb Mews Sudbury, MA 01776 2406 Nikanna Road London W6 7PA 978-443-5000 Mississauga, ON L5C 2W6 UK [email protected] CANADA www.jbpub.com Copyright © 2003 by Jones and Bartlett Publishers, Inc. Cover image © David Buffington / Getty Images Illustrations based upon and drawn from art provided by Julia Lobur Library of Congress Cataloging-in-Publication Data Null, Linda. The essentials of computer organization and architecture / Linda Null, Julia Lobur. p. cm. ISBN 0-7637-0444-X 1. Computer organization. 2. Computer architecture. I. Lobur, Julia. II. Title. QA76.9.C643 N85 2003 004.2’2—dc21 2002040576 All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form, electronic or mechanical, including photocopying, recording, or any information storage or retrieval system, without written permission from the copyright owner. Chief Executive Officer: Clayton Jones Chief Operating Officer: Don W. Jones, Jr. Executive V.P. and Publisher: Robert W. Holland, Jr. V.P., Design and Production: Anne Spencer V.P., Manufacturing and Inventory Control: Therese Bräuer Director, Sales and Marketing: William Kane Editor-in-Chief, College: J. Michael Stranz Production Manager: Amy Rose Senior Marketing Manager: Nathan Schultz Associate Production Editor: Karen C. Ferreira Associate Editor: Theresa DiDonato Production Assistant: Jenny McIsaac Cover Design: Kristin E. -

Chapter 2 Data Representation in Computer Systems 2.1 Introduction

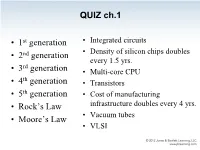

QUIZ ch.1 • 1st generation • Integrated circuits • 2nd generation • Density of silicon chips doubles every 1.5 yrs. rd • 3 generation • Multi-core CPU th • 4 generation • Transistors • 5th generation • Cost of manufacturing • Rock’s Law infrastructure doubles every 4 yrs. • Vacuum tubes • Moore’s Law • VLSI QUIZ ch.1 The highest # of transistors in a CPU commercially available today is about: • 100 million • 500 million • 1 billion • 2 billion • 2.5 billion • 5 billion QUIZ ch.1 The highest # of transistors in a CPU commercially available today is about: • 100 million • 500 million “As of 2012, the highest transistor count in a commercially available CPU is over 2.5 • 1 billion billion transistors, in Intel's 10-core Xeon • 2 billion Westmere-EX. • 2.5 billion Xilinx currently holds the "world-record" for an FPGA containing 6.8 billion transistors.” Source: Wikipedia – Transistor_count Chapter 2 Data Representation in Computer Systems 2.1 Introduction • A bit is the most basic unit of information in a computer. – It is a state of “on” or “off” in a digital circuit. – Sometimes these states are “high” or “low” voltage instead of “on” or “off..” • A byte is a group of eight bits. – A byte is the smallest possible addressable unit of computer storage. – The term, “addressable,” means that a particular byte can be retrieved according to its location in memory. 5 2.1 Introduction A word is a contiguous group of bytes. – Words can be any number of bits or bytes. – Word sizes of 16, 32, or 64 bits are most common. – Intel: 16 bits = 1 word, 32 bits = double word, 64 bits = quad word – In a word-addressable system, a word is the smallest addressable unit of storage. -

Topics Today

CMSC 313 COMPUTER ORGANIZATION & ASSEMBLY LANGUAGE PROGRAMMING LECTURE 01, SPRING 2013 TOPICS TODAY • Course overview • Levels of machines • Machine models: von Neumann & System Bus • Fetch-Execute Cycle • Base Conversion COURSE OVERVIEW CMSC 313 Course Description Spring 2013 Computer Organization & Assembly Language Programming Instructor. Prof. Richard Chang, [email protected], 410-455-3093. Office Hours: Tuesday & Thursday 11:30am–12:30pm, ITE 326. Teaching Assistant. Roshan Ghumare, [email protected] Office Hours: TBA Time and Place. Section 01: Tu - Th 10:00am – 11:15am, ITE 229. Section 02: Tu - Th 1:00pm – 2:15pm, ITE 229. Textbook. • Essentials of Computer Organization and Architecture, third edition, by Linda Null & Julia Lobur. Jones & Bartlett Learning, 2010. ISBN: 1449600069. • Assembly Language Step-by-Step: Programming with Linux, third edition, by Jeff Duntemann. Wiley, 2009. ISBN: 0470497025. Web Page. http://umbc.edu/~chang/cs313/ Catalog Description. This course introduces the student to the low-level abstraction of a computer system from a programmer's point of view, with an emphasis on low-level programming. Topics include data representation, assembly language programming, C programming, the process of compiling and linking, low-level memory management, exceptional control flow, and basic processor architecture. Prerequisites. You should have mastered the material covered in the following courses: CMSC 202 Computer Science II and CMSC 203 Discrete Structures. You need the programming experience from CMSC202. Additional experience from CMSC341 Data Structures would also be helpful. You must also be familiar with and be able to work with truth tables, Boolean algebra and modular arithmetic. Objectives. The purpose of this course is to introduce computer science majors to computing systems below that of a high-level programming language. -

CS5865 Laboratory #1 Notes File Transfer Protocols

1 CS5865 Laboratory #1 Notes File Transfer Protocols - An Overview Dr. B.J. Kurz XMODEM (Ward Christensen, 1970), one of the earliest ‘industry standard’ file transfer protocols in the public domain. HDX operation, character (byte)-oriented, fixed-length 128-byte blocks, 8-bit characters (bytes), 8-bit BCC = sum-mod256, stop-wait ARQ, block counts, binary data capability. Poor error detection capability, typically 95%. data block format: SOH/count/1’s compl. count/ user data/BCC control block format: ACK or NAK (or C), EOT Several later versions of XMODEM are in use: XMODEM-CRC same as regular XMODEM above except uses 8-bit BCC = CRC-8 (some implementations use 16-bit BCC = CRC-16). Better error detection capability, typically 99.97% (for CRC-8). Some versions negotiate the error character generation method: the sender first tries sum- mod256 BCC, then switches to CRC-8 BCC after three unsuccessful attempts indicated by NAKs from the receiver. XMODEM-1K same as XMODEM-CRC except uses 1024-byte blocks for better throughput (fewer line- turn-arounds), but slightly degraded error detection performance. WXMODEM a sliding-window version of XMODEM. Group size is fixed as 4 blocks. Much improved throughput. FDX capable lines needed if continous-ARQ error recovery used. YMODEM (Chuck Forsberg) a variation of XMODEM-1K. Supports two block lengths of 128 bytes and 1024 bytes, uses 2-byte CRC-16, excellent error detection capability, typically 99.99%. KERMIT (Frank de Cruz, Columbia Univ. Comp. Center, N.Y), most popular file transfer protocol, copyrighted, over 200 implementations for various systems. This is a comprehensive 2 remote communications package including terminal emulators, storage-to-storage transfer, not only a file transfer protocol. -

Flow Control and ARQ Media Access Physical

Data Link Layer The Data Link layer can be further subdivided into: Computer Networks application 1. Logical Link Control (LLC): provides flow and error control transport • different link protocols may provide different services, e.g., Ethernet doesn’t provide reliable network delivery (error recovery) Lecture 26: 2. Media Access Control (MAC): framing and LLC MAC Flow Control and ARQ media access physical Link Layer Services Flow Control Flow Control: What is flow control? • pacing between adjacent sending and receiving nodes • receiver telling sender to slow down Error Control: Why do you need flow control? • errors caused by signal attenuation, noise • ARQ: receiver detects presence of errors and asks sender for retransmission Flow control protocols at data link layer (single hop): • FEC: receiver identifies and corrects bit error(s), • XON/XOFF without resorting to retransmission • Stop & Wait Protocol • Sliding Window Protocol Reliable delivery between adjacent nodes • seldom used on low bit error links (fiber, some twisted pair) Similar issues and mechanisms apply at the • plays an important role in wireless links with high error rates transport layer (end-to-end) • Q: why do we need both link-level and end-end reliability? XON/XOFF Stop and Wait (S&W) Protocol ! : propagation After sending a packet, sender must wait for delay SR acknowledgment (ACK) before sending the next packet sender receiver Sender Receiver S R round-trip Algorithm: time (rtt) t • S sends stream of data Time ! : propagation • R sends XOFF, S stops transmission pkt -

Effect of Sliding Window Techniques Over a Performance of Tcp/Ip Networks

EFFECT OF SLIDING WINDOW TECHNIQUES OVER A PERFORMANCE OF TCP/IP NETWORKS ABBAS ABEDI JANUARY, 2018 EFFECT OF SLIDING WINDOWS TECHNIQUES OVER A PERFORMANCE OF TCP/IP NETWORKS A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF CANKAYA UNIVERSITY BY ABBAS ABEDI IN PARTIAL FULLFILLMENT OF a REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN THE DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING JANUARY, 2018 ABSTRACT EFFECT OF SLIDING WINDOWS TECHNIQUES OVER A PERFORMANCE OF TCP/IP NETWORKS ABEDI, Abbas M.Sc., Department of Electronics and Communication Engineering Supervisor: Asst. Prof. Dr. Barbaros PREVEZE January 2018 The communication channels have a variety of features in the communication system and networks, particularly wireless channels. It is used in transmissions between two nodes and deals with high error rates. Such errors that occur frequently which are not easy to be avoided, have the greatest effect on the performance of a network. So, it must be concluded that error rates are for different network conditions with use of different types of sliding windows techniques. In this thesis, error correcting techniques have been investigated based on a retransmission technique they used. One of the famous retransmission techniques is sliding windows technique, which it has three sub-algorithms called: stop and wait, selective repeat, and go back N. In this work, selective repeat and go back N algorithms were taken into account, but a stop and wait algorithm was not considered since it doesn’t use any window structure in their retransmissions. Also, it always has a high delay amount with less performance compared to the selective repeat and go back N techniques. -

The Kermit File Transfer Protocol

THE KERMIT FILE TRANSFER PROTOCOL Frank da Cruz February 1985 This is the original manuscript of the Digital Press book Kermit, A File Transfer Protocol, ISBN 0-932976-88-6, Copyright 1987, written in 1985 and in print from 1986 until 2001. This PDF file was produced by running the original Scribe markup-language source files through the Scribe publishing package, which still existed on an old Sun Solaris computer that was about to be shut off at the end of February 2016, and then converting the resulting PostScript version to PDF. Neither PostScript nor PDF existed in 1985, so this result is a near miracle, especially since the last time this book was "scribed" was on a DECSYSTEM-20 for a Xerox 9700 laser printer (one of the first). Some of the tables are messed up, some of the source code comes out in the wrong font; there's not much I can do about that. Also (unavoidably) the page numbering is different from the printed book and of couse the artwork is missing. Bear in mind Kermit protocol and software have seen over 30 years of progress and development since this book was written. All information herein regarding the Kermit Project, how to get Kermit software, or its license or status, etc, is no longer valid. The Kermit Project at Columbia University survived until 2011 but now it's gone and all Kermit software was converted to Open Source at that time. For current information, please visit the New Open Source Kermit Project website at http://www.kermitproject.org (as long as it lasts). -

Data Representation in Computer Systems

© Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION There are 10 kinds of people in the world—those who understand binary and those who don’t. © Jones & Bartlett Learning, LLC © Jones—Anonymous & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION © Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION CHAPTER Data Representation © Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE 2OR DISTRIBUTIONin ComputerNOT FOR Systems SALE OR DISTRIBUTION © Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION 2.1 INTRODUCTION he organization of any computer depends considerably on how it represents T numbers, characters, and control information. The converse is also true: Stan- © Jones & Bartlettdards Learning, and conventions LLC established over the years© Jones have determined& Bartlett certain Learning, aspects LLC of computer organization. This chapter describes the various ways in which com- NOT FOR SALE putersOR DISTRIBUTION can store and manipulate numbers andNOT characters. FOR SALE The ideas OR presented DISTRIBUTION in the following sections form the basis for understanding the organization and func- tion of all types of digital systems. The most basic unit of information in a digital computer is called a bit, which is a contraction of binary digit. In the concrete sense, a bit is nothing more than © Jones & Bartlett Learning, aLLC state of “on” or “off ” (or “high”© Jones and “low”)& Bartlett within Learning, a computer LLCcircuit. In 1964, NOT FOR SALE OR DISTRIBUTIONthe designers of the IBM System/360NOT FOR mainframe SALE OR computer DISTRIBUTION established a conven- tion of using groups of 8 bits as the basic unit of addressable computer storage. -

Courier V.Everything External Modem: Getting Started

Courier V.Everything External Modem: Getting Started FINAL 4/96 p/n 1.024.492 1996 U.S. Robotics Access Corp. 8100 North McCormick Blvd. Skokie, IL 60076-2999 All Rights Reserved U.S. Robotics and the U.S. Robotics logo are registered trademarks of U.S. Robotics Access Corp. V.Fast Class and V.FC are trademarks of Rockwell International. Any trademarks, tradenames, service marks or service names owned or registered by any other company and used in this manual are the property of their respective companies. 1996 U.S. Robotics Access Corp. 8100 N. McCormick Blvd. Skokie, IL 60076-2999 USA Table of Contents About This Manual iii We Welcome Your Suggestions.............................................................iii Chapter 1 The Courier 1-1 Courier Controls, Displays, and Connectors.....................................1-3 Status Indicators ....................................................................................1-4 Features...................................................................................................1-5 Chapter 2 Installing the Courier 2-1 What You Need......................................................................................2-1 Package Contents...................................................................................2-3 Installing the Courier ............................................................................2-4 Setting the DIP Switches.......................................................................2-4 Powering On the Courier .....................................................................2-6 -

Configuration Parameters

Good news, everyone! User Documentation Version: 2020-01-01 M. Brutman ([email protected]) http://www.brutman.com/mTCP/ Table of Contents Introduction and Setup Introduction..............................................................................................................................................................8 What is mTCP?...................................................................................................................................................8 Features...............................................................................................................................................................8 Tested machines/environments...........................................................................................................................9 Licensing...........................................................................................................................................................10 Packaging..........................................................................................................................................................10 Binaries.....................................................................................................................................................................10 Documentation..........................................................................................................................................................11 Support and contact information.......................................................................................................................11 -

Electronic Bulletin Board System for the Federal Depository Library Program

GP 3.2:E1 2 Electronic Bulletin Board System for the Federal Depository Library Program: A Study Library Programs Service U.S. Government Printing Office Superintendent of Documents Washington, D.C. 1991 tr Electronic Bulletin Board System for the Federal Depository Library Program A Study Written by: Marian W. MacGilvray Joseph P. Paskoski John M. Walters Project Director: Joseph C. McClane February 1, 1991 Library Programs Service U.S. Government Printing Office Washington, D.C. U.S. Government Printing Office Robert W. Houk, Public Printer Superintendent of Documents (Vacant) Library Programs Service Bonnie B. Trivizas, Director Library Division Gil Baldwin, Chief Depository Services Staff Joseph C. McClane, Chief Any use of trade, product, or firm names in this publication is for descriptive purposes only and does not imply endorsement by the U.S. Government. Table of Contents Preface , iv I. Executive Summary and Recommendations 1 II. Introduction A. Federal Depository Library Program 2 B. Basis of the Study 2 C. Scope of the System 2 D. Study Methodology 2 III. Bulletin Board Systems - General Characteristics 3 IV. FDLP Bulletin Board System - System Description A. File Characteristics and Size 4 B. Usage Characteristics 7 C. Staffing 7 D. Telecommunications . 7 E. System Configuration Options and Costs 8 F. Implementation Schedule 11 Bibliography 13 Appendix A. Recommendations, Depository Library Council 14 Appendix B. List of Consultants 15 Appendix C. Suggestions for File Content 18 Appendix D. Alternate Technologies 20 Appendix E. Hardware and Software 25 iii Preface A preliminary draft of "Electronic Bulletin Board • the system will be beta tested with the 54 System for the Federal Depository Library Program: A regional depositories before being made Study" was completed on October 15, 1990 and available to all depository libraries.