TPS75003 Configurable Multi-Rail PMIC Datasheet (Rev. J)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ina21x Voltage Output

Product Order Technical Tools & Support & Folder Now Documents Software Community INA210, INA211, INA212, INA213, INA214, INA215 SBOS437J –MAY 2008–REVISED FEBRUARY 2017 INA21x Voltage Output, Low- or High-Side Measurement, Bidirectional, Zero-Drift Series, Current-Shunt Monitors 1 Features 3 Description The INA21x are voltage-output, current-shunt 1• Wide Common-Mode Range: –0.3 V to 26 V monitors (also called current-sense amplifiers) that • Offset Voltage: ±35 μV (Maximum, INA210) are commonly used for overcurrent protection, (Enables Shunt Drops of 10-mV Full-Scale) precision-current measurement for system • Accuracy: optimization, or in closed-loop feedback circuits. This – Gain Error (Maximum Over Temperature): series of devices can sense drops across shunts at common-mode voltages from –0.3 V to 26 V, – ±0.5% (Version C) independent of the supply voltage. Six fixed gains are – ±1% (Versions A and B) available: 50 V/V, 75 V/V, 100 V/V, 200 V/V, 500 V/V, – 0.5-µV/°C Offset Drift (Maximum) or 1000 V/V. The low offset of the zero-drift architecture enables current sensing with maximum – 10-ppm/°C Gain Drift (Maximum) drops across the shunt as low as 10-mV full-scale. • Choice of Gains: These devices operate from a single 2.7-V to 26-V – INA210: 200 V/V power supply, drawing a maximum of 100 µA of – INA211: 500 V/V supply current. All versions are specified over the – INA212: 1000 V/V extended operating temperature range (–40°C to +125°C), and offered in SC70 and UQFN – INA213: 50 V/V packages. -

Performance Characteristics of IC Packages 4

Performance Characteristics of IC Packages 4 4.1 IC Package Electrical Characteristics As microprocessor speeds have increased and power supply voltages have decreased, the function of the microprocessor package has transitioned from that of a mechanical interconnect which provides protection for the die from the outside environment to that of an electrical interconnect that affects microprocessor performance and which must be properly understood in an electrical context. Inherent in understanding the electrical performance effects of the package is the need for electrical characterization of the package. The package is a complex electrical environment and the characterization of this environment is a multi-faceted task that consists of models constructed from both theoretical calculations and experimental measurements. In simple terms, a package electrical model translates the physical properties of a package into electrical characteristics that are usually combined into a circuit representation. The typical electrical circuit characteristics that are reported are DC resistance (R), inductance (L), capacitance (C), and characteristic impedance (Z_o) of various structures in the package. A package model consists of two parts, both of which are necessary for fully understanding the electrical performance effects of the package environment on Intel’s microprocessors. The first is an I/O lead model that describes the signal path from the die to the board. Depending upon the complexity of the model required for simulation purposes, the I/O lead model can take the form of a simple lumped circuit model, a distributed lumped circuit model, a single-conductor transmission-line model, or a multiple-conductor transmission-line model. While lumped models can adequately model simple effects, such as DC resistive voltage drop, more sophisticated models like the multiple-conductor transmission-line model include effects such as time delay and crosstalk. -

Semiconductor Products Statement Concerning SCIP And

STATEMENT REGARDING EU-Waste Framework Directive Integrated Circuit Products Effective date: 07 February 2021 To our valued customers: The European Union’s amended Waste Framework Directive (WFD)1, among other things, requires EU manufacturers and importers Companies that produce, import or supply articles containing substances of very high concern (SVHCs) meeting certain requirements to register those products in the SCIP database (Substances of Concern In articles as such or in complex objects (Products)). This obligation is for articles produced in the EU or imported from non-EU countries. As a first importer of articles into the EU market Microchip Technology Incorporated (Microchip) understands the obligations to register with ECHA and to facilitate the flow of information to our supply chain. As of the date above, none of the articles in Microchip’s integrated circuit products have been found to have equal to or greater than 0.1% weight overweight of any of the 211 SVHCs, except for those identified within attachment “A”. All products identified within attachment “A” will be submitted by Microchip to ECHA and assigned a SCIP number. Should you have any questions, please contact your sales representative (http://www.microchip.com/distributors/SalesHome.aspx) or visit ECHA website (https://echa.europa.eu/scip) Ben Gross Senior Manager, Compliance- Trade and Corporate Social Responsibility Microchip Technology Inc. 2355 W. Chandler Blvd., Chandler, AZ 85224 1 1 Directive (EU) 2018/851 of the European Parliament and of the Council of 30 May 2018 amending Directive 2008/98/EC Page 1 of 8 Attachment “A” : Modules BMxx / RN4xx / KLRxx / and System in Package (SIP) and XXBall Grid Arrays (xxBGA) packages may contain thick film resistors with [lead monoxide (1317-36-8)] and/or ceramic capacitors or inductors with [diboron trioxide (1303- 86-2)] Di-boron trioxide. -

Application of Diffusion Bonding to Electronic

APPLICATION OF DIFFUSION BONDING TO ELECTRONIC INTERCONNECTION OF FLATPACK LEADS (NASA-CR-124460) APPLICATION OF DIFFUSION N73-33429 BONDING TO ELECTRONIC INTERCONNECTION OF FLATPACK LEADS Summary Report (Hughes Aircraft Co.) 114-p HC $7.75 CSCL 11 Unclas 1 G3/17 15799 SUMMARY REPORT JULY 1973 Prepared By R. W.Korb V. F. Lardenoit Contract No. NAS 8-28269 6 Prepared For George C. Marshall Space Flight Center National Aeronautics and Space Administration Marshall Space Flight Center Alabama 35812 ------------------- HUGHES HUGHES AIRCRAFT COMPANY Ground Systems Group P.O. Box 3310, Fullerton, CA 92634 FR-73-01-580 APPLICATION OF DIFFUSION BONDING TO ELECTRONIC INTERCONNECTION OF FLATPACK LEADS SUMMARY REPORT JULY 1973 PREPARED BY R. W. KORB V. F. LARDENOIT CONTRACT NO. NAS 8-28269 PREPARED FOR GEORGE C. MARSHALL SPACE FLIGHT CENTER NATIONAL AERONAUTICS AND SPACE ADMINISTRATION MARSHALL SPACE FLIGHT CENTER ALABAMA 35812 HUGHES AIRCRAFT COMPANY GROUND SYSTEMS GROUP P.O. BOX 3310 FULLERTON, CA 92634 FR73-10-580 IMIG PAGE BLANK NOT FILMED ACKNOWLEDGMENT Appreciation is extended to the following persons for their assistance in the preparation of this report: J. R. Shackleton for performing scanning electron microscopy and x-ray analyses L. J. Yarber for making bonds and performing pull tests J. L. Ewing for typing and preparation of the rough draft. iii ABSTRACT This investigation conducted under Contract No. NAS 8-28269 consisted of testing and evaluating diffusion bonds using low melting metals between gold-plated Kovar lead material and copper circuit pads. The investigation was conducted in three parts consisting of (1) an evaluation of the physical strength of resulting bonds at ambient and elevated temperature, (2) a metallurgical analysis of bonds using scanning electron microscopy and nondispersive x-ray analysis and (3) evaluation and development of various schemes for multiple lead flatpack bonding. -

Transistor Standards (Ts)

JEDEC Publication No. 95 TRANSISTORS OUTLINES (TO) Contents TO-3 Diamond Base, .430 Pin Spacing TO-5 Axial Leads, .200 Pin Circle TO-8 Axial Leads, .281 Pin Circle TO-9 Axial Leads, .200 Pin Circle TO-12 Axial Leads, .200 Pin Circle TO-18 Axial Leads, .100 Pin Circle TO-33 4 Axial Leads, .200 Pin Circle TO-37 Diamond Base, .200 Pin Circle TO-39 Axial Leads, .200 Pin Circle TO-41 Diamond Base, .430 Pin Circle TO-42 Axial Leads, .200 Pin Circle TO-46 Axial Leads, .100 Pin Circle TO-66 Diamond Base, .200 Pin Spacing TO-72 4 Axial Leads, .100 Pin Circle TO-73 12 Axial Leads, .200 Pin Circle TO-74 10 Axial Leads, .200 Pin Circle TO-75 6 Axial Leads, .200 Pin Circle TO-76 8 Axial Leads, .200 Pin Circle TO-77 8 Axial Leads, .200 Pin Circle TO-78 8 Axial Leads, .200 Pin Circle TO-79 8 Axial Leads, .200 Pin Circle TO-80 8 Axial Leads, .200 Pin Circle TO-84 Multiple-Ended 14-Lead Flatpack TO-85 Multiple-Ended 14-Lead Flatpack TO-86 Multiple-Ended 14-Lead Flatpack TO-87 Double-Ended 14-Lead Flatpack TO-88 Double-Ended 14-Lead Flatpack TO-89 Double-Ended 10-Lead Flatpack TO-90 Double-Ended 10-Lead Flatpack TO-91 Double-Ended 10-Lead Flatpack TO-92 Axial Leaded, Flat Index TO-94 Stud-Mount Flex Leads TO-95 Double-Ended 14-Lead Flatpack TO-96 10 Axial Leads, .230 Pin Circle TO-97 10 Axial Leads, .230 Pin Circle TO-99 8 Axial Leads, .200 Pin Circle TO-100 10 Axial Leads, .230 Pin Circle TO-101 12 Axial Leads, .230 Pin Circle TO-117 Lateral, 4 Flat Leads TO-123 Diamond Base, .200 Pin Circle TO-124 Diamond Base, .200 Pin Circle TO-126 Flat Lead .090” pin spacing -i- Updated 01/12 JEDEC Publication No. -

SN65MLVD204B Multipoint-LVDS Line Drivers and Receivers (Transceivers) with IEC ESD Protection

SN65MLVD204B www.ti.com SLLSEN0C – NOVEMBER 2015 – REVISEDSN65MLVD204B SEPTEMBER 2020 SLLSEN0C – NOVEMBER 2015 – REVISED SEPTEMBER 2020 SN65MLVD204B Multipoint-LVDS Line Drivers and Receivers (Transceivers) With IEC ESD Protection 1 Features receivers which are optimized to operate at signaling rates up to 100 Mbps. This device family has robust • Compatible with the M-LVDS Standard TIA/ 3.3-V drivers and receivers in the standard SOIC and EIA-899 for Multipoint Data Interchange QFN footprint for demanding industrial applications. • Low-Voltage Differential 30-Ω to 55-Ω Line Drivers The bus pins are robust to ESD events, with high and Receivers for Signaling Rates(1) Up to 100 levels of protection to human-body model and IEC Mbps, Clock Frequencies up to 50 MHz contact discharge specifications. – Type-2 Receiver Provides an Offset Threshold The SN65MLVD204B combine a differential driver to Detect Open-Circuit and Idle-Bus Conditions and a differential receiver (transceiver), which operate • Bus I/O Protection from a single 3.3-V supply. The transceivers are – >±8-kV HBM optimized to operate at signaling rates up to 100 – >±8-kV IEC 61000-4-2 Contact Discharge Mbps. • Controlled Driver Output Voltage Transition Times The SN65MLVD204B has enhancements over similar for Improved Signal Quality devices. Improved features include a controlled slew • -1-V to 3.4-V Common-Mode Voltage Range rate on the driver output to help minimize reflections Allows Data Transfer With 2 V of Ground Noise from unterminated stubs, resulting in better signal • Bus Pins High Impedance When Disabled or VCC ≤ integrity. The same footprint definition was 1.5 V maintained, allowing for an easy drop-in replacement • 200-Mbps Device Available (SN65MLVD206B) 1 for a system performance upgrade. -

Packages and Landpatterns Page 1 JEDEC Number Family Description

Packages and LandPatterns Registered Passive IPC-SM-782 Component Land Pattern Faabmedia land Land Pattern Generic JEDEC Number Identifier Number pattern name Status Symbol Family Description Pins DO-217 Button Rectifier Button Rectifier DO-200 Disc Type Disc Type DO-211 Cancelled replaced by TO-244-AA-AB Flange Mounted Family Flange Mounted Family (Rectangular base) DO-213 Leadless Family DO-213 AA 200A IPC-RLPN-200A Done Metal Electrode Face (MELF) Components SOD-80/MLL 34 Diode DO-204 Lead Mounted Family Lead Mounted Family (Round Lead Axial) DO-204-AA DO-204-AA DO-204-AB DO-204-AB DO-204-AC DO-204-AC DO-204-AD DO-204-AD DO-204-AE DO-204-AE DO-204-AF DO-204-AF DO-204-AG DO-204-AG DO-204-AH DO-204-AH DO-204-AJ DO-204-AJ DO-204-AK DO-204-AK DO-204-AL DO-204-AL Done DO-204-AM DO-204-AM DO-204-AN DO-204-AN DO-204-AP DO-204-AP DO-204-AR DO-204-AR SOD 123 220A IPC-RLPN-220A Done Plastic Surface Mount Family C Bend Plastic Surface-Mount DO-214AA SMB 221A IPC-RLPN-221A Done DO-215 Plastic Surface Mount Family Gull Wing Plastic Surface-Mount DO-216 Plastic Surface Mount Family Gull Wing Plastic Surface-Mount DO-218 Plastic Surface Mount Family Power Outline Plastic Surface Mount C-Bend DO-219 Plastic Surface Mount Family Outline Plastic Surface Mount Flat DO-7 (Archived) see DO-204-AA Round Body Axial Lead Axial Lead, Round Body DO-13 (Archived) see DO-202-AA (Also Archived) Round Body Axial Lead Axial Lead, Round Body DO-15 (Archived) see DO-204-AC Round Body Axial Lead Axial Lead, Round Body DO-29 (Archived) see DO-204-AF Round Body Axial -

FPGA Evaluation

JPL Publication 92-22 Field Programmable Gate Arrays: Evaluation Report for Space-Flight Application Mike Sandor Mike Davarpanah Kamal Soliman Steven Suszko Susan Mackey September 15, 1992 I IA$A National Aeronautics and Space Administration Jet Propulsion Laboratory California Institute of Technology Pasadena, California The research described in this publication was carried out by the Jet Propulsion Laboratory (California Institute of Technology), Aerospace Corporation, Actel Corporation, Applied Physics Laboratory, GE Astro Space, Hughes Aircraft, TRW, Magnavox Electronics Systems Company, and the National Aeronautics and Space Administration. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States Government or the sponsors named above. SPECIAL ACKNOWLEDGEMENT The content of this report was provided by the foUowing organizations: JET PROPULSION LABORA TORY AEROSPACE CORPORA TION A CTEL CORPORATION APPLIED PHYSICS LABORATORY GE ASTRO SPACE HUGHES AIRCRAFT TRW MA GNA VOX ELECTRONICS SYSTEMS COMPANY This publication was prepared by the Jet Propulsion Laboratory, California Institute of Technology under agreement with the aforesaid consortium members and others whose work contributed to the overall FPGA evaluation. It is distributed for information purposes only. o°° ili FPGA REPORT ABSTRACT Field Programmable Gate Arrays commonly called FPGA's are the newer generation of field programmable devices and offer more flexibility in the logic modules they incorporate and in how they are interconnected. The flexibility, the number of logic building blocks available, and the high gate densities achievable are why users find FPGA's attractive. These attributes are important in reducing product devdopment costs and shortening the development cycle. -

Intel-Packaging-Databook.Pdf

Introduction 1 1.1 Overview Of Intel Packaging Technology As semiconductor devices become significantly more complex, electronics designers are challenged to fully harness their computing power. Transistor count in products is expected to exceed 100 million. With a greater number of functions integrated on a die or chip of silicon, manufacturers and users face new and increasingly challenging electrical interconnect issues. To tap the power of the die efficiently, each level of electrical interconnect from the die to the functional hardware or equipment must also keep pace with these revolutionary devices. Package design has a major impact on device performance and functionality. Today, submicron feature size at the die level is driving package feature size down to the design- rule level of the early silicon transistors. At the same time, electronic equipment designers are shrinking their products, increasing complexity, setting higher expectations for performance, and focusing strongly on reducing cost. To meet these demands, package technology must deliver higher lead counts, reduced pitch, reduced footprint area, provide overall volume reduction, aid in system partitioning, and be cost effective. Circuit performance is only as good as the weakest link. Therefore, a significant challenge for packaging is to insure it does not gate device performance. While packaging cannot add to the theoretical performance of the device design, it can have adverse effects if not optimized. Package performance, therefore, is the best compromise of electrical, thermal, and mechanical attributes, as well as the form factor or physical outline, to meet product specific applications, reliability and cost objectives. The continuing demand for higher performance products is requiring levels of package performance unattainable by the molded plastic and ceramic packages of the past decade. -

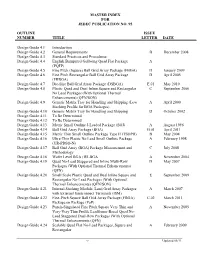

Master Index for Jedec Publication No

MASTER INDEX FOR JEDEC PUBLICATION NO. 95 OUTLINE ISSUE NUMBER TITLE LETTER DATE Design Guide 4.1 Introduction Design Guide 4.2 General Requirements B December 2008 Design Guide 4.3 Standard Practices and Procedures Design Guide 4.4 English Bumpered Gullwing Quad Flat Package A (PQFP) Design Guide 4.5 Fine Pitch (Square) Ball Grid Array Package (FBGA) H January 2009 Design Guide 4.6 Fine Pitch Rectangular Ball Grid Array Package D April 2005 (FRBGA) Design Guide 4.7 Die-Size Ball Grid Array Package (DSBGA) E.01 May 2010 Design Guide 4.8 Plastic Quad and Dual Inline Square and Rectangular C September 2006 No Lead Packages (With Optional Thermal Enhancements) (QFN/SON) Design Guide 4.9 Generic Matrix Tray for Handling and Shipping (Low A April 2000 Stacking Profile for BGA Packages) Design Guide 4.10 Generic Matrix Tray for Handling and Shipping D October 2002 Design Guide 4.11 To Be Determined Design Guide 4.12 To Be Determined Design Guide 4.13 Metric Small Outline J-Leaded Package (SOJ) A August 1996 Design Guide 4.14 Ball Grid Array Package (BGA) G.01 April 2011 Design Guide 4.15 Metric Thin Small Outline Package Type II (TSOPII) B May 2004 Design Guide 4.16 Ultra-Thin Plastic No Lead Small Outline Package A February 1998 (UR-PDSO-N) Design Guide 4.17 Ball Grid Array (BGA) Package Measurement and C July 2008 Methodology Design Guide 4.18 Wafer Level BGA (WLBGA A November 2004 Design Guide 4.19 Quad No-Lead Staggered and Inline Multi-Row D May 2007 Packages (With Optional Thermal Enhancements) (QFN) Design Guide 4.20 Small Scale Plastic -

Ordering Information

Nomenclature Guide Intersil Nomenclatures ISL Types ISL X XXXX X I XX X XXX Z -T PREFIX SUFFIX/ POST PROCESSING/ PB-FREE OPTION SPECIAL SERVICES Z: ROHS and IEC61249-2-21 Halogen Free -T: Tape and Reel FAMILY DESIGNATOR SPECIAL SELECTIONS -T1: Tape and Reel 1: DSL, RTC, Clocks, ATE, -T2: Tape and Reel Optional Characters to Denote Operating Conditions or Energy LED Lighting w/Vacuum Pack Package Options: 2: Reference, DCPs, Buffers, -T7: 7” Reel 18: 1.8V Sensors, Precision Op Amp, -TS: 7” Reel, 100 pc. 33: 3.3V Precision ADC & DAC -T7A: 7” Reel, 250pc. EP: Enhanced Product 3: Interface, Data Communication -T13: 13” Reel (DSCC Vendor Item Drawing) 4: Analog Component Solutions -T5: 500pc Tape and Reel EPZ: Enhanced Product w/100% Matte Tin Lead Finish 5: High Speed Amps, Switch/MUX, -TK: 1,000pc Tape and Reel -T5K: 5,000pc Tape and Reel ADCs, DACs, Optical, Video, OPTIONAL ELECTRICAL GRADE -EV: Evaluation Board Telecom VoIP, DSP Function To Denote Speed or Precision Grading as Defined in Datasheet -EVZ: Evaluation Board Specific ROHS Compliant 6: Desktop Power PACKAGE DESIGNATOR -DM: Demo Board 7: Space, Auto A: Shrink Small Outline Plastic (SSOP/QSOP) -DMZ: Demo Board ROHS 8: Analog Switches, General B: Small Outline Plastic (SOIC) Compliant Purpose Power BE: Exposed Pad SOIC (EPSOIC) -RF: Ref Design Eval Board 9: Notebook, Handheld C: Available -RFZ: Ref Design Eval Board A: High Speed ADCs D: Ceramic Dual-In-Line Metal Seal (SBDIP) ROHS Compliant E: Small Outline Transistor Plastic (SC-70) -EC: Enhanced Commercial F: Ceramic Flatpack -

Smt Glossary

SMT GLOSSARY Alloy. Two or more metals combined to create a metal with different physical characteristics. Ball Grid Array. A grid array using solder balls rather than leads. Butt Joint. A solder joint where just the end of the lead touches the solder pad. Capillary Action. Surface tension that draws a liquid into a small opening. Chip Carrier. A low profile package with leads that hold the chip die. Contact. The conducting area where a lead touches a pad or connector. Convection. Heat transfer by hot air. Coplanarity. The surface mount lead positioning in reference to the parallel card surface. Dewetting. The effect of solder withdrawing from a presoldered lead. DIP. Dual In-Line package, a package with leads in two parallel rows. DPAK. Small power transistor package. Drawbridge (Tombstone). A solder "open" caused by a two legged component standing on end during soldering. Electroplating. A method of depositing metal coating onto another metal. Eutectic. Common solder alloy with low melting point. (63% Tin / 37%Lead) Fillet. The junction where to surfaces meet, as in solder fillet. Flatpack. A flat surface mount package with flat or gull-wing leads on two or four sides. Footprint. The pcb foil pattern to which a surface mount component is attached. Also pad or land. Glass Transition Temperature. The temperature at which a hard substance becomes soft. Gull Wing. A surface mount lead that is formed outward from a package parallel to the pcb solder pad. IR Shadowing. Non-uniform heating caused by objects blocking infrared energy. IR Reflow. A solder process using infrared light.