KV4X Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

June 18 Newsletter

ESSEX EGYPTOLOGY GROUP Newsletter 114 June/July 2018 DATES FOR YOUR DIARY 3rd June The Tomb of Tatia at Saqqara: Vincent Oeters 1st July Papyrus Berlin P10480-82: a Middle Kingdom mortuary ritual reflected in writing: Dr Ilona Regulski 5th August Flies, lions and oysters: military awards or tea for two: Taneash Sidpura Annual General Meeting 2nd September Egypt’s Origins: the view from Mesopotamia and Iran: Dr Paul Collins This month we welcome back Vincent Oeters from Holland. During the 2009 field season of the joint mission of the Rijksmuseum van Oudheden (National Museum of Antiquities) at Leiden, the Netherlands and Leiden University (Faculty of Humanities, Department of Egyptology) a small Ramesside tomb-chapel was unearthed in the New Kingdom necropolis at Saqqara (1550-1070 BC), south of the causeway of Unas. The tomb-chapel belonged to a man named Tatia, Priest of the front of Ptah and Chief of the Goldsmiths. By studying the reliefs as well as the architecture and by comparing the tomb with other Ramesside tombs at Saqqara and elsewhere, an attempt was made to establish a more precise dating of the monument. Recent research has resulted in new insights on Tatia and his career, signs of private devotion and familial relationships. It appears Tatia was a relative of two other well-known New Kingdom officials, one whose important tomb was also built at Saqqara, the other a vizier and 'High Priest of Amun' in Thebes. In July we welcome, Ilona Regulski, the curator responsible for the papyrus collection and other inscribed material in the collection at the British Museum. -

Needle Roller and Cage Assemblies B-003〜022

*保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 1 Needle roller and cage assemblies B-003〜022 Needle roller and cage assemblies for connecting rod bearings B-023〜030 Drawn cup needle roller bearings B-031〜054 Machined-ring needle roller bearings B-055〜102 Needle Roller Bearings Machined-ring needle roller bearings, B-103〜120 BEARING TABLES separable Self-aligning needle roller bearings B-121〜126 Inner rings B-127〜144 Clearance-adjustable needle roller bearings B-145〜150 Complex bearings B-151〜172 Cam followers B-173〜217 Roller followers B-218〜240 Thrust roller bearings B-241〜260 Components Needle rollers / Snap rings / Seals B-261〜274 Linear bearings B-275〜294 One-way clutches B-295〜299 Bottom roller bearings for textile machinery Tension pulleys for textile machinery B-300〜308 *保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 2 B-2 *保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 3 Needle Roller and Cage Assemblies *保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 4 Needle roller and cage assemblies NTN Needle Roller and Cage Assemblies This needle roller and cage assembly is one of the or a housing as the direct raceway surface, without using basic components for the needle roller bearing of a inner ring and outer ring. construction wherein the needle rollers are fitted with a The needle rollers are guided by the cage more cage so as not to separate from each other. The use of precisely than the full complement roller type, hence this roller and cage assembly enables to design a enabling high speed running of bearing. -

Emission Station List by County for the Web

Emission Station List By County for the Web Run Date: June 20, 2018 Run Time: 7:24:12 AM Type of test performed OIS County Station Status Station Name Station Address Phone Number Number OBD Tailpipe Visual Dynamometer ADAMS Active 194 Imports Inc B067 680 HANOVER PIKE , LITTLESTOWN PA 17340 717-359-7752 X ADAMS Active Bankerts Auto Service L311 3001 HANOVER PIKE , HANOVER PA 17331 717-632-8464 X ADAMS Active Bankert'S Garage DB27 168 FERN DRIVE , NEW OXFORD PA 17350 717-624-0420 X ADAMS Active Bell'S Auto Repair Llc DN71 2825 CARLISLE PIKE , NEW OXFORD PA 17350 717-624-4752 X ADAMS Active Biglerville Tire & Auto 5260 301 E YORK ST , BIGLERVILLE PA 17307 -- ADAMS Active Chohany Auto Repr. Sales & Svc EJ73 2782 CARLISLE PIKE , NEW OXFORD PA 17350 717-479-5589 X 1489 CRANBERRY RD. , YORK SPRINGS PA ADAMS Active Clines Auto Worx Llc EQ02 717-321-4929 X 17372 611 MAIN STREET REAR , MCSHERRYSTOWN ADAMS Active Dodd'S Garage K149 717-637-1072 X PA 17344 ADAMS Active Gene Latta Ford Inc A809 1565 CARLISLE PIKE , HANOVER PA 17331 717-633-1999 X ADAMS Active Greg'S Auto And Truck Repair X994 1935 E BERLIN ROAD , NEW OXFORD PA 17350 717-624-2926 X ADAMS Active Hanover Nissan EG08 75 W EISENHOWER DR , HANOVER PA 17331 717-637-1121 X ADAMS Active Hanover Toyota X536 RT 94-1830 CARLISLE PK , HANOVER PA 17331 717-633-1818 X ADAMS Active Lawrence Motors Inc N318 1726 CARLISLE PIKE , HANOVER PA 17331 717-637-6664 X 630 HOOVER SCHOOL RD , EAST BERLIN PA ADAMS Active Leas Garage 6722 717-259-0311 X 17316-9571 586 W KING STREET , ABBOTTSTOWN PA ADAMS Active -

Il Cristianesimo in Egitto Luci E Ombre in Abydos La Tomba

egittologia.net magazine in questo numero: IL CRISTIANESIMO IN EGITTO EGITTO A VENEZIA LUCI E OMBRE IN ABYDOS SPECIALE NEFERTARI LA TOMBA QV66 AREA ARCHEOLOGICA TEBANA IL VILLAGGIO DI DEIR EL-MEDINA EGITTO IN PILLOLE ISCRIZIONI IERATICHE NELLA TOMBA DI THUTMOSI IV Italiani in Egitto: Ernesto Schiaparelli | L’Arte di Shamira | I papiri di Carla BOLLETTINO INFORMATIVO DELL'ASSOCIAZIONE EGITTOLOGIA.NET NUMERO 3 e d i t o r i a l e La prolungata e precoce presenza di questo Confesso che questo numero di EM – Egitto- insolito e intenso caldo, dà l’impressione che logia.net Magazine è stato sul punto di non l’estate stia già volgendo al termine, anche se uscire! La prossimità con il ferragosto e il in realtà la legna accumulata per l’inverno caldo scoraggiante, soprattutto nelle due set- dovrà aspettare ancora molto tempo prima di timane centrali del mese di luglio – periodo in essere utile. cui il terzo numero del magazine ha comin- Curioso come hanno deciso di chiamare le tre ciato a prendere vita – ci avevano fatto propen- fasi più intense del caldo i meteorologici: Sci- dere per una sospensione, procrastinandone pione, Caronte e Minosse. Curioso perché mi l’uscita direttamente a ottobre. vien da pensare che l’epiteto “Africano” di Sci- Ma abbiamo resistito alla tentazione, sospen- pione e il collegamento con l’Ade che è possi- dendo solo una parte dei temi che abbiamo bile fare con Caronte e Minosse, abbia cominciato a trattare nei numeri precedenti, richiamato alla mente degli scienziati il con- come ci è stato richiesto dagli autori degli cetto di “caldo”. -

Minnowenvironmental Inc

--~------- minnowenvironmental inc. _____ 2 Lamb Street Georgetown, Ontario L7G 3M9 Memorandum To: Dan Cornett, Access Consulting Group From: Cynthia Russel, Minnow Environmental Inc. Date: February 13, 2008-02-13 Re: Update of Surface Water Quality Assessment for United Keno Hill Mine Complex. Minnow Environmental Inc. (Minnow) was retained by Access Consulting Group to undertake an assessment of the existing water quality data for the United Keno Hill Mine Complex (United Keno, Galena and Sourdough Hill). The objective of this assessment was to identify parameters and locations of concern within the downstream waters relative to established guidelines and background. This information, combined with toxicity data and watershed use objectives may then be combined to develop an approach for considering the development of Site Specific Water Quality Objectives (SSWQO) for various parameters and locations. In order to meet the study objectives, a progressive assessment of the available water quality data was undertaken which included the following steps; • Screen all data to identify outliers (i.e., those greater then 3 standard deviations from the mean) and remove these data. • Establish the background concentration for each parameter based the upper limit of background data distribution (mean + t S.D.) for the combined data from KV-1 and KV-37. UKH Surface Water Quality Assessment - Progress Report • Identify parameters with high method detection limits relative to guidelines which preclude determination of whether concentrations exceed the guideline. • Identify background concentrations which exceed the Canadian Water Quality Guidelines (CWQG). • Determine the median, mean, minimum and maximum concentration for each parameter at each location. • Determine which locations exceed background and/or CWQG at measurable (10%) and substantial (50%) frequencies. -

DSFRA IKEN Report Template

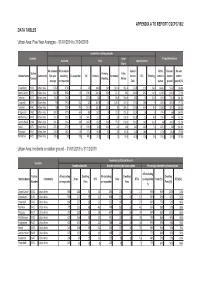

APPENDIX A TO REPORT CSCPC/19/2 DATA TABLES Urban Area: Five-Year Averages – 01/04/2014 to 31/04/2019 Incidents on station grounds Location False Pump Attendances Overview Fires Special Service Alarm All incidents All incidents Special All by On own On own Station Primary: False Station Name Community five-year excluding Co-responder All Primary Secondary Service RTC Flooding station's station station Number Dwelling Alarms average co-responder Calls pumps ground ground (%) Greenbank KV50 Urban Area 878.6 878.6 0 245 104.6 56.6 140.4 361.4 271.8 21.6 24.6 1424.8 974.2 68.4% Danes Castle KV32 Urban Area 832.6 830.8 1.8 198.8 126.4 56.6 72.4 385 248.4 29.2 14.8 1090.6 849.4 77.9% Torquay KV17 Urban Area 744.8 744.8 0 207.8 111 59 96.8 306.8 230 36 15.8 919.8 776.4 84.4% Crownhill KV49 Urban Area 742 741.8 0.2 227 100.6 43 126.4 337.4 177.4 28.6 9 878.4 680.6 77.5% Taunton KV61 Urban Area 734 733.4 0.6 227.8 132.8 56.6 95 284.6 221.6 65.4 8.4 1038.8 901.8 86.8% Bridgwater KV62 Urban Area 584.2 577.6 6.6 160 88.2 38 71.8 231.8 192.4 56 8 774.4 666 86.0% Middlemoor KV59 Urban Area 537.6 535.8 1.8 144.2 91.2 33 53 239.6 153.8 51 8.8 724.4 444 61.3% Camels Head KV48 Urban Area 491.6 491.2 0.4 162.8 85.2 50.4 77.6 178.6 150.2 16.6 11.8 638 390.2 61.2% Yeovil KV73 Urban Area 471.6 471.6 0 139.6 78.6 34.8 61 191 141 46.8 7.4 674.2 569 84.4% Plympton KV47 Urban Area 218.4 204.4 14 57.8 34.8 12 23 87.8 72.4 18.6 3 170.6 135.8 79.6% Plymstock KV51 Urban Area 185.8 185 0.8 48.4 27.4 12 21 76.8 60.6 12.6 2.6 165.4 123.8 74.8% Urban Area: Incidents on -

ABSTRACT Carl Nicholas Reeves STUDIES in the ARCHAEOLOGY

ABSTRACT Carl Nicholas Reeves STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies This study considers the physical evidence for tomb robbery on the Theban west bank, and its resultant effects, during the New Kingdom and Third Intermediate Period. Each tomb and deposit known from the Valley of the Kings is examined in detail, with the aims of establishing the archaeological context of each find and, wherever possible, isolating and comparing the evidence for post-interment activity. The archaeological and documentary evidence pertaining to the royal caches from Deir el-Bahri, the tomb of Amenophis II and elsewhere is drawn together, and from an analysis of this material it is possible to suggest the routes by which the mummies arrived at their final destinations. Large-scale tomb robbery is shown to have been a relatively uncommon phenomenon, confined to periods of political and economic instability. The caching of the royal mummies may be seen as a direct consequence of the tomb robberies of the late New Kingdom and the subsequent abandonment of the necropolis by Ramesses XI. Associated with the evacuation of the Valley tombs may be discerned an official dismantling of the burials and a re-absorption into the economy of the precious commodities there interred. STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies (Volumes I—II) Volume I: Text by Carl Nicholas Reeves Thesis submitted for the degree of Doctor of Philosophy School of Oriental Studies University of Durham 1984 The copyright of this thesis rests with the author. -

NCE Kids Winter at a Glance

newton community education WINTER 2019 newtoncommunityed.org • 617-559-6999 Baking Outside the Box 2 Family & Saturday On the cover: Marissa Rosenfield, Instructor Our cover’s Programs Bake and decorate a unique gift for some- delightful one special—maybe even yourself! Learn to painting was done NEW make cookie pops, edible cards, and choco- in our Modern Adult/Child Yoga late and/or sugar-cookie boxes in the shape Art Adventure of your choice. Later, you can fill the cookie class, in which Ben Cohen, Instructor box with your own homemade truffles, kids create art Experience the joy of yoga as an adult-child marshmallows, or more cookies (our Pastry inspired by artists from the late 18th- pair. You’ll do poses side by side, and also to- Chef instructor has abundant ideas for cook- early 20th centuries. This painting was gether with your partner. We’ll enjoy imag- ie box fillings and uses). Each pair will go inspired by Spanish surrealist Joan inary family yoga adventures to the beach home with their pops, a card, a decorated Miró, who was known for painting or an African safari, with creative exercises, cookie box, and raw dough to practice your whimsical shapes and forms in bold stories, and occasional music to accompany own creations at home. If time allows, we colors. We confess we don’t know the our journey. You’ll participate in partner will make our own truffles too. Grades 2 & identity of our cover artist; if it’s you, massage, and play fun games like yogi’s trees up with an adult. -

Standard Software Driver for C90TFS/Ftfx Flash User's Manual

Standard Software Driver for C90TFS/FTFx Flash User’s Manual © Copyright Freescale Semiconductor 2010-2014. All Rights Reserved REVISION LIST Version Date Author Description No. 1.0 06-07-2010 FPT Team Initial Version 1.1 09-22-2010 FPT Team Update for the FTFx_KX_256K_256K_4K_2K_2K derivative 1.2 09-30-2010 FPT Team Update performance result for the FTFx_KX_256K_256K_4K_2K_2K derivative 1.3 02-24-2011 FPT Team Update for the FTFx_KX_512K_0K_0K_2K_0K derivative 1.4 03-16-2011 FPT Team Update for the FTFx_JX_128K_32K_2K_1K_1K derivative 1.5 05-05-2011 FPT Team Update for the FTFx_FX_256K_32K_2K _1K_1K derivative Update callback time for FTFx_JX_128K_32K_2K_1K_1K 1.6 10-31-2011 FPT Team Update for the FTFx_KX_512K_512K_16K_4K_4K 1.7 11-17-2011 FPT Team Update for the FTFx_KX_1024K_0K_16K_4K_0K 1.8 12-27-2011 FPT Team Update list of derivative in table 7. Add comment for FlashReadResource() function. 1.9 02-21-2012 FPT Team Update to support more Kinetis derivatives. Update PFlashSwap() function prototype. Add performance/code size for FTFx_KX_128K_32K_2K_1K_1K derivative (K20). 2.0 06-12-2012 FPT Team Update to support FTFx_NX_256K_32K_2K_2K_1K FTFx_NX_128K_32K_2K_2K_1K FTFx_NX_96K_32K_2K_2K_1K FTFx_NX_64K_32K_2K_2K_1K derivatives. Update FlashProgramOnce() and FlashReadInce() function prototypes. Add performance/code size for FTFx_NX_256K_32K_2K_2K_1K derivative (Nevis2). 2.1 07-25-2012 FPT Team Update to support derivatives: FTFx_LX_128K_0K_0K_1K_0K FTFx_LX_64K_0K_0K_1K_0K FTFx_LX_32K_0K_0K_1K_0K FTFx_LX_16K_0K_0K_1K_0K FTFx_LX_8K_0K_0K_1K_0K Add performance/code size for FTFx_LX_128K_0K_0K_1K_0K (L2K) and FTFx_LX_32K_0K_0K_1K_0K (L1PT) 2.2 08-23-2012 FPT Team Update to support derivatives: FTFx_AX_64K_0K_0K_1K_0K FTFx_AX_48K_0K_0K_1K_0K FTFx_AX_32K_0K_0K_1K_0K FTFx_AX_16K_0K_0K_1K_0K Recollect performance data for FTFx_LX_128K_0K_0K_1K_0K (L2K), FTFx_LX_32K_0K_0K_1K_0K (L1PT), and FTFx_AX_64K_0K_0K_1K_0K (MC56F82748) 3.0 05-28-2013 FPT Team - Customize the content of document by removing unnecessary sections. -

The New Kingdom Theban Royal Necropolis, Better Known As The

Copyright © 2021 Michael J. Marfleet Published June 18th, 2021 The New Kingdom Theban royal necropolis, better known as the Valley of the Kings, is in fact two convergent valleys - the West Valley (XVIIIth Dynasty tombs only) and the Valley of the Kings proper (XVIIIth through XXth Dynasty tombs) - situated in the Theban Hills on the West Bank of the River Nile, opposite the modern city of Luxor. I. A brief introduction to the Valley(s) of the Kings c1570 to c1070bc by MICHAEL J MARFLEET The West Valley and the Valley of the Kings have been carved out by eons of sporadic torrential rains and runoff from the surrounding ridges and the pyramidal peak of el- Qurn, (see above). To date the two valleys have yielded eighty-five 'tombs'*. Sixty-five of these are numerically numbered, the remaining twenty alphabetically. Of the numerical 'tombs', KV1 through KV21, KV26 through KV40 and KV42 through KV64 lie in the Valley of the Kings (VoK) proper. KV22 through KV25 and KV65** lie in the West Valley, (Essay II appearing July 2nd). KV41, an incomplete pit/shaft 'tomb', lies outside the perimeter of the VoK on the outside of the topographical ridge that encloses the valley and forms part of the so-called 'gateway' to the VoK, (Figs. 1 & 2). Not all are true tombs. Of the eighty-five, twenty-four are known king tombs with twenty-six confirmed pharaoh 'owner/occupiers'. An additional four are not definitively associated with any king 'owner/occupier' but could be considered king tombs - KV19; KV25; KV33; & KV39. -

Supplemental Data FLO1 Is a Variable Green Beard Gene That Drives

Cell, Volume 135 Supplemental Data FLO1 Is a Variable Green Beard Gene that Drives Biofilm-like Cooperation in Budding Yeast Scott Smukalla, Marina Caldara, Nathalie Pochet, Anne Beauvais, Stephanie Guadagnini, Chen Yan, Marcelo D. Vinces, An Jansen, Marie Christine Prevost, Jean-Paul Latgé, Gerald R. Fink, Kevin R. Foster, and Kevin J. Verstrepen 1 Figure S1. Flocculent cultures are resistant to extremely high concentrations of amphotericin B. Flocculent (FLO1, KV210) and non-flocculent (flo1, KV22) cells were subjected to increasing concentrations of amphotericin B for 4 hours, after which the percentage of surviving cells was determined. Asterisks indicate statistical differences between the flocculating and non-flocculating cultures (α = 0.05). Error bars represent standard deviation. 2 3 Figure S2. Flocculating and non-flocculating cells show differential expression of several gene sets. Gene Ontology (GO) gene sets describing biological processes and cellular components (rows) that differ significantly between flocculating and non- flocculating experiments are shown. The gene sets are grouped according to higher-order categories. For each gene set, the median expression of the leading-edge genes in each experiment from the two conditions is shown (columns). Furthermore, each gene set was normalized by mean centering and unit scaling prior to visualization. Red and blue respectively represent induction and repression as compared to average across all experiments. 4 Figure S3. Deletion of genes that are upregulated in flocculating cultures does not affect resistance to amphotericin B. We constructed ten mutant strains of the flocculent (FLO1+) strain KV210. Each of these mutant strains lacks a functional copy of one gene that is upregulated in flocculating cultures (see our gene array analyses). -

Series 8750Xd Unitized Curtain Wall

SERIES 8750XD UNITIZED CURTAIN WALL Installation Instructions Sections 1-15 Jan 2015 PART NO. Y80B 1000 COUNTY ROAD MONETT, MO 65708 • 800.221.4169 • EFCOCORP.COM Series 8750XD Unitized Curtain Wall Installation Instructions Table Of Contents SECTION PAGES 1. General Notes and Guidelines……………………………………………………………………………………………………………………………… 3 - 4 2. Parts Identification……………………………………………………………………………………………………………………………………………. 5 - 11 3. Static Starter Sill Preparation and Installation……………………………..……………………………………………………………………………. 12 - 18 4. Dynamic Starter Sill Preparation and Installation…………………..………………..…………………………………………………………………. 19 - 22 5. Intermediate Floor Slab Anchor Installation……………………………………….....…………………………………………………………………. 23 - 24 6. Unit Inspection and Preparation for Installation……………………………..….......…………………………………………………………………. 25 - 27 7. Setting Units at Static Starter Sills………………………………………………..…....…………………………………………………………………. 28 - 30 8. Setting Units at Dynamic Starter Sills………………………………………………….…………………………………………………………………. 31 - 32 9. Applying Critical Seals and Stack Gaskets……………………………………...………………………………………………………………………. 33 10. Setting Typical intermediate Units….......................................................................…………………………………………………………………. 34 - 35 11. Setting Typical Head Condition Units………………………………………………….…………………………………………………………………. 36 12. Setting Typical 90 Degree Corner Units……………………………………………….…………………………………………………………………. 37 13. Appling Typical Perimeter Seals………………………………………………………..…………………………………………………………………. 38 14. Deglaze /