MNT VA2000, an Amiga 2000 Graphics Card (Zorro II) How I

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Minimig Op Een Chameleon in Een Eerdere Uitgave Hebben We Gesproken Over Viva Amiga De Tobiflexx Heeft De Minimig Core Geschikt Gemaakt Documentaire

C o m m o d o r e I n f o B u l l e t i n J u n i 2 0 1 1 Spreekwoordelijk Keep the Retro Alive... Voorwoord... Van de Voorzitter Moesson Het gaat goed met de Commodore. Dit is een zin die je na 1994 niet meer Het is inmiddels alweer eind mei en we hebben verwacht had nietwaar? De laatste jaren sluimerde de liefde binnen een er al een kleine zomer opzitten. Volgens de groep erg fanatieke hardcore gebruikers, een echte hechte familie. weerkundigen krijgen we in juli en/of augustus een soort moesson dus de aanschaf van een rubberbootje bij de speelgoedwinkel is Het mooie van deze familie was (en is) dat iedereen daarin zonder problemen waarschijnlijk geen sinecure. Hopelijk is het niet wordt opgenomen en geaccepteerd. Iedereen is altijd welkom op onze clubdagen het begin van de nieuwe zondvloed maar ja, en brengt iemand defecte hardware mee, is er altijd wel een clublid die met raad en misschien hebben deze zogenaamde kenners daad terzijde wil staan. We zien onze clubdagen groeien en de gezelligheid stijgen. wel ongelijk. Ook de ontwikkelingen gaan naar ons gevoel opeens snel. Het gerucht van Wij hebben in juni en augustus onze zomer Commodore USA, om te beginnen, is werkelijkheid gebleken. Er komen een paar clubdagen op het programma staan en ook al ligt mooie computers in retro verpakking op de markt. Er zijn hierin tegenstanders die er een meter sneeuw we verwachten weer een hoop drukte. De loop zit er de laatste tijd namelijk roepen dat dit een goedkope marketing truc is, maar de vraag blijkt enorm. -

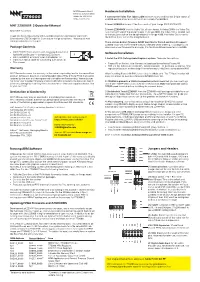

MNT ZZ9000 R 2 Quicksta T Manual Package Contents Wa Ranty

MNT Research GmbH Hardware Installation Fehlerstr. 8, 12161 Berlin WEEE DE 33315564 1. Connect the Video Slot ibbon cable by inseting one end into the 34 pin socket https://mntre.com of ZZ9000 and the other end into the 34 pin socket of ZZ9000CX. MNT ZZ9000 R2 Quickstat Manual 2. Inset ZZ9000 into any of the Zoro slots of your Amiga 2000/3000/4000. 3. Inset ZZ9000CX into the Video Slot of your Amiga. In Amiga 2000, the Video Dear MNT Customer, Slot is on the ight side of the power supply. In Amiga 3000, the Video Slot is located next to the top Zoro slot on the daugtherboard. In Amiga 4000, the Video Thank you for purchasing the MNT ZZ9000 Graphics Coprocessor Card (with Slot is next to the bottom Zoro slot on the daughterboard. Ethenet and USB Storage) for Commodore Amiga computers. This product was made possible by your suppot. There are two distinct fimware BOOT.bin) files for Zoro II and Zoro III suppot. ZZ9000 ships with the fimware that you selected when ordeing. To change it, just Package Contents download a new fimware file and copy it to the MicroSD card inseted in ZZ9000. • MNT ZZ9000 Zoro card 1 with mounting bracket and Software Installation 128MB MicroSD card 4 containing ZZ9000OS • MNT ZZ9000CX ECS/AGA Video Slot adapter 2 1. Install the RTG ReTargetable Graphics) system. There are two options: • Video Slot ibbon cable for connecting both cards 3 • This manual • Picasso96 on Aminet: http://aminet.net/package/diver/video/Picasso96 • P96 2.x by Individual Computers (recommended). -

News Features Reviews Support

CONTENTS CONTENTS Contents Letter from the Editor The Chairman Speaks elcome to the second issue espite my last attempt at writing of Clubbed and an especially an article for Clubbed magazine NEWS W warm welcome to all the new Dhere I am again. subscribers and members who have UPDATE SEAL Update.....................3 come along since the first issue. Also In this months issue of Clubbed I am since the last issue we’ve received lots trying to convey the message that Members Amiga Inc. Update .............7 of positive comments and constructive upgrading your Amiga lets you get much suggestions for the magazine. Please more from it, and can also be done rela- Since the last mag Mick Sutton has got keep sending in your ideas so we can tively economically. himself an Internet account so you can make Clubbed a monster-mag! now EMail him at [email protected]. FEATURES If you have an older machine like an Also a warm welcome to all the Dave Haynie Interview.......8 Just before this issue went to press we A500 the best route is often to upgrade members who have joined since the last made an arrangement with two Amiga to an A1200 as they are much easier issue! Fleecy Moss Interview .....10 software distributors (Underground PD and cheaper to expand, and therefore a and Forematt Home Computing), for better base to build upon. For example, Web Site Gary Peake Interview .......... 11 them to distribute Clubbed flyers with More Product Information - With every it is often cheaper to buy an A1200 and Microsoft ..........................12 the packages they send out. -

ZZ9000 R-3 Manual and Schematics

MNT Research GmbH Hardware Installation Fehlerstr. 8, 12161 Berlin WEEE DE 33315564 1. Connect the Video Slot ��ibbon cable by inseting one end into the 34 pin socket of https://mntre.com ZZ9000 and the other end into the 34 pin socket of ZZ9000CX. MNT ZZ9000 R��3 Quicksta9t Manual 2. Inset ZZ9000 into any of the Zoro slots of your Amiga 2000/3000/4000. 3. Inset ZZ9000CX into the Video Slot of your Amiga. In Amiga 2000, the Video Slot Dear MNT Customer, is on the ight side of the power supply. In Amiga 3000, the Video Slot is located next to the top Zoro slot on the daugtherboard. In Amiga 4000, the Video Slot is next to Thank you for purchasing the MNT ZZ9000 Graphics Coprocessor Card (with the bottom Zoro slot on the daughterboard. Ethe��net and USB Storage) for Commodore Amiga computers. This product was made possible by your suppot. There are two distinct fimware 9BOOT.bin) files for Zoro II and Zoro III suppot. ZZ9000 ships with the fimware that you selected when ordeing. To change it, just Package Contents download a new fimware file and copy it to the MicroSD card inseted in ZZ9000. • MNT ZZ9000 Zoro card 1 with mounting bracket and Software Installation 128MB MicroSD card 4 containing ZZ9000OS • MNT ZZ9000CX ECS/AGA Video Slot adapter 2 1. Install the RTG 9ReTargetable Graphics) system. There are two options: • Video Slot ibbon cable for connecting both cards 3 • This manual • Picasso96 on Aminet: http://aminet.net/package/diver/video/Picasso96 • P96 2.x by Individual Computers (recommended). -

Toaster Toolkit 4000 (Devware)

L/BER4770A/”— BLOCKBUSTER HIT FOR CD327-P.70 mu nicotians i cat ion A m i g a . PC A m ig a See How They Run! ► ANIMATION ► GRAPHICS ►MORPHING ►VIDEO ► MULTIMEDIA ► DTP Plus! • 10 AG A Fixes For Non-AGA Owners 50 I/O Expanders A nimation “Recycling I | i [ I i ! I A udio For V ideo 07447065948804 M ore DOS “G ems” “HotLink” Y our DTP LOW PRICE jpm ai n m e r Release 2 f i n a l ^O pyM l Release 2 f j g r inal Writer is arguably the best word processor "Readers’ Choice Awa^:i#93'\ Amazing yet released tor the Amiga.”, Amiga \ $ g |d ; March Computing; "Awarcy§3 -"feest Software Product", 1994. "...Final Writer is the top Amiga word proces Amiga Plus "Product of the Year 1993",, i sor to rival even the Mac and PC heavyweights.", Amiga Macaflp^iermany). What more can we savJS CU Amiga (England). January 1994. Finalwriter Thisjfr thelmost popular and most used word haskall of Final Copy M s major features plus many . ^ | M B r on the Amiga today. It features a 110.000-; more. Jt includes: Table of Contents, Table of p ir a speller; 1.4 million word thesaurus; autaj| illustrations. Endnotes, Bibliography, and Index gen- hyphenation: search and replace: tab stops; 'eraijion; sections; multiple master pages; E P S adjustable margins; word and sentenc(y»HCljg;-l gsapnic support: movable text blocks; rotated text paragraph sorting; on-screen math; ARexx port; and graphics; and a user configured button strip for style sheets; drawing tools; imported IFF graphics:^ individulTcustorri^tion of the program’s interface. -

Amiga Alternate History, What If MIPS ?

Amiga Alternate History, What If MIPS ? The Amiga computers were always tightly bound the the Motorola M68k range of processors, this eventually became a performance bottleneck, what if that never happened. Amiga 1000 progress meeting, 1985. Much of the custom chips are in final development and testing but over in California MIPS Computer Systems Inc are about to announce their first designs. At the toss of a coin the Amiga hardware team decide to ditch the M68000 from the first design and go with the R2000 processor. This caused considerable delays to both the hardware team, who had to remove the dependencies on M68k bus signals from the OCS chipset and to the operating system team who had to replace chunks of m68k assembler code with C. The delays meant that the Amiga 1000 launched in 1986, the same year as the first MIPS R2000 unix box. The Amiga 1000 specs where: 256k of RAM 8mhz R2000 CPU Kickstart 1.2 in ROM OCS Chipset The Amiga 1000 was like in true life way ahead of its time but sales were slow, supporting a new operating system with new hardware was always going to be difficult. But sales were good enough for Commodore to plan two new designs, a reduced cost games machine and a big box version for professional use. The plans did not provide new chipset features and so resulted in two very similar models, which were; The Amiga 500 512k chip RAM 8mhz R2000 CPU Kickstart 1.3 in ROM OCS Chipset The Amiga 2000 512k chip RAM 15mhz R2000 CPU + R2010 FPU companion Kickstart 1.3 in ROM OCS Chipset Zorro II expansion bus The ‘Big Box’ Amiga 2000 main differentiators where its uprated CPU, which was the maximum R2000 clock frequency, the addition of the FPU companion and the Zorro II expansion slots. -

Morphos Im Detail (V2.6)

MorphOS im Detail (V2.6) Von Ulrich Beckers, Nicholas Blachford © V2.6 Ulrich Beckers, 30. Mai 2013 Die Intention dieses Dokumentes ist, MorphOS zu beschreiben - Wie es dazu kam, wie es funktioniert, wie der gegenwärtige Status ist, und wie die Zukunft aussehen kann. Besonderer Dank geht an das MorphOS-Team, das Ambient- Entwicklerteam und an Genesi für ihre großartige Leistung und Hilfe. Inhalt Inhalt Seite 2 1. Einführung Seite 3 2. Am Anfang: Die Geschichte von MorphOS Seite 4 3. Die Hardware Seite 6 3.1 Pegasos Seite 6 3.2 Efika 5200B Seite 7 3.3 Apple Hardware Seite 7 4. Die Struktur von MorphOS Seite 8 5. Die ABox Seite 9 6. Systemkomponenten der ABox Seite 11 7. QBox - Eine Zukunftsoption von MorphOS Seite 15 8. Weitere Informationen Seite 19 © V2.x 2004 - 2013 Ulrich Beckers, alle Rechte vorbehalten Kontakt & Rückfragen: [email protected] Morphos im Detail 2.6 Seite 2 1. Einführung MorphOS ist ein eigenständiges grafisches Betriebssystem für PowerPC RISC Mikroprozessoren. MorphOS zeichnet sich in erster Linie durch einfache Bedienbarkeit, transparenten und logischen Aufbau des Systems sowie eine sehr hohe Reaktionsgeschwindigkeit bei geringen Hardwareanforderungen aus. Das System ist für Multimediaanwendungen besonders gut geeignet und erfüllt schwache Echtzeitanforderungen. Die unterstützte Hardware zeichnet sich mehrheitlich durch einen vergleichsweise geringen Strombedarf aus. Das Logo von MorphOS ist ein blauer Schmetterling der tropischen Art Morpho menelaus. MorphOS ist am 27. Mai 2013 in Version 3.2 für PowerPC-Computersysteme von Apple Computer Inc. (Modelle Powerbook G4 Aluminium mit ATI Grafik, iBook G4, Mac mini G4, PowerMac G4, PowerMac G5 (PowerMac 7.3) eMac G4 1.25 und 1.42 Ghz ) und von Genesi/bplan (Pegasos 1 & 2, sowie das Kleinstmainboard Efika 5200B) veröffentlicht worden (www.morphos- team.net). -

When I Was Looking for a Guide to Set up an Amiga on My Shiny New Imac, I Scanned the Forums and Googled the Web

When I was looking for a guide to set up an Amiga on my shiny new iMac, I scanned the forums and Googled the web. I didn't find one. This is the reason for this guide; I've actually enjoyed setting up EUAE myself (although it has taken longer) as I have learnt things on the way. For the record I have a 17" iMac G5, 250Gig HD, 1Gig Ram and OSX 10.4.5 I absolutely love this computer, I didn't think I would ever love using a computer as much as my Amiga, back in the day. Although it has to be said that WINUAE is an amazing piece of software, and that the combination of this running on Windows is unbeatable, I could still not bring myself to be restricted to only using Windows at home, as I think I would slowly loose my mind. Mac OSX is just so much better than Windows. Throughout this guide, I will be using Amiga Forever from the guys at Cloanto - this is an excellent packaged software Amiga, with data and configurations that can be used on the Mac. I am assuming some working knowledge of Mac OSX and some knowledge of the Amiga in this guide. I also assume you either have copies of your own Amiga ROMs and games or have purchased Amiga forever. Anyway, lets get the show on the road. First things first, lets get an Amiga to boot and show the boot rom screens. Start by visiting the web-site of Daniel Pimley, here you will find a most useful piece of software. -

Feature List Revision 1.0 January 7, 2003

Feature List Revision 1.0 January 7, 2003 © 2003 Hyperion Entertainment Introduction The following pages provide a more detailed description of the “new” functionality introduced by Amiga OS 4.0. Functionality is considered “new” when it was not present in Amiga OS 3.9 (Boing Bag 2). OS modules which are simply recompiled for PPC (such as Workbench for instance) are not mentioned here. Note that this document should be considered preliminary and the information it contains is still subject to change and refinement. Nothing in this document shall be construed as limiting Hyperion’s right to modify the functionality of AmigaOS 4.0 without prior notice. Further revisions of this document will be made available. This document is © (2003) Hyperion Entertainment. Permission is hereby granted to reproduce the content of this document in whole or in part solely in unmodified form. 3 Exec SG (second generation) Exec SG is the OS 4.x kernel and as such the heart of the system. Inherited functionality from older Exec versions: ExecSG is fully backward compatible to older Exec versions and preserves all of its features including, but not limited to: • Fully pre-emptive multitasking (round-robin) • Support for shared libraries • Very fast inter-process communication (IPC - message passing by reference) • Fast interrupt handling (low latency) • Low-overhead task switching New functionality introduced by ExecSG: • Fully PPC native: not a single 68k instruction left in ExecSG. • 68k emulation: both interpreting and JIT emulation available (see below), JIT for speed, interpreting for compatibility. • Extremely fast context switching times: 1 microsecond on a 600 MHz G3. -

Workbench November98

Amiga Users Group Inc. Workbench November–December 1998 Number 140 or those of you who couldn’t make it to The exibitors included the Melbourne Amiga AmigaFest ’98 at Albert Park, Melbourne Users Group (formally the North Western Amiga Fon Saturday 24 October you didn’t miss Users Group) which set up an internet cafe site much! I don’t want to denigrate the Amiga and right in the building using Amiga 3000’s and it’s supporters but the show (a glorified user 4000’s. You could surf the web using a familiar group meeting actually) was poorly organised interface and computer at the same time. The and a great disappointment from that which service was really fast and the group were was advertised. Now that I have that off my charging $1.00 per hour for the privilege. The chest let’s get on with the show report. group also had a User Group stand set up and The original show which was to be held over were recruiting new members at the meeting. two days only managed a Saturday showing. The venue was one of the corporate boxes above the Grand Prix pit complex at Albert Park. The large room still seemed empty even after all the exhibitors had arrived and set up their displays and wares. Entry was reduced to $5.00 dollars to compensate for the lower quality of the event than that which was advertised. What to buy?: Computa-Magic shows its wares to software starved enthusiasts Computa-Magic had a large stand and had many items for sale including all the latest Amiga titles on CDROM. -

Also in This Issue

Issue 10, Spring 2002 £3.50 Also in this issue: News: WoASE Show Report AmigaOS 4 Update Features: AmiMPC Reviews: Mediator 4000 EZKey XS and Multimedia Keyboard Support: B2B: Mode Promotion Directory Opus Tutorial Contents Contents The Chairman Speaks the show in November, to announced we intended to put Issue 10 Editorial n these frugal times it is hopefully coincide with the on an Amiga show I was as with the old one I expect it Idifficult to gauge just how estimated release of OS4 and quietly concerned after elcome to the first issue will be refined over time, many active Amiga users there AmigaOne (about October). witnessing the Kickstart K4 are, while on a daily basis I show. But we (SEAL, ANT, Spring 2002 Wof Total Amiga! If you’re please let us know if you have The more we thought about view on Amibench whole Kickstart and ASA) decided to an existing Clubbed subscriber any comments or suggestions. putting on a show the more you may just not have heard systems being sold complete go ahead with it and hope for If you’ve read our enthusiasm we built up, and that Total Amiga is the new with high quality original the best. announcements about Total after a meeting between the Contents name for the magazine. We software. That of course Amiga you will know that we two user groups it was decided The main issue was to put on a think it better reflects the range means they are leaving the are aiming to move from we were going to put on a show that was commercially of Amiga subjects we cover behind the scenes section, Amiga for good, not keeping News quarterly to bi-monthly show. -

When I Was Looking for a Guide to Set up an Amiga on My Shiny New Imac, I Scanned the Forums and Googled the Web

When I was looking for a guide to set up an Amiga on my shiny new iMac, I scanned the forums and Googled the web. I didn't find one. This is the reason for this guide; I've actually enjoyed setting up EUAE myself (although it has taken longer) as I have learnt things on the way. For the record I have a 17" iMac G5, 250Gig HD, 1Gig Ram and OSX 10.4.5 I absolutely love this computer, I didn't think I would ever love using a computer as much as my Amiga, back in the day. Although it has to be said that WINUAE is an amazing piece of software, and that the combination of this running on Windows is unbeatable, I could still not bring myself to be restricted to only using Windows at home, as I think I would slowly loose my mind. Mac OSX is just so much better than Windows. Throughout this guide, I will be using Amiga Forever from the guys at Cloanto - this is an excellent packaged software Amiga, with data and configurations that can be used on the Mac. I am assuming some working knowledge of Mac OSX and some knowledge of the Amiga in this guide. I also assume you either have copies of your own Amiga ROMs and games or have purchased Amiga forever. Anyway, lets get the show on the road. First things first, lets get an Amiga to boot and show the boot rom screens. Start by visiting the web-site of Daniel Pimley, here you will find a most useful piece of software.