Nvidia Hardware Documentation Release Git

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

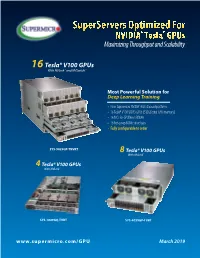

Supermicro GPU Solutions Optimized for NVIDIA Nvlink

SuperServers Optimized For NVIDIA® Tesla® GPUs Maximizing Throughput and Scalability 16 Tesla® V100 GPUs With NVLink™ and NVSwitch™ Most Powerful Solution for Deep Learning Training • New Supermicro NVIDIA® HGX-2 based platform • 16 Tesla® V100 SXM3 GPUs (512GB total GPU memory) • 16 NICs for GPUDirect RDMA • 16 hot-swap NVMe drive bays • Fully configurable to order SYS-9029GP-TNVRT 8 Tesla® V100 GPUs With NVLink™ 4 Tesla® V100 GPUs With NVLink™ SYS-1029GQ-TVRT SYS-4029GP-TVRT www.supermicro.com/GPU March 2019 Maximum Acceleration for AI/DL Training Workloads PERFORMANCE: Highest Parallel peak performance with NVIDIA Tesla V100 GPUs THROUGHPUT: Best in class GPU-to-GPU bandwidth with a maximum speed of 300GB/s SCALABILITY: Designed for direct interconections between multiple GPU nodes FLEXIBILITY: PCI-E 3.0 x16 for low latency I/O expansion capacity & GPU Direct RDMA support DESIGN: Optimized GPU cooling for highest sustained parallel computing performance EFFICIENCY: Redundant Titanium Level power supplies & intelligent cooling control Model SYS-1029GQ-TVRT SYS-4029GP-TVRT • Dual Intel® Xeon® Scalable processors with 3 UPI up to • Dual Intel® Xeon® Scalable processors with 3 UPI up to 10.4GT/s CPU Support 10.4GT/s • Supports up to 205W TDP CPU • Supports up to 205W TDP CPU • 8 NVIDIA® Tesla® V100 GPUs • 4 NVIDIA Tesla V100 GPUs • NVIDIA® NVLink™ GPU Interconnect up to 300GB/s GPU Support • NVIDIA® NVLink™ GPU Interconnect up to 300GB/s • Optimized for GPUDirect RDMA • Optimized for GPUDirect RDMA • Independent CPU and GPU thermal zones -

Gs-35F-4677G

March 2013 NCS Technologies, Inc. Information Technology (IT) Schedule Contract Number: GS-35F-4677G FEDERAL ACQUISTIION SERVICE INFORMATION TECHNOLOGY SCHEDULE PRICELIST GENERAL PURPOSE COMMERCIAL INFORMATION TECHNOLOGY EQUIPMENT Special Item No. 132-8 Purchase of Hardware 132-8 PURCHASE OF EQUIPMENT FSC CLASS 7010 – SYSTEM CONFIGURATION 1. End User Computer / Desktop 2. Professional Workstation 3. Server 4. Laptop / Portable / Notebook FSC CLASS 7-25 – INPUT/OUTPUT AND STORAGE DEVICES 1. Display 2. Network Equipment 3. Storage Devices including Magnetic Storage, Magnetic Tape and Optical Disk NCS TECHNOLOGIES, INC. 7669 Limestone Drive Gainesville, VA 20155-4038 Tel: (703) 621-1700 Fax: (703) 621-1701 Website: www.ncst.com Contract Number: GS-35F-4677G – Option Year 3 Period Covered by Contract: May 15, 1997 through May 14, 2017 GENERAL SERVICE ADMINISTRATION FEDERAL ACQUISTIION SERVICE Products and ordering information in this Authorized FAS IT Schedule Price List is also available on the GSA Advantage! System. Agencies can browse GSA Advantage! By accessing GSA’s Home Page via Internet at www.gsa.gov. TABLE OF CONTENTS INFORMATION FOR ORDERING OFFICES ............................................................................................................................................................................................................................... TC-1 SPECIAL NOTICE TO AGENCIES – SMALL BUSINESS PARTICIPATION 1. Geographical Scope of Contract ............................................................................................................................................................................................................................. -

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

Case M:07-cv-01826-WHA Document 249 Filed 11/08/2007 Page 1 of 34 1 BOIES, SCHILLER & FLEXNER LLP WILLIAM A. ISAACSON (pro hac vice) 2 5301 Wisconsin Ave. NW, Suite 800 Washington, D.C. 20015 3 Telephone: (202) 237-2727 Facsimile: (202) 237-6131 4 Email: [email protected] 5 6 BOIES, SCHILLER & FLEXNER LLP BOIES, SCHILLER & FLEXNER LLP JOHN F. COVE, JR. (CA Bar No. 212213) PHILIP J. IOVIENO (pro hac vice) 7 DAVID W. SHAPIRO (CA Bar No. 219265) ANNE M. NARDACCI (pro hac vice) KEVIN J. BARRY (CA Bar No. 229748) 10 North Pearl Street 8 1999 Harrison St., Suite 900 4th Floor Oakland, CA 94612 Albany, NY 12207 9 Telephone: (510) 874-1000 Telephone: (518) 434-0600 Facsimile: (510) 874-1460 Facsimile: (518) 434-0665 10 Email: [email protected] Email: [email protected] [email protected] [email protected] 11 [email protected] 12 Attorneys for Plaintiff Jordan Walker Interim Class Counsel for Direct Purchaser 13 Plaintiffs 14 15 UNITED STATES DISTRICT COURT 16 NORTHERN DISTRICT OF CALIFORNIA 17 18 IN RE GRAPHICS PROCESSING UNITS ) Case No.: M:07-CV-01826-WHA ANTITRUST LITIGATION ) 19 ) MDL No. 1826 ) 20 This Document Relates to: ) THIRD CONSOLIDATED AND ALL DIRECT PURCHASER ACTIONS ) AMENDED CLASS ACTION 21 ) COMPLAINT FOR VIOLATION OF ) SECTION 1 OF THE SHERMAN ACT, 15 22 ) U.S.C. § 1 23 ) ) 24 ) ) JURY TRIAL DEMANDED 25 ) ) 26 ) ) 27 ) 28 THIRD CONSOLIDATED AND AMENDED CLASS ACTION COMPLAINT BY DIRECT PURCHASERS M:07-CV-01826-WHA Case M:07-cv-01826-WHA Document 249 Filed 11/08/2007 Page 2 of 34 1 Plaintiffs Jordan Walker, Michael Bensignor, d/b/a Mike’s Computer Services, Fred 2 Williams, and Karol Juskiewicz, on behalf of themselves and all others similarly situated in the 3 United States, bring this action for damages and injunctive relief under the federal antitrust laws 4 against Defendants named herein, demanding trial by jury, and complaining and alleging as 5 follows: 6 NATURE OF THE CASE 7 1. -

Xfx Geforce 8200 Motherboard Drivers Download, Xfx Geforce 8200 Motherboard Drivers

xfx geforce 8200 motherboard drivers download, Xfx geforce 8200 motherboard drivers. Downloaded: 19,337 times Last Time: 10 August 2021 On neutechcomputerservices.com you can find most up to date drivers ready for download. Save and fast, we are here to support you and your hardware. Happy to assist, please let us know if anything is missing. Xfx geforce 8200 motherboard drivers User Comments. 09-Apr-21 21:35 aaaaaa. i've been waiting for this for ages!! thanks :)) 22-Aug-19 14:32 Super love it thank u for Xfx geforce 8200 motherboard s. DRIVER XFX GEFORCE 8200 ETHERNET FOR WINDOWS 7 64BIT DOWNLOAD. Very low CPU utilization, anytime. The XFX GEFORCE 8200 from didn't provide the menu. Find many DirectX 10 gjennom hele prisspekteret. The ZOTAC GeForce 8200-ITX WiFi is capable of playing high-definition Blu-ray with very low CPU utilization, sending vivid high-definition visuals and high-definition audio to high-definition displays over its DVI output, or HDMI output using the included DVI-to-HDMI adapter. Update your graphics card drivers today. Also for, Geforce 8100 mi-a78v-8109 , Geforce 8200 mi-a78s-8209 , Geforce 8300 mi-a78u-8309, Geforce. As we have never been driving me crazy! Graphics Card with NVIDIA nForce 720a nForce 630i with fellow gamers. NForce 750a SLI, nForce 740a SLI, nForce 730a/GeForce 8300/8200, nForce 720a - GeForce 8100, nForce. 1.08.2009 XFX Mobo- Trouble Installing Ethernet Driver - posted in Hardware, Components and Peripherals, So this has been driving me crazy! I've downloaded the one off xfx's website and it doesn't work. -

Programming Graphics Hardware Overview of the Tutorial: Afternoon

Tutorial 5 ProgrammingProgramming GraphicsGraphics HardwareHardware Randy Fernando, Mark Harris, Matthias Wloka, Cyril Zeller Overview of the Tutorial: Morning 8:30 Introduction to the Hardware Graphics Pipeline Cyril Zeller 9:30 Controlling the GPU from the CPU: the 3D API Cyril Zeller 10:15 Break 10:45 Programming the GPU: High-level Shading Languages Randy Fernando 12:00 Lunch Tutorial 5: Programming Graphics Hardware Overview of the Tutorial: Afternoon 12:00 Lunch 14:00 Optimizing the Graphics Pipeline Matthias Wloka 14:45 Advanced Rendering Techniques Matthias Wloka 15:45 Break 16:15 General-Purpose Computation Using Graphics Hardware Mark Harris 17:30 End Tutorial 5: Programming Graphics Hardware Tutorial 5: Programming Graphics Hardware IntroductionIntroduction toto thethe HardwareHardware GraphicsGraphics PipelinePipeline Cyril Zeller Overview Concepts: Real-time rendering Hardware graphics pipeline Evolution of the PC hardware graphics pipeline: 1995-1998: Texture mapping and z-buffer 1998: Multitexturing 1999-2000: Transform and lighting 2001: Programmable vertex shader 2002-2003: Programmable pixel shader 2004: Shader model 3.0 and 64-bit color support PC graphics software architecture Performance numbers Tutorial 5: Programming Graphics Hardware Real-Time Rendering Graphics hardware enables real-time rendering Real-time means display rate at more than 10 images per second 3D Scene = Image = Collection of Array of pixels 3D primitives (triangles, lines, points) Tutorial 5: Programming Graphics Hardware Hardware Graphics Pipeline -

GPU-Based Deep Learning Inference

Whitepaper GPU-Based Deep Learning Inference: A Performance and Power Analysis November 2015 1 Contents Abstract ......................................................................................................................................................... 3 Introduction .................................................................................................................................................. 3 Inference versus Training .............................................................................................................................. 4 GPUs Excel at Neural Network Inference ..................................................................................................... 5 Inference Optimizations in Caffe and cuDNN 4 ........................................................................................ 5 Experimental Setup and Testing Methodology ........................................................................................ 7 Inference on Small and Large GPUs .......................................................................................................... 8 Conclusion ................................................................................................................................................... 10 References .................................................................................................................................................. 10 2 Abstract Deep learning methods are revolutionizing various areas of machine perception. On a -

How to Download 382.33 Nvidia Driver Geforce Game Ready Driver

how to download 382.33 nvidia driver GeForce Game Ready Driver. As part of the NVIDIA Notebook Driver Program, this is a reference driver that can be installed on supported NVIDIA notebook GPUs. However, please note that your notebook original equipment manufacturer (OEM) provides certified drivers for your specific notebook on their website. NVIDIA recommends that you check with your notebook OEM about recommended software updates for your notebook. OEMs may not provide technical support for issues that arise from the use of this driver. Before downloading this driver: It is recommended that you backup your current system configuration. Click here for instructions. Game Ready Drivers provide the best possible gaming experience for all major new releases, including Virtual Reality games. Prior to a new title launching, our driver team is working up until the last minute to ensure every performance tweak and bug fix is included for the best gameplay on day-1. Game Ready Provides the optimal gaming experience for Tekken 7 and Star Trek Bridge Crew. Notebooks supporting Hybrid Power technology are not supported (NVIDIA Optimus technology is supported). The following Sony VAIO notebooks are included in the Verde notebook program: Sony VAIO F Series with NVIDIA GeForce 310M, GeForce GT 330M, GeForce GT 425M, GeForce GT 520M or GeForce GT 540M. Other Sony VAIO notebooks are not included (please contact Sony for driver support). Fujitsu notebooks are not included (Fujitsu Siemens notebooks are included). GeForce GTX 1080, GeForce GTX 1070, GeForce GTX 1060, GeForce GTX 1050 Ti, GeForce GTX 1050. GeForce 900M Series (Notebooks): GeForce GTX 980, GeForce GTX 980M, GeForce GTX 970M, GeForce GTX 965M, GeForce GTX 960M, GeForce GTX 950M, GeForce 945M, GeForce 940MX, GeForce 930MX, GeForce 920MX, GeForce 940M, GeForce 930M, GeForce 920M, GeForce 910M. -

Download Gtx 970 Driver Download Gtx 970 Driver

download gtx 970 driver Download gtx 970 driver. Completing the CAPTCHA proves you are a human and gives you temporary access to the web property. What can I do to prevent this in the future? If you are on a personal connection, like at home, you can run an anti-virus scan on your device to make sure it is not infected with malware. If you are at an office or shared network, you can ask the network administrator to run a scan across the network looking for misconfigured or infected devices. Another way to prevent getting this page in the future is to use Privacy Pass. You may need to download version 2.0 now from the Chrome Web Store. Cloudflare Ray ID: 67a229f54fd4c3c5 • Your IP : 188.246.226.140 • Performance & security by Cloudflare. GeForce Windows 10 Driver. NVIDIA has been working closely with Microsoft on the development of Windows 10 and DirectX 12. Coinciding with the arrival of Windows 10, this Game Ready driver includes the latest tweaks, bug fixes, and optimizations to ensure you have the best possible gaming experience. Game Ready Best gaming experience for Windows 10. GeForce GTX TITAN X, GeForce GTX TITAN, GeForce GTX TITAN Black, GeForce GTX TITAN Z. GeForce 900 Series: GeForce GTX 980 Ti, GeForce GTX 980, GeForce GTX 970, GeForce GTX 960. GeForce 700 Series: GeForce GTX 780 Ti, GeForce GTX 780, GeForce GTX 770, GeForce GTX 760, GeForce GTX 760 Ti (OEM), GeForce GTX 750 Ti, GeForce GTX 750, GeForce GTX 745, GeForce GT 740, GeForce GT 730, GeForce GT 720, GeForce GT 710, GeForce GT 705. -

![Arxiv:1809.03668V2 [Cs.LG] 20 Jan 2019 17, 20, 21]](https://docslib.b-cdn.net/cover/1376/arxiv-1809-03668v2-cs-lg-20-jan-2019-17-20-21-481376.webp)

Arxiv:1809.03668V2 [Cs.LG] 20 Jan 2019 17, 20, 21]

Comparing Computing Platforms for Deep Learning on a Humanoid Robot Alexander Biddulph∗, Trent Houliston, Alexandre Mendes, and Stephan K. Chalup School of Electrical Engineering and Computing The University of Newcastle, Callaghan, NSW, 2308, Australia. [email protected] Abstract. The goal of this study is to test two different computing plat- forms with respect to their suitability for running deep networks as part of a humanoid robot software system. One of the platforms is the CPU- centered Intel R NUC7i7BNH and the other is a NVIDIA R Jetson TX2 system that puts more emphasis on GPU processing. The experiments addressed a number of benchmarking tasks including pedestrian detec- tion using deep neural networks. Some of the results were unexpected but demonstrate that platforms exhibit both advantages and disadvantages when taking computational performance and electrical power require- ments of such a system into account. Keywords: deep learning, robot vision, gpu computing, low powered devices 1 Introduction Deep learning comes with challenges with respect to computational resources and training data requirements [6, 13]. Some of the breakthroughs in deep neu- ral networks (DNNs) only became possible through the availability of massive computing systems or through careful co-design of software and hardware. For example, the AlexNet system presented in [15] was implemented efficiently util- ising two NVIDIA R GTX580 GPUs for training. Machine learning on robots has been a growing area over the past years [4, arXiv:1809.03668v2 [cs.LG] 20 Jan 2019 17, 20, 21]. It has become increasingly desirable to employ DNNs in low powered devices, among them humanoid robot systems, specifically for complex tasks such as object detection, walk learning, and behaviour learning. -

Nvidia Forceware Graphics Drivers for XP, Manual and Notes

ForceWare Graphics Drivers Release 162 Notes Version 162.18 for Windows XP NVIDIA Corporation June 29, 2007 Confidential Information Published by NVIDIA Corporation 2701 San Tomas Expressway Santa Clara, CA 95050 Notice ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, “MATERIALS”) ARE BEING PROVIDED “AS IS.” NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE. Information furnished is believed to be accurate and reliable. However, NVIDIA Corporation assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of NVIDIA Corporation. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. NVIDIA Corporation products are not authorized for use as critical components in life support devices or systems without express written approval of NVIDIA Corporation. Trademarks NVIDIA, the NVIDIA logo, 3DFX, 3DFX INTERACTIVE, the 3dfx Logo, STB, STB Systems and Design, the STB Logo, the StarBox Logo, NVIDIA nForce, GeForce, NVIDIA Quadro, NVDVD, NVIDIA Personal Cinema, NVIDIA Soundstorm, Vanta, TNT2, TNT, -

Specification XPC SN85G4V3

Shuttle Mini Barebone PC System Hardware at its finest! Based on NVIDIA's nForce3 250 chipset this 3rd generation SN85G4 shines with an excellent feature set, quiet operation and cool thermals. It boasts plenty of power under the hood that can satisfy the demands of the most power hungry gamers, while presenting a very well design and aesthetically pleasing exterior. The SN85G4V3 is not only the right weapon for every LAN- party, but also a fast companion at home. The XPC SN85G4V3 is an ideal: LAN-gaming PC, Home gaming machine, Digital media management center, Digital content workstation. Feature Highlight · Black Alu chassis with mirror front face · Integrated 8-in-1 card reader G4 chassis · Temperature controlled 92mm fan · Bays: 1x 5.25“, 1x 3.5“ Chipset · NVIDIA nForce3 250 · Socket 754 CPU · Supports AMD Athlon 64 · 1 x AGP (8X) Slots · 1 x PCI Memory · Supports 2x DDR-400/333 Drive · 2x Serial ATA Raid connectors · 2x IDE ATA 133 other · 6-channel audio, SPDIF connectors · Firewire, USB 2.0, LAN Power supply · Silent-X 240 Watt Application · Gaming Article number: SN85G4V3 Order number: PC-SN85G4V3 UPC (see bar code) Date: 24. Nov. 2004 Shuttle Computer Handels GmbH, Fritz-Strassmann-Strasse 5, D-25337 Elmshorn, Germany Tel. +49 (0)4121 476-860 Fax. +49 (0)4121 476-900 Email: [email protected] www.shuttle.com Shuttle Mini Barebone PC System Specification Chassis G4-type chassis made of aluminum, black color, acrylic mirror front face integrated 8-in-1 memory card reader storage bays: 1 x 5.25" (external), 1 x 3.5" ( internal) dimensions: 30 x 20 x 18.5 cm (LWH), weight: 2.85 kg net / 4.65 kg gross Mainboard Shuttle FN85, Shuttle form factor, proprietary design for SN85G4V3 chipset: NVIDIA nForce3 250 with HyperTransport link at 1600MT/s Award V6.0PG BIOS, 4MBit flash memory with hardware monitoring and ACPI power management functions dimensions: 25.4 x 18.5 cm Power supply Silent-X 240 Watt mini PSU, supports 115/230V connectors: 20-pin ATX, 4-pin ATX12V Processor support Socket 754 supports AMD Athlon 64 processors Processor cooling Shuttle I.C.E. -

Numerical Behavior of NVIDIA Tensor Cores

Numerical behavior of NVIDIA tensor cores Massimiliano Fasi1, Nicholas J. Higham2, Mantas Mikaitis2 and Srikara Pranesh2 1 School of Science and Technology, Örebro University, Örebro, Sweden 2 Department of Mathematics, University of Manchester, Manchester, UK ABSTRACT We explore the floating-point arithmetic implemented in the NVIDIA tensor cores, which are hardware accelerators for mixed-precision matrix multiplication available on the Volta, Turing, and Ampere microarchitectures. Using Volta V100, Turing T4, and Ampere A100 graphics cards, we determine what precision is used for the intermediate results, whether subnormal numbers are supported, what rounding mode is used, in which order the operations underlying the matrix multiplication are performed, and whether partial sums are normalized. These aspects are not documented by NVIDIA, and we gain insight by running carefully designed numerical experiments on these hardware units. Knowing the answers to these questions is important if one wishes to: (1) accurately simulate NVIDIA tensor cores on conventional hardware; (2) understand the differences between results produced by code that utilizes tensor cores and code that uses only IEEE 754-compliant arithmetic operations; and (3) build custom hardware whose behavior matches that of NVIDIA tensor cores. As part of this work we provide a test suite that can be easily adapted to test newer versions of the NVIDIA tensorcoresaswellassimilaracceleratorsfromothervendors,astheybecome available. Moreover, we identify a non-monotonicity issue