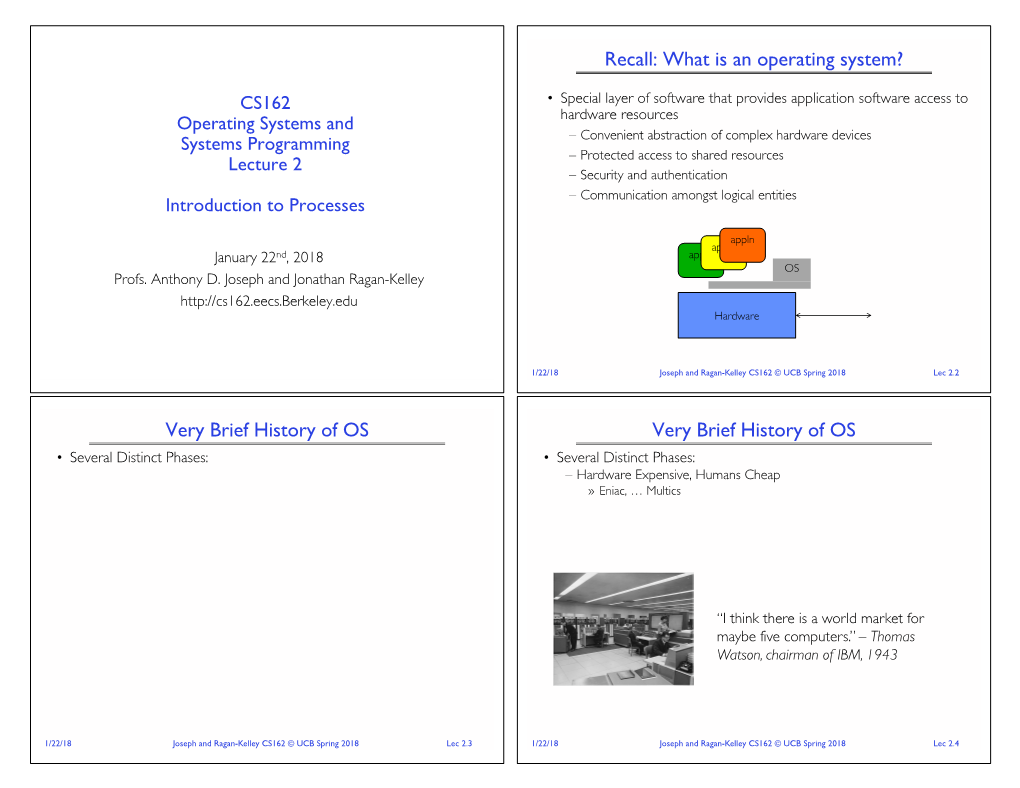

Recall: What Is an Operating System? Very Brief History of OS Very Brief

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Moving FLASK to BSD Systems

MovingMoving FLASKFLASK toto BSDBSD SSystemsystems SELinux Symposium 2006 Chris Vance Information Systems Security Operation, SPARTA, Inc. Vance_20060301_01 Overview • Security Frameworks • A Brief History • SELinux Inspired… – Security Enhanced BSD – Security Enhanced Darwin Vance_20060301_02 Security Frameworks • Traditional UNIX security isn’t enough – OS hardening – Mandatory protection – Flexible, manageable, scalable protection • Support required in the operating system for new security services – Costs of locally maintaining security extensions are high – Framework offers extensibility so that policies may be enhanced without changing the base operating system • There does not appear to be one perfect security model or policy – Sites may have different security/performance trade-offs – Sites may have special local requirements – Vendors unlikely to adopt a single policy • Bottom Line: Frameworks for Linux, FreeBSD, Darwin Vance_20060301_03 How We Got Here… Vance_20060301_04 Focus and Reuse • Don’t “reinvent” security – Learn from the past – The research is often decades old – A good design is durable, doesn’t require constant change – FLASK hasn’t changed much recently, what’s that mean? • Leverage existing technology, focus on “new” issues – Focus on improving operating system security – Spend the time to get Frameworks correct – Work with vendor for acceptance – Develop rule sets that work – Develop effective tools to manage policy • Do innovate – Don’t stop thinking! – Don’t squash new ideas – Re-factor old ideas Vance_20060301_05 -

A Brief Technical Introduction

Mac OS X A Brief Technical Introduction Leon Towns-von Stauber, Occam's Razor LISA Hit the Ground Running, December 2005 http://www.occam.com/osx/ X Contents Opening Remarks..............................3 What is Mac OS X?.............................5 A New Kind of UNIX.........................12 A Diferent Kind of UNIX..................15 Resources........................................39 X Opening Remarks 3 This is a technical introduction to Mac OS X, mainly targeted to experienced UNIX users for whom OS X is at least relatively new This presentation covers primarily Mac OS X 10.4.3 (Darwin 8.3), aka Tiger X Legal Notices 4 This presentation Copyright © 2003-2005 Leon Towns-von Stauber. All rights reserved. Trademark notices Apple®, Mac®, Macintosh®, Mac OS®, Finder™, Quartz™, Cocoa®, Carbon®, AppleScript®, Bonjour™, Panther™, Tiger™, and other terms are trademarks of Apple Computer. See <http://www.apple.com/legal/ appletmlist.html>. NeXT®, NeXTstep®, OpenStep®, and NetInfo® are trademarks of NeXT Software. See <http://www.apple.com/legal/nexttmlist.html>. Other trademarks are the property of their respective owners. X What Is It? 5 Answers Ancestry Operating System Products The Structure of Mac OS X X What Is It? Answers 6 It's an elephant I mean, it's like the elephant in the Chinese/Indian parable of the blind men, perceived as diferent things depending on the approach X What Is It? Answers 7 Inheritor of the Mac OS legacy Evolved GUI, Carbon (from Mac Toolbox), AppleScript, QuickTime, etc. The latest version of NeXTstep Mach, Quartz (from Display PostScript), Cocoa (from OpenStep), NetInfo, apps (Mail, Terminal, TextEdit, Preview, Interface Builder, Project Builder, etc.), bundles, faxing from Print panel, NetBoot, etc. -

Mac OS X Intro for UNIX Users

Mac OS X An Introduction for UNIX Users Leon Towns-von Stauber, Occam's Razor Seattle BSD Users Group, October 2004 http://www.occam.com/osx/ X Contents Opening Remarks.............................3 Where Did Mac OS X Come From?.....5 What is Mac OS X?..........................13 A New Kind of UNIX........................25 A Different Kind of UNIX.................28 Why Use Mac OS X?.........................60 Resources.......................................63 Closing Remarks.............................67 X Opening Remarks 3 This is a technical introduction to Mac OS X, mainly targeted to experienced UNIX users for whom OS X is at least relatively new Some emphasis on comparisons with FreeBSD I'm assuming basic familiarity with operating system design Where I'm coming from: UNIX user and some-time admin since 1990 Full-time UNIX admin since 1995 NeXTstep user and admin since 1991 This presentation covers primarily Mac OS X 10.3.5 (Darwin 7.5) X Legal Notices 4 This presentation Copyright © 2003-2004 Leon Towns-von Stauber. All rights reserved. Trademark notices Apple®, Mac®, Macintosh®, Mac OS®, Aqua®, Finder™, Quartz™, Cocoa®, Carbon®, AppleScript®, Rendezvous™, Panther™, and other terms are trademarks of Apple Computer. See <http:// www.apple.com/legal/appletmlist.html>. NeXT®, NeXTstep®, OpenStep®, and NetInfo® are trademarks of NeXT Software. See <http://www.apple.com/legal/nexttmlist.html>. PowerPC™ is a trademark of International Business Machines. Java™ is a trademark of Sun Microsystems. Other trademarks are the property of their -

The Apple Ecosystem

APPENDIX A The Apple Ecosystem There are a lot of applications used to manage Apple devices in one way or another. Additionally, here’s a list of tools, sorted alphabetically per category in order to remain vendor agnostic. Antivirus Solutions for scanning Macs for viruses and other malware. • AVG: Basic antivirus and spyware detection and remediation. • Avast: Centralized antivirus with a cloud console for tracking incidents and device status. • Avira: Antivirus and a browser extension. Avira Connect allows you to view device status online. • BitDefender: Antivirus and malware managed from a central console. • CarbonBlack: Antivirus and Application Control. • Cylance: Ransomware, advanced threats, fileless malware, and malicious documents in addition to standard antivirus. • Kaspersky: Antivirus with a centralized cloud dashboard to track device status. © Charles Edge and Rich Trouton 2020 707 C. Edge and R. Trouton, Apple Device Management, https://doi.org/10.1007/978-1-4842-5388-5 APPENDIX A THe AppLe ECOSYSteM • Malware Bytes: Antivirus and malware managed from a central console. • McAfee Endpoint Security: Antivirus and advanced threat management with a centralized server to track devices. • Sophos: Antivirus and malware managed from a central console. • Symantec Mobile Device Management: Antivirus and malware managed from a central console. • Trend Micro Endpoint Security: Application whitelisting, antivirus, and ransomware protection in a centralized console. • Wandera: Malicious hot-spot monitoring, jailbreak detection, web gateway for mobile threat detection that integrates with common MDM solutions. Automation Tools Scripty tools used to automate management on the Mac • AutoCasperNBI: Automates the creation of NetBoot Images (read: NBI’s) for use with Casper Imaging. • AutoDMG: Takes a macOS installer (10.10 or newer) and builds a system image suitable for deployment with Imagr, DeployStudio, LANrev, Jamf Pro, and other asr or Apple Systems Restore-based imaging tools. -

Objective-C Bootcamp | Ios Programming Course

Contact Us 978.250.4983 iOS Programming for iPhone® and iPad® Applications Using Objective-C Duration: 35 hours Prerequisites: Prior programming experience in an object-oriented language. Course Description: Participants in this hands-on course will learn about and gain practice developing iOS applications for iPhone and iPad devices. Attendees will learn all the basics needed for iOS development, from installation of the Xcode editor to the Apple approval process. The Objective-C language is presented and used in hands on exercises to learn how it interacts with the hardware systems. In hands on exercises, students will use built-in data views as well as create custom screens for data entry and presentation. Students will learn to follow Apple's design recommendations to provide clean interfaces that appropriately size to various devices and screens. The course includes coverage of scheduled background execution to allow code to be run when the app isn't active and to schedule alerts to draw attention back to the app. Comprehensive hands on exercises are integrated throughout to reinforce learning and develop real competency. Students will create apps from the ground up, demonstrating the features of Objective-C and serving as an introduction to developing apps for release to the App Store. Students Will Learn Protocols/Delegates, Notifications and KVC/KVO iOS Overview Forms, Views and ViewControllers Using Xcode NSObjects and other Foundation Classes Objective-C Language Fundamentals Dynamic Typing vs Static Typing and Introspection -

Workstation Operating Systems Mac OS 9

15-410 “Now that we've covered the 1970's...” Plan 9 Nov. 25, 2019 Dave Eckhardt 1 L11_P9 15-412, F'19 Overview “The land that time forgot” What style of computing? The death of timesharing The “Unix workstation problem” Design principles Name spaces File servers The TCP file system... Runtime environment 3 15-412, F'19 The Land That Time Forgot The “multi-core revolution” already happened once 1982: VAX-11/782 (dual-core) 1984: Sequent Balance 8000 (12 x NS32032) 1985: Encore MultiMax (20 x NS32032) 1990: Omron Luna88k workstation (4 x Motorola 88100) 1991: KSR1 (1088 x KSR1) 1991: “MCS” paper on multi-processor locking algorithms 1995: BeBox workstation (2 x PowerPC 603) The Land That Time Forgot The “multi-core revolution” already happened once 1982: VAX-11/782 (dual-core) 1984: Sequent Balance 8000 (12 x NS32032) 1985: Encore MultiMax (20 x NS32032) 1990: Omron Luna88k workstation (4 x Motorola 88100) 1991: KSR1 (1088 x KSR1) 1991: “MCS” paper on multi-processor locking algorithms 1995: BeBox workstation (2 x PowerPC 603) Wow! Why was 1995-2004 ruled by single-core machines? What operating systems did those multi-core machines run? The Land That Time Forgot Why was 1995-2004 ruled by single-core machines? In 1995 Intel + Microsoft made it feasible to buy a fast processor that fit on one chip, a fast I/O bus, multiple megabytes of RAM, and an OS with memory protection. Everybody could afford a “workstation”, so everybody bought one. Massive economies of scale existed in the single- processor “Wintel” universe. -

DISCOVERING OPENSTEP: a Developer Tutorial

DISCOVERING OPENSTEP: A Developer Tutorial Rhapsody Developer Release Apple Computer, Inc. User Interface Tips copyright © 1997 Apple Computer, Inc. All rights reserved. [6467.00] No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc., except to make a backup copy of any documentation provided on CD-ROM. Printed in the United States of America. The Apple logo is a trademark of Apple Computer, Inc. Use of the “keyboard” Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws. No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist application developers to develop applications only for Apple-labeled or Apple-licensed computers. Every effort has been made to ensure that the information in this manual is accurate. Apple is not responsible for printing or clerical errors. Apple Computer, Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010 Apple, and the Apple logo are trademarks of Apple Computer, Inc., registered in the United States and other countries. NeXT, the NeXT logo, NEXTSTEP, the NEXTSTEP logo, Digital Librarian, NeXTmail, and -

Chapter 1. Getting Started

Chapter 1. Getting Started This book teaches the Swift 3 programming language by exploring the development of three applications for Apple platforms: macOS, iOS, and watchOS. This book’s approach might differ from what you’re used to, because our philosophy is that the best way to learn Swift is to build apps using it! The vast majority of the code in this book will be part of the apps we’re building—a full note-taking app for macOS, iOS, and watchOS—rather than individual pieces of sample code. You can see the final product in Figure 1-1. Figure 1-1. Our finished app, for macOS, iOS, and watchOS Our app is fully functional, but we do make some deliberate design and feature decisions along the way to constrain the scope a little (the book is almost 500 pages!). As we mentioned in the Preface, we assume that you’re a reasonably capable programmer, but we don’t assume you’ve ever developed for iOS or macOS, or used Swift or Objective-C before. We also assume that you’re fairly comfortable navigating macOS and iOS as a user. TIP We recommend that you work through this book front to back, building the macOS app, then the iOS app, then the watchOS app, even if you’re only interested in one of the platforms. By approaching the book this way, you’ll get the best understanding of what building a real app with Swift requires. Programming with Swift, and using the Cocoa and Cocoa Touch frameworks to develop macOS and iOS apps, respectively, involves using a set of tools developed by Apple. -

Rhapsody Developer's Guide

Jesse Feiler AP PROFESSIONAL AP Professional is a division of Academic Press Boston San Diego New York London Sydney Tokyo Toronto Find us on the Web! http:/ /www.apnet.com This book is printed on acid-free paper. @ Copyright © 1997 by Academic Press. All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording, or any information storage and retrieval system, without permission in writing from the publisher. Excerpts from Chartsmith are copyright © 1997 by Blacksmith, Inc. All rights reserved. Excerpts from OpenBase are copyright © 1997 by OpenBase International, Ltd. All rights reserved. Excerpts from Create are copyright © 1997 by Stone Design, Inc. All rights reserved. Excerpts from OmniWeb are copyright © 1997 by Omni Development, Inc. All rights reserved. Excerpts from TIFFany are copyright © 1997 by Caffeine Software. All rights reserved. All brand names and product names mentioned in this book are trademarks or registered trademarks of their respective companies. Academic Press 525 B Street, Suite 1900, San Diego, CA 92101-4495 1300 Boylston Street, Chestnut Hill, MA 02167 United Kingdom Edition published by ACADEMIC PRESS LIMITED 24-28 Oval Road, London NW1 7DX ISBN 0-12-251334-7 Printed in the United States of America 97 98 99 00 CP 9 8 7 6 5 4 3 2 1 Table of Contents Advanced Mac Look and Feel i Y e llo w Box Mac OS 0P6NSTgP based JaCT^ Core OS: Microkernel, ^0, Fiie System... |Power Macintosh, PowerPC Piatform Hardware Semantics T ables ........................................................................................... xv Preface........................................................................................................... -

Mach-O Internals

Mach-O Internals William Woodru February 10, 2016 1 / 31 General Agenda 1. Who are you? 2. What is Mach-O? 3. An Extremely Brief History of Mach and Mach-O 4. Structure of a Mach-O File 5. Quirks Encountered 6. Concluding Notes 2 / 31 Who are you? My name is William Woodru. I'm a Computer Science major and Philosophy minor at the University of Maryland, College Park. Outside of school, I'm a member of the Homebrew project and a regular contributor to several open source groups. My work for Homebrew is largely concerned with the underlying system interface and reconciling OS X's intricacies/irregularities with the package manager. 3 / 31 What is Mach-O? Mach-O is the Mach Object binary format. Mach-O is used primarily by Apple in OS X and iOS. Apps on both platforms are really just directory trees containing Mach-O binaries and resources (fonts, icons, congurations). Metadata is stored in a number of places, but mainly within bundled plists (XML) and the binaries themselves. Like its cousins on Linux (ELF) and Windows (PE), Mach-O supports multiple object types: I Executable I Core dump I Shared library/object I Prelinked object le I etc. 4 / 31 . and multiple architectures: I m68k/m88k (yes, it's still supported!*) I x86 I AMD64 I POWER I ARMv6/7/8 Unlike ELF or PE, Mach-O has been extended to allow multi-architecture fat binaries. This has resulted in some interesting properties not shared by the other two. More on that later. -

School Management Application Using Ios

38 Academic Journal of Nawroz University (AJNU) School Management Application Using iOS Renas Rajab Asaad1, Rasan Ismail Segerey2 Department of Computer Science, Nawroz University, Duhok, Kurdistan Region – Iraq, Researcher, Duhok, , Kurdistan Region – Iraq ABSTRACT Recently, the mobile application become a big service that’s make users easy manage the data over the server. The Application consist several sections. First section the Front End used is Swift Language in Xcode platform with MySQL and web server. Second section the Back End used is MySQL. In this paper there are several modules such as Data Entry module, Data Records module. These modules are further divided in to sub modules. That is Class Setup, Student Setup, Teacher Setup, Student Attendance, Subject Setup, Examination Setup and Exam Details are in Data Entry module. Student Details, Teacher Records, Student Attendance are in the Data Records module. These modules give way in managing the organization efficiently. So, this project helps in efficient management of human resource inside the organization. Also, it consumes less time consumption. The main and important benefit of this proposed Application is that it is very much user friendly and accurate. So the employees and the administrators feel so much comfortable to work with it. Also in all the modules the regularly updated information are very much useful when they are extracted. Keywords: iOS, School Management Application, Computer Science. 1. Introduction A School Management Application is a large database application which can be used for managing school's daily work. It is configurable and can be configured to meet most individual school's needs. -

WWDC17 Louis Gerbarg, Senior Linker Engineer Developer

Developer #WWDC17 App• Startup Time: Past, Present, and Future • Session 413 Louis Gerbarg, Senior Linker Engineer © 2017 Apple Inc. All rights reserved. Redistribution or public display not permitted without written permission from Apple. • Review of app launch startup advice • New tools to help find slow initializers • Brief history of dyld • The all new dyld that is coming in this years Apple OS platforms • Best practices Preamble Preamble We want your feedback Preamble We want your feedback • Please file bug reports with “DYLD USAGE:” in the title Preamble We want your feedback • Please file bug reports with “DYLD USAGE:” in the title Terminology Preamble We want your feedback • Please file bug reports with “DYLD USAGE:” in the title Terminology • Startup time Preamble We want your feedback • Please file bug reports with “DYLD USAGE:” in the title Terminology • Startup time - For the purposes of this talk startup time is everything that happens before main() is called Preamble We want your feedback • Please file bug reports with “DYLD USAGE:” in the title Terminology • Startup time - For the purposes of this talk startup time is everything that happens before main() is called • Launch Closure Preamble We want your feedback • Please file bug reports with “DYLD USAGE:” in the title Terminology • Startup time - For the purposes of this talk startup time is everything that happens before main() is called • Launch Closure - All of the information necessary to launch an application Improving App Startup Time Optimizing App Startup Time WWDC