Sol-20 Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ALTAIR 8800 CLONE COMPUTER OPERATOR's MANUAL Version

ALTAIR 8800 CLONE COMPUTER OPERATOR’S MANUAL Version 2.3, April 2021 TABLE OF CONTENTS INTRODUCTION ............................................................... 1 PART 1 – ALTAIR 8800 CLONE HARDWARE SPECIFICATIONS ......................... 2 PART 2 – CONFIGURATION MONITOR ............................................. 4 A. Floppy Disk Menu ....................................................... 4 B. PROM Menu .............................................................. 6 C. Serial Port Menu ....................................................... 7 D. Load .BIN or .HEX File ................................................. 9 E. Administration Menu .................................................... 9 PART 3 – TERMINAL EMULATOR ................................................ 14 A. Overview .............................................................. 14 B. TeraTerm Terminal Emulator ............................................ 14 C. Installing TeraTerm ................................................... 14 D. Configuring TeraTerm .................................................. 14 E. Using TeraTerm ........................................................ 15 PART 4 – ALTAIR 8800 DEMONSTRATIONS ....................................... 16 A. Kill-the-Bit Front Panel Game ......................................... 16 B. Loading and Using 4K BASIC from Paper Tape ............................ 18 C. Loading and Using 8K BASIC from Cassette .............................. 21 D. Loading and Using Disk BASIC from Floppy Disk ........................ -

MITS Altair 8800 Computer Systems Brochure

MITS ALTAI 800 A Computer Concept Becomes an ex •ting reality. •••••••••• Contents ••••••••••••••••••••••••••• Introduction •....•.•.•.•••••••••••• 3 Altair Systems .........•........•.. 5 The Ultimate System .......•....•.•. 7 The Possibilities .......•....•....• S User Applications ......•.......•.. 10 Altair Options ..........•..•...•.• ll Processor Description ........••.•. 14 Processor Instructions ............ l5 Questions &Answers ......••....•.• 17 1....................................................... .1 Warranty: 90 days on parts and labor fOf assembled units. 90 days on parts fOf kits. Prices, spec'ifications and delivery subject to change without notice. 6328 LINN, N.E .., P.O. BOX 8636, ALBUQUERQUE, N.M. 87108 505/265-7553 © MITS, Inc. 1974 PRINTED IN U.S:A. .. PIPE DREAM? Not too long ago, the thought of an honest, full-blown, high-quality computer that sells for less than $500 would have been considered a mere pipe dream. Everyone knows that computers are monstrous, box-shaped machines that sell for 10's and 100's of thousands of dollars. Pipe dream or not, MITS, the quality engineering company that pioneered the calcu lator market, has made the Altair 8800 a reality. It is the realization of that day when computers arc accessible to almost anyone who wants one. I The heart (and the secret) of the M ITS Altair 8800 is the Intel 8080 processor chip. Thanks to rapid advances in integrated circuit technology, this one IC chip can now do 3 what once took thousands of electronic components (including 100's of IC's) and miles of wire. Make no mistake about it. The M ITS Altair 8800 is a lot of brain power. Its parallel, 8-bit processor uses a 16-bit address. It has 78 basic machine instructions with variances up to 200 instructions. -

M.Nlo Hrk, CA

vee P.t). b{)x JI() pa... k.~ca.~4-02~ N-.Proflt a... U.I.I"OSTAGE PAID ",""h No. 427 M.nlo hrk, CA Celiverto+ ~• jli • ~• N n z- 0 of m,. 3 m 0 'a m 0 c:: 0 _.M• I :::II -'U UI m 'U c» of 0 m 3: DI 3 m .... D ..lI D ~ ~ 111 u::: Not too long ago it became pouible for large scale chips to be made. Intel rolled the ball with the 800e. then rolled it some more with the 8(110. This year's real winner looks like being the PACE chip, from National Semiconductor. These things are oot easy to make. The difficulty of making them is lIflormoosly increased as they get bigger ••nd a 16 bit CPu is awful big. The $lory starts with a few enthusia$ls. a blackboard and a whole crew who doubted it could be made at all. Moby chip, as it was known, was oot a project for the faint hearted. The crooked tines on the blackboard soon became straight and well defined. Very. This is the beginning of the marks which OPtically define the position of every tiny facet of the chip to be. The precision of the whole process starts here, and hera also is the place where chips can be designed not to work - tNery line is checked and rechecked and ... Sometimes a particular person can make things when others can't. There Is the tale of the big manufacturer Now the magic begins. It starts with. sinlJle Cl'VSUI which was licensing a company in another country to of pure silicon. -

Dr. Dobb's Journal of $1.So COMPUTER Calisthenics & Orthodontia Running Light Without Overbyte June/July, 1976 Box 310, Menlo Park CA 94025 Volume 1, Number 6

dr. dobb's journal of $1.so COMPUTER Calisthenics & Orthodontia Running Light Without Overbyte June/July, 1976 Box 310, Menlo Park CA 94025 Volume 1, Number 6 A REFERENCE JOURNAL FOR USERS OF HOME COMPUTERS .CONSUMER COMMENTS ·fraUie for Pittman's 6800 Tiny BASIC [letter & reply] 4 Denver's Digital Group Kit Draws Praise [letter] 5 Good Reports & Plaudits for MOS Technology[letter/note] 5 Accentuate the Software; Eliminate the Games [letter/reply] 6 Short on Length, hut Long on Quality [letter] 6 A Novice Constructs an IMSAL S. A. Cochran, Jr. 7 Don't Underestimate BASIC fletter] 40 an attorney builds his first computer BASIC Complaint & Macro Message [letter & reply] 40 FCC Petition on ANSCII Transmission by Hams 42 Dennis Allison reply points out BASIC limitations SOFTWARE A Bootstrap for the 8080, Lichen Wang 8 Byte-Saving Programming Tricks for the 8080, Tom Pittman 9 An Exercise for Novice Translator Implementors, Bill Thompson 11 A Classy 8080 Text Editor, similar to a PDP-9 Editor, F. J. Greeb 13 includes general comments, user documentation & extensively annotated source code Tiny Trek for Mueller's MINOL, Erik Mueller 37 Button, Button Game in 8080 Machine Code, Ron Santore 38 CORRECTIONS & IMPROVEMENTS Errors in & Improvements for Texas Tiny BASIC (TBX), Charles Skeldon 3'4 Errata & Additions to Wang's Palo Alto Tiny BAS1C, Lichen Wang 35 MinErrata for MINOL, plus Tiny Trek, Erik Mueller 36 VIDEO OUTPUT 48 Lines of 64 Characters on a TV for $499. 95, Video· Terminal Technology 27 512-Character Video RAM from Canada, Matrox Electronic Systems 27 Variable Character Spacing in Video Displays, Jim Day 28 TVT-11 Mods to Get 64 Characters per Line, David Valliere . -

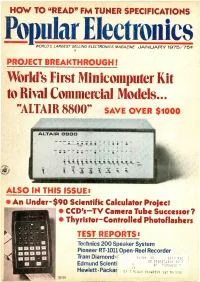

Build the Altair 8800 Mini Computer, Part 1

HOW TO "READ" FM TUNER SPECIFICATIONS 7t ioiiIc $ WORLDS LARGEST-SELLING ELECTRONICS MAGAZINE JANUARY 1975/75¢ PROJECT BREAKTHROUGH! 1Mild's First Minicomputer Kit to Rival Commercial Models... ALTAIR 88U0" SAVE OVER $1000 { A LTA 1R 8800 PAX: 1. let F In au an {0 l O, OS T- f a, ci tt n Os S i Q 11 . `/ MOO J t '4, _ , - . r . _ !w tn. LIS All tl U at = Al {{ U /11. At at {O O 6 G .. t O u 11 tt 1! 11 uMu ' AlOS tnr uuw aMut . sr MOW .a a.Ma4ai ' . in 9 - t- 4 ALSO IN THIS ISSUE: An Under -$90 Scientific Calculator Project o,ae . CCD's-TV Camera Tube Successor? . r'`?99` Thyristor-Controlled Photoflashers ;- TEST REPORTS: lSt Technics 200 Speaker System le Q 0'© Pioneer RT-1011 Open -Reel Recorder Tram Diamond í,6. 3:cr Nvs .aa,© - é f g COGN311 Aw 551 Edmund Scientw sr .1121abEi 1 i4 Hewlett-Packar , t 9teat C6451CC479 kxG' 96IC4£ 18101 AmericanRadioHistory.Com Popular Electronics PC 1117/ JANUARY, 1975 TESTED EXCLUSIVE! ALTAIR 8800 The most powerful minicomputer project ever presente -caM be built for under $400 á: . ;' --¢-^-. ., - .-r= ALTAIR 8800 ui1 PIOr MM. °,ei r i1 Our eUI ,;11.101.- 30 IR' It ° 05 04 U n- 11 00 5, n t [ ,'r` q [1. Q.,' Q.-.. ó ' ri '11 43 ' gout 3301-I@ IM R] !It III MO 7, M 03 tl,ai' II II°. 'lb II. C' , 0 O . U,.G t! , , U, l ° ' 1 , , . ' ' - ' .1 IS ...se . I 1 1- 1 S 1^ I 0 - r 10 /1 p r5 e-, .INAull, _ y 1 "-----11 4% 4% ":-....:174111.UAfíS N 331 IrOi . -

The Computer History Simulation Project

The Computer History Simulation Project The Computer History Simulation Project The Computer History Simulation Project is a loose Internet-based collective of people interested in restoring historically significant computer hardware and software systems by simulation. The goal of the project is to create highly portable system simulators and to publish them as freeware on the Internet, with freely available copies of significant or representative software. Simulators SIMH is a highly portable, multi-system simulator. ● Download the latest sources for SIMH (V3.5-1 updated 15-Oct-2005 - see change log). ● Download a zip file containing Windows executables for all the SIMH simulators. The VAX and PDP-11 are compiled without Ethernet support. Versions with Ethernet support are available here. If you download the executables, you should download the source archive as well, as it contains the documentation and other supporting files. ● If your host system is Alpha/VMS, and you want Ethernet support, you need to download the VMS Pcap library and execlet here. SIMH implements simulators for: ● Data General Nova, Eclipse ● Digital Equipment Corporation PDP-1, PDP-4, PDP-7, PDP-8, PDP-9, PDP-10, PDP-11, PDP- 15, VAX ● GRI Corporation GRI-909 ● IBM 1401, 1620, 1130, System 3 ● Interdata (Perkin-Elmer) 16b and 32b systems ● Hewlett-Packard 2116, 2100, 21MX ● Honeywell H316/H516 ● MITS Altair 8800, with both 8080 and Z80 ● Royal-Mcbee LGP-30, LGP-21 ● Scientific Data Systems SDS 940 Also available is a collection of tools for manipulating simulator file formats and for cross- assembling code for the PDP-1, PDP-7, PDP-8, and PDP-11. -

The Small Computer Catalog

The new Sol-20 is unique. In the home. Home uses are limited It's the first small computer designed as only by your imagination. Regulate heat and a complete system. light to save fuel. Run a complex model Most small computers simply "grew railroad. Compute taxes. Play a variety of like Topsy" - a memory here, an expansion TV games, not only computer hockey and module there. They weren't conceived or tennis, but more interesting, more complex integrated to provide maximum efficiency at games such as TREK-8O, where your starship lowest possible cost. takes on a whole fleet of Klingons. Several Sol-20, a true breakthrough in small sophisticated TV games come with the computer systems, includes all the essential Sol-20. And you can even design your own. elements as standard equipment — central At the office. Use it as a fullfledged processor, memory, keyboard and display, business computer. Use it to compose and software, a power supply, and appropriate edit letters electronically, store and retrieve packaging. mailing lists, process orders, maintain There are no "surprises." You don't journals and general ledgers, and produce have to buy expensive peripheral equipment statements and reports. to make it run. Its own keyboard and In the lab. Use Sol to reduce and "smart" terminal are built-in. analyze data statistically, control lab Use it without being a programming equipment, prepare graphics, and fit curves. expert. Sol-20 frees your time and expands your In fact, you can operate it efficiently without overall capability. any prior computer experience. In schools and universities. -

The Tarbell Cassette Interface

THE TARBELL CASSETTE INTERFACE Plugs directly into ALTAI R * 8800 or IMSAI 8080 Computer. Serial-Parallel and Parallel-Serial Conversion performed on board. It's fast - Up to 540 bytes per second (2200 bits per inch) with high-quality cassette recorder. 187 bytes per second (800 bits per inch) suggested s.tandard with medium quality ($39.95) recorder. 27 bytes per second (with modification) for Kansas City format. 1000 bytes per second @ 10 inches per second with PHI-DECK. Encoding method - Phase encoded self-clocking method requires only one channel, and withstands large amounts of wow and flutter. Has been used in the computer industry for many years. Can also be used to generate and detect Kansas City format tapes \~. ith small mod ification. Will work with most audio cassette recorders. Has been used with reel-reel tape recorders. Can easily be adapted to automatically (software) controlled digital cassette units. The J. C. Penny #6536 is presently being recommended ($39.95). Suggested tape is Scotch Low-Noise, High-Density audio tape. The device code (address) to which the interface responds is selectable in increments of 4 by an on- board dip-switch. '. Four extra status lines are available to read external conditions. Four extra control lines are available, which may be used to drive relays for extra cassette units, start stop control, or controlled cassette drives, such as the PHI-DECK. Two spare IC slots are provided on the board to do your own thing. Software provided includes input/output driver routines, bootstrap, read-only memory program, and a ' BASIC program for saving and loading data. -

Micro Computing

Micro computing Thomas J. Bergin ©Computer History Museum American University Context…. • What was going on in the computer industry in the 1970s? – Mainframes and peripherals – Minicomputers and peripherals – Telecommunications – Applications, applications, applications – Operating systems and programming languages And the answer is…. • Everything!!! – Mainframes from small to giant – Supercomputers (many varieties) – Minicomputers, Super Minis, tiny Minis – Networks, WANS, LANS, etc. – Client Server Architectures – 2nd and 3rd generation applications: • Executive Information Systems • Decision Support Systems, etc. And into this technologically rich soup of computing, comes the: • Microprocessor • Microcomputer • New Operating Systems • New Operating Environments • Economics • New Users, New Users, New Users, New Users, New Users, New Users, New Users Intel • Robert Noyce, Gordon Moore, and Andrew Grove leave Fairchild and found Intel in 1968 – focus on random access memory (RAM) chips • Question: if you can put transistors, capacitors, etc. on a chip, why couldn’t you put a central processor on a chip? Enter the hero: Ted Hoff • Ph.D. Stanford University: Electrical Engineering – Semiconductor memories; several patents • Intel's 12th employee: hired to dream up applications for Intel's chips • Noyce wanted Intel to do memory chips only! • 1969: ETI, a Japanese calculator company -- wants a chip for a series of calculators The Microprocessor • ETI calculator would cost as much as a mini • "Why build a special purpose device when a general purpose device would be superior?" • Hoff proposed a new design loosely based on PDP-8: the Japanese weren't interested! • October 1969, Japanese engineers visit Intel to review the project, and agree to use the I 4004 for their calculator. -

Mise En Page 1

Publicité du Micral N premier micro-ordinateur de l’histoire informatique. National Computer Exhibition, Chicago, mai 1974. 1 Table des matières R2E. MICRAL-N, 1974. ................................................................................................................ 4 Des premiers calculateurs à la micro-informatique .................................................................... 6 Apparition de l’électronique pendant la Seconde guerre mondiale ............................................. 6 Domination nord–américaine dans la course aux gros ordinateurs ............................................. 6 Réaction française avec le plan calcul du Général de Gaulle ...................................................... 7 Course à la miniaturisation remportée brillamment par la France. ......................................... 7 Le Micral N : premier micro-ordinateur, 1972. ........................................................................... 8 Utilisation de l’Intel 8008 : la première carte micro-processeur ................................................. 9 La mémoire MOS......................................................................................................................... 9 François Gernelle, père des micro-ordinateurs (1972) et des ordinateurs portable (1977) ........ 10 Le succès du Micral et ses suiveurs nord-américains ............................................................... 10 3 ans d’avance sur I.B.M, 1975. ............................................................................................... -

ALTAIR 8800 / IMSAI 8080 Replacement CPU Project Josh

ALTAIR 8800 / IMSAI 8080 Replacement CPU Project Josh Bensadon June 5, 2014 Toronto Canada I cannot thank everyone by name or else I may forget someone, but you know who you are and thank you for your help and friendship. Special Thanks to everyone at the N8VEM group for their endless help and wonderful ideas that broadened the scope of this project. Extra Special Thanks to Andrew Lynch for his hard work to build and distribute the boards in the N8VEM realm. Only after doing similar work did I realize how much labour is involved. Also Extra Special Thanks to John Monahan for all his hard work building www.S-100computers.com Introduction Thank you for your interest and participation in this project. It drew on several skills and took many hours to bring it to this point. As an electronics hobbyist, I enjoy the roots of my interest as formed by endless hours of studying Popular Electronics and Radio Electronics magazines from the 70’s and 80’s. Recently, I’ve been taking a larger interest in the history of personal computers. As such, I would like to include a short history of this project board. Table of Contents Introduction ........................................................................................................... 2 Table of Contents .................................................................................................. 2 Short History ......................................................................................................... 3 Features ................................................................................................................ -

Integrated Circuits in and Under the Microscope

INTEGRATED CIRCUITS IN AND UNDER THE MICROSCOPE Michael W. Davidson Institute of Molecular Biophysics and Center for Materials Research and Technology, The Florida State University, Tallahassee, Florida 32306 Keywords: Photomicrography, reflected differential interference contrast microscopy, integrated circuits, and microprocessors. P erhaps no single technology has produced such a widespread impact on science as the current revolutionary developments occurring in integrated circuit design and fabrication. Integrated circuits are now found in virtually every piece of scientific equipment on the market and new upgrades of existing circuitry are being released at an amazing rate. The most sophisticated members of the integrated The complex electronics involved with transmis- circuit family are microprocessors that serve as the sion and scanning electron microscopy led, early on, central processing units of modern calculators and to the widespread use of microprocessors in these computers. Microprocessors have found their way instruments. Only recently, however, has the micro- into a myriad of everyday appliances such as radio, processor been utilized as an aid to light microscopy. television, refrigerators, stoves, microwaves ovens, Many modern light microscopes are equipped with automobiles, motorcycles, electronic watches, in-camera light detection systems that feed illumina- cameras, bicycle, odometers, and home security tion intensity information to a microprocessor that, in systems. In the scientific arena, microprocessors are turn, calculates exposure times. As time goes on, the now found in such simple instruments as pH meters, microprocessor will find increasingly more complex thermometers, balances, pipettes, and even the simple tasks to perform in light microscopy. Nikon has light microscope. recently introduced the Microphot-FXA/L light Microscope Technology & News 1 microscope that is almost entirely controlled by a 16- design, the more circuits can be packed onto a wafer.