SONET OC-48 Transceiver

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Smart Speakers & Their Impact on Music Consumption

Everybody’s Talkin’ Smart Speakers & their impact on music consumption A special report by Music Ally for the BPI and the Entertainment Retailers Association Contents 02"Forewords 04"Executive Summary 07"Devices Guide 18"Market Data 22"The Impact on Music 34"What Comes Next? Forewords Geoff Taylor, chief executive of the BPI, and Kim Bayley, chief executive of ERA, on the potential of smart speakers for artists 1 and the music industry Forewords Kim Bayley, CEO! Geoff Taylor, CEO! Entertainment Retailers Association BPI and BRIT Awards Music began with the human voice. It is the instrument which virtually Smart speakers are poised to kickstart the next stage of the music all are born with. So how appropriate that the voice is fast emerging as streaming revolution. With fans consuming more than 100 billion the future of entertainment technology. streams of music in 2017 (audio and video), streaming has overtaken CD to become the dominant format in the music mix. The iTunes Store decoupled music buying from the disc; Spotify decoupled music access from ownership: now voice control frees music Smart speakers will undoubtedly give streaming a further boost, from the keyboard. In the process it promises music fans a more fluid attracting more casual listeners into subscription music services, as and personal relationship with the music they love. It also offers a real music is the killer app for these devices. solution to optimising streaming for the automobile. Playlists curated by streaming services are already an essential Naturally there are challenges too. The music industry has struggled to marketing channel for music, and their influence will only increase as deliver the metadata required in a digital music environment. -

Applied Voice Execution: a Handbook for Marketing and Business Leaders TABLE of CONTENTS

Applied Voice Execution: A handbook for marketing and business leaders TABLE OF CONTENTS 00 INTRODUCTION 03 01 FINDING OUR VOICE 04 02 TALK ISN’T CHEAP 07 03 VOICE IN THE DRIVER’S SEAT 11 04 SAY VS. SWIPE 15 05 BRAND VOICE 18 06 WHAT CAN YOU DO TO GET READY? 21 07 LET’S TALK 24 APPLIED VOICE EXECUTION 2 00 INTRODUCTION In a crowded Seattle conference hall, a nervous IBM developer stood in front of dozens of reporters and spoke slowly and deliberately into a hand-held microphone: “Six, seven, eight, plus, two, three, four…” he began, and the rapt audience watched in wonder as his “voice recognition machine” – dubbed Shoebox because of its size – typed each number on a thin strip of paper and tallied his equation. It was the 1962 World’s Fair, and the world had just gotten its first see if it’s the delivery driver at your door, all without ever lifting glimpse of Alexa’s earliest ancestor, complete with a 16-word a finger. No longer fantasy or fad, the voice market has become vocabulary 1. Fast forward to the 2018 Consumer Electronics a $600M juggernaut that is reshaping consumer behavior and Show (CES)—a modern-day equivalent of the World’s Fair—and presenting retailers with a powerful opportunity to drive loyalty it’s stunning just how far Shoebox’s progeny have come. The to their brand, and dollars to their bottom line. The implications— human voice can now control myriad devices and services, and the impending disruption for businesses and brands—cannot enabling you to start the laundry, adjust the room temperature, be overstated. -

Apple's Iphone Launch: a Case Study in Effective Marketing

Apple's iPhone Launch: A Case Study in Effective Marketing Kyle Mickalowski, Augustana College Mark Mickelson, Augustana College Jaciel Keltgen, Augustana College ABSTRACT When CEO Steve Jobs announced in January 2007 that Apple would be releasing a revolutionary iPhone five months hence, consumers waited with bated breath for a phone that would deliver all the features of their iPods as well as a smart phone. Anticipation grew, just as Jobs knew it would, as June approached. The launch would become one of the most heralded technological product splashes Apple, known for its masterful media build-up, had ever planned. How the iPhone was developed, priced, promoted, and distributed is lesson for marketers around the world. Apple investors were pretty happy with the outcome as well. INTRODUCTION One year after Apple Inc. CEO Steve Jobs announced the company’s industry-changing iPhone on January 9, 2007, at the Macworld convention in San Francisco, the share price of Apple’s stock has more than doubled to a January 9, 2008, value of $179.40 (See Chart 1). This stock price incorporates all of Apple’s business, but a large part of the rise in value can be attributed to the launch of the cutting-edge iPhone, of which four million have already been sold through mid-January 2008 (Carew, 2008). Based on this simple observation of the stock price, the iPhone can so far be declared a success, at least from a shareholder standpoint. This paper will explore both the pre- and post-launch activities surrounding the iPhone to explain why it was such a success for the stockholders and why Apple’s reputation for unparalleled marketing success is deserved. -

Apple Identity Guidelines for Channel Affiliates and Apple-Certified Individuals

Apple Identity Guidelines For Channel Affiliates and Apple-Certified Individuals March 2018 The Apple identity is a seal of approval and a promise of excellence. When you are authorized or certified in your area of business or expertise, you also represent Apple. By following these guidelines, you reap the benefits of the Apple identity and contribute to its strength. Apple requirements The Apple channel signatures and graphics described in these guidelines are for use only by current Apple channel affiliates who have signed the Apple Authorized Reseller Agreement and by individuals with a current Apple certification. Apple channel affiliates and Apple-certified individuals must follow these guidelines when publicizing their relationship with Apple in communications. Apple reserves the right to withdraw permission to use an Apple channel signature at any time if the use of the signature is inconsistent with these guidelines or is otherwise deemed inappropriate by Apple. Apple channel signatures cannot be used in connection with any communications that do not meet the criteria outlined in the Apple Authorized Reseller Agreement or Apple Certification Agreement. Apple channel affiliates and Apple-certified individuals must comply with these guidelines, notwithstanding anything to the contrary in the “Guidelines for Using Apple Trademarks and Copyrights” at www.apple.com/legal/intellectual-property/ guidelinesfor3rdparties.html. Apple Identity Guidelines for Channel Affiliates and Apple-Certified Individuals March 2018 2 Contents Apple Sales Web -

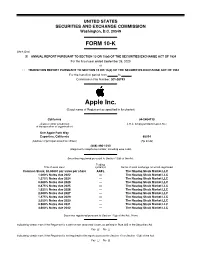

Apple Annual Report 2020

Apple Annual Report 2020 Form 10-K (NASDAQ:AAPL) Published: October 30th, 2020 PDF generated by stocklight.com UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-K (Mark One) ☒ ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended September 26, 2020 or ☐ TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to . Commission File Number: 001-36743 Apple Inc. (Exact name of Registrant as specified in its charter) California 94-2404110 (State or other jurisdiction (I.R.S. Employer Identification No.) of incorporation or organization) One Apple Park Way Cupertino, California 95014 (Address of principal executive offices) (Zip Code) (408) 996-1010 (Registrant’s telephone number, including area code) Securities registered pursuant to Section 12(b) of the Act: Title of each class Trading symbol(s) Name of each exchange on which registered Common Stock, $0.00001 par value per share AAPL The Nasdaq Stock Market LLC 1.000% Notes due 2022 — The Nasdaq Stock Market LLC 1.375% Notes due 2024 — The Nasdaq Stock Market LLC 0.000% Notes due 2025 — The Nasdaq Stock Market LLC 0.875% Notes due 2025 — The Nasdaq Stock Market LLC 1.625% Notes due 2026 — The Nasdaq Stock Market LLC 2.000% Notes due 2027 — The Nasdaq Stock Market LLC 1.375% Notes due 2029 — The Nasdaq Stock Market LLC 3.050% Notes due 2029 — The Nasdaq Stock Market LLC 0.500% Notes due 2031 — The Nasdaq Stock Market LLC 3.600% Notes due 2042 — The Nasdaq Stock Market LLC Securities registered pursuant to Section 12(g) of the Act: None Indicate by check mark if the Registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. -

Executive Summary Apple Inc Is One of the Most Iconic Companies of the Recent Decade

Rutgers Business School Applied Portfolio Management Analyst: Alexander Berila Executive summary Apple Inc is one of the most iconic companies of the recent decade. Apple has not only been developing and selling great products. More importantly the company has been building an incredible platform and an ecosystem for its loyal users within which it could further sell apps and services. The company is not immune to general market trends and some of the product sales are slowing down either due to markets maturing (e.g. smartphones) or due www. nasdaq.com to a general industry decline (e.g. music players and computers). Apple has a formidable competition within well established and well financed companies such as Alphabet, Samsung, Amazon, HP as well as newcomers from China like Huawei and Xiaomi. Despite strong competition the company managed to grow and thrive within its industries and enjoys one of the best balance sheets and financial metrics among its peers. Moat Apple moat is built on a combination of economies of scale, great products protected by a wall of patents, very strong brand recognition and a unique ecosystem which holistically links everything together. Valuation In my opinion, Apple stock is undervalued. Stock has fallen over 19% in the last 12 month compared to a 1.5% fall for S&P 500. Currently, AAPL trades at TTM P/E of 11.25 which is lower than 5 year average P/E ratio of 13.8. I believe www. finance.yahoo.com that market is incorrectly pricing the value of not only Apple’s $164b of cash piled in LT equities but also of earning potential of existing and new products. -

Grant 2013.005

ao\ 3. oo5 Student Technology Fee r~ Grant Proposal Request Form Fiscal Year 2012-13 Northwestern State University ofLouisiana ALL BLANKS MUST BE FILLED COMPLETELY Prepared by: Kirstin Riehl & Brett Garfinkel For: Kirstin Riehl & Brett Garfinkel Department/Unit: Theatre & Dance College: Creative & Performing Arts Campus: Natchitoches Which NSTEP Goals/Objectives does this project meet? Objectives 1.2.6,8 & 9 Requested equipment will be located/installed/housed? Building Old CAPA Room 132 & 109 Does the department requesting funding receive lab fees? YES Are department property policies and procedures in place for requested equipment? Yes Which individual will be responsible for property control of the requested equipment? Brett Garfinkel Signatui~% .,)271E G?;;:;zC.nate: 10/30112 Proposal Requested Amount: $17,3 86.19 Budget Attached: YES Proposal delivered to Student Technology located in Watson Library, Room 113 Date: 10/30112 The proposal must include all specifications, description, model number, quotation, cost, state contract number, and vendor for each item. If the proposal does not include all requested information, it will be returned. 1. Describe target audience. -Theatre & Dance Majors and Minors are the primary target audience, especially those earning a BS degree in Theatre with a concentration in Dance and Musical Theatre. Students use the space for class as well as rehearsals for their own projects. (Approximately 120 students) -Secondary target audience would be student groups, organizations and the entire NSU student -

Class Action Complaint 1 2 3 4 5 6 7 8 9 10 11

Case 5:18-cv-02813 Document 1 Filed 05/11/18 Page 1 of 44 1 Daniel C. Girard (State Bar No. 114826) Jordan Elias (State Bar No. 228731) 2 Adam E. Polk (State Bar No. 273000) 3 Simon S. Grille (State Bar No. 294914) GIRARD GIBBS LLP 4 601 California Street, Suite 1400 San Francisco, California 94108 5 Telephone: (415) 981-4800 6 [email protected] [email protected] 7 [email protected] [email protected] 8 9 Counsel for Plaintiffs 10 [Additional Counsel on Signature Page] 11 12 UNITED STATES DISTRICT COURT 13 NORTHERN DISTRICT OF CALIFORNIA 14 ZIXUAN RAO and KYLE BARBARO, Case No. 15 individually and on behalf of all others similarly 16 situated, CLASS ACTION COMPLAINT FOR: 17 Plaintiffs, 1. Breach of Express Warranty; 2. Breach of the Covenant of Good Faith and 18 v. Fair Dealing; 19 3. Breach of the Implied Warranty of APPLE INC., Merchantability; 20 4. Violation of the Magnuson-Moss Warranty 21 Defendant. Act, 15 U.S.C. § 2301, et seq.; 5. Violation of the Song-Beverly Consumer 22 Warranty Act; 6. Violation of California’s Unfair 23 Competition Law; 24 7. Violation of California’s Consumer Legal Remedies Act; and 25 8. Fraudulent Concealment. 26 DEMAND FOR JURY TRIAL 27 28 CLASS ACTION COMPLAINT www.girardgibbs.com Case 5:18-cv-02813 Document 1 Filed 05/11/18 Page 2 of 44 1 Plaintiffs Zixuan Rao and Kyle Barbaro, individually and on behalf of all others similarly 2 situated, allege as follows against Defendant Apple Inc. 3 SUMMARY OF THE ACTION 4 1. -

Hardware Universe V 4.7 User Guide

Hardware Universe v 4.7 User Guide June 2015 ©2015 NetApp, Inc. All rights reserved. No portions of this document may be reproduced without prior written consent of NetApp, Inc. Specifications are subject to change without notice. NetApp, the NetApp logo, Go further, faster is a trademark or registered trademark of NetApp, Inc. in the United States and/or other countries. All other brands or products are trademarks or registered trademarks of their respective holders and should be treated as such. WP-215-0728_A0 TABLE OF CONTENTS 1 Hardware Universe Overview .............................................................................................................. 4 1.1 Requirements ..................................................................................................................................................4 1.2 Supported NetApp Software Versions ............................................................................................................4 1.3 Acronyms ........................................................................................................................................................5 2 What’s New in Hardware Universe version 4.7? ............................................................................... 7 2.1 All Flash FAS Rebranding ...............................................................................................................................7 2.2 StorageGRID WebScale Appliance ................................................................................................................7 -

Form 10-K from 2020

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-K (Mark One) ☒ ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended September 26, 2020 or ☐ TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to . Commission File Number: 001-36743 Apple Inc. (Exact name of Registrant as specified in its charter) California 94-2404110 (State or other jurisdiction (I.R.S. Employer Identification No.) of incorporation or organization) One Apple Park Way Cupertino, California 95014 (Address of principal executive offices) (Zip Code) (408) 996-1010 (Registrant’s telephone number, including area code) Securities registered pursuant to Section 12(b) of the Act: Trading Title of each class symbol(s) Name of each exchange on which registered Common Stock, $0.00001 par value per share AAPL The Nasdaq Stock Market LLC 1.000% Notes due 2022 — The Nasdaq Stock Market LLC 1.375% Notes due 2024 — The Nasdaq Stock Market LLC 0.000% Notes due 2025 — The Nasdaq Stock Market LLC 0.875% Notes due 2025 — The Nasdaq Stock Market LLC 1.625% Notes due 2026 — The Nasdaq Stock Market LLC 2.000% Notes due 2027 — The Nasdaq Stock Market LLC 1.375% Notes due 2029 — The Nasdaq Stock Market LLC 3.050% Notes due 2029 — The Nasdaq Stock Market LLC 0.500% Notes due 2031 — The Nasdaq Stock Market LLC 3.600% Notes due 2042 — The Nasdaq Stock Market LLC Securities registered pursuant to Section 12(g) of the Act: None Indicate by check mark if the Registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. -

Brand Guidelines Final

Apple Affiliate Program Brand and Photography Guidelines Content Overview 3 Promoting apple.com 4 Apple Logo 5 Apple Web Banners Best Practice 6 Design Mistakes to Avoid 7 Layout Mistakes to Avoid 8 Apple Product Photography Overview 9 Best Practice 10 Mistakes to Avoid 11 Your Content 12 Linking to apple.com 13 Using Trademarks and Credit Lines 14 Prohibited Activity 16 More Information 16 Apple Affiliate Program Brand and Photography Guidelines 2 Overview Apple.com is the world’s #1 resource for purchasing Apple products online. When your company is approved to use an Apple-provided asset, such as a web banner or badge to direct your customers to apple.com, it’s important to use those assets as directed and approved in these guidelines. These guidelines are for use by companies that To represent Apple correctly on websites, mobile promote Apple and link directly from their channels, advertising, and other marketing website, mobile site, or app to shop on communications, these guidelines should be apple.com or the Apple Store app. followed wherever an Apple banner, badge, or text link to apple.com is used. Apple Affiliate Program Brand and Photography Guidelines 3 Promoting apple.com Examples of scenarios to avoid When describing shopping with Apple, the Scenarios to Avoid following phrases can be used: Here are some common mistakes to avoid when Shop apple.com you promote Apple product offers in your communications: Shop the Apple website Shop Apple online • Do not incorporate Apple assets (Apple Shop the Apple Store app banners, the Apple logo, or Apple product Shop with Education Pricing photography) in headlines or body copy. -

Why Apple May Have Jumped the Gun with Airpods Aneri Pattani, Special to CNBC.Com

Why Apple may have jumped the gun with AirPods Aneri Pattani, special to CNBC.com Apple is confident it made the right decision to remove the wired headphone jack on the iPhone 7 and launch the wireless AirPods, but it could take some time for the new Apple product innovation to prove to consumers it's ready for prime time in the premium headphone market. Several audio executives told CNBC the AirPods can't quickly catch up to wired headphones, because of failings in three key attributes — and appearance isn't among them. Power efficiency, audio quality and noise cancellation technology are areas in which the AirPods are limited compared with current top-tier mobile audio options. Among the new device's flaws is that wireless functionality lasts for only five hours per charge, said Mike Culver, president of Danish audio company Libratone, which is launching Lightning compatible earbuds next month. (The AirPods do come with a portable charging case that can provide more than 24 hours of battery life.) AirPods also lack the ability to produce high-resolution audio quality, said Dunja LaRosa, director and head of mobile audio at Sony Electronics. LaRosa said the future is likely in wireless, but technology hasn't progressed enough to put the cord to rest and achieve high- resolution audio. "In general, we do see the market going for wireless or Bluetooth devices more over the last couple years," said LaRosa. "But the majority of the market right now still comes from wired solutions." In the world of premium headphones, audio executives mentioned the lack of active noise cancellation as a major drawback.