Electronic Design Automation Tools Part 2 by Christopher Henderson This Article Provides an Overview of the Electronic Design Automation (EDA) Design Tools

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Aras Innovator - Connectors Support Matrix

Aras Innovator - Connectors Support Matrix MCAD Tools Autocad Autodesk Inventor CATIA V5 Dassault CATIA V6 SolidWorks Creo PTC Creo Direct NX Siemens Solid Edge PDM/PLM Autodesk Vault Altium Vault Enovia Dassault SmarTeam SolidWorks PDM Pro Oracle Agile PTC Windchill SAP PLM Siemens Teamcenter SAP PLM ERP IBM DOORS ORACLE ERP ERP SAP ERP V6 ERP HANNA QAD QAD/Mfg Dynamics NAV Microsoft Dynamics GP Dynamics AX Oracle Netsuite BIM Tools Revit AutoDesk 1 January 2021 Aras Innovator - Connectors Support Matrix ECAD Tools AutoCAD Electrical (Autodesk) Electrical CAD AutoDesk AutoCAD Electrical (Autodesk) Electrical Librarian SolidWorks (Dassault) Electrical Dassault SolidWorks (Dassault) Electrical Librarian Designer Electronic Board Layout CAD Designer Electronic Schematic CAD Designer Electronic Librarian Altium Nexus Server Agent Nexus Electronic Librarian Concord Electronic Librarian Concord PCB Electronic Librarian Xpedition Capture (Mentor Graphic) Electronic Schematic CAD PADS Standard Electronic Schematic CAD Xpedition Electronic Board Layout CAD PADS Standard Electronic Board Layout CAD Xpedition & PADS Professional Electronic Librarian PADS Standard Electronic Librarian Mentor PADS Professional Electronic Schematic CAD PADS Professional Electronic Board Layout CAD Capital Electrical Capital Electrical Librarian EDM Server Agent EDM Librarian Allegro HDL Electronic Schematic CAD OrCAD Capture CIS Electronic Schematic CAD Cadence Allegro & OrCAD Electronic Board Layout CAD Allegro HDL Electronic Librarian OrCAD Electronic Librarian Zuken E3.series (Zuken) Electrical Wiring Layout CAD Elcad Electrical CAD Elcad Electrical Librarian Aucotec Engineering Base Electrical CAD Engineering Base Electrical Librarian EPLAN Electric Electrical CAD EPLAN EPLAN Electric Electrical Librarian Pulsonix Electronic Board Layout CAD Pulsonix Pulsonix Electronic Schematic Layout CAD Pulsonix Electronic Librarian 2 January 2021. -

LH1546ADF Datasheet (PDF)

LH1546ADF, LH1546ADFTR www.vishay.com Vishay Semiconductors 1 Form A Solid-State Relay (Normally Open) FEATURES • Isolation test voltage 5300 VRMS • Typical RON 22 Ω A 1 4 S1 • Load voltage 350 V • Load current 120 mA C 2 3 S2 • Clean bounce free switching • Current limit protection • Low power consumption • Material categorization: for definitions of compliance please see www.vishay.com/doc?99912 DESCRIPTION APPLICATIONS The LH1546AD is a single channel solid state relay in a • General telecom switching 4 pin SMD package. It is a SPST normally open switch (1 Form A) that replaces electromechanical relays in many • Metering applications. It is constructed using a GaAlAs LED for • Security equipment actuation control and MOSFET switches for the output. • Instrumentation In addition, it employs current-limiting circuitry to provide • Industrial controls overvoltage protection. • Battery management systems • Automatic test equipment AGENCY APPROVALS • UL1577, file no. E52744 ORDERING INFORMATION SMD LH1546A##TR PART NUMBER ELECTR. PACKAGE TAPE AND VARIATION CONFIG. REEL > 0.1 mm PACKAGE UL SMD-4, tubes LH1546ADF SMD-4, tape and reel LH1546ADFTR Rev. 1.8, 05-Jul-2018 1 Document Number: 83836 For technical questions, contact: [email protected] THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000 LH1546ADF, LH1546ADFTR www.vishay.com Vishay Semiconductors ABSOLUTE MAXIMUM RATINGS (Tamb = 25 °C, unless otherwise specified) PARAMETER CONDITION SYMBOL VALUE UNIT INPUT IRED continuous forward current IF 50 mA IRED reverse voltage VR 5V Input power dissipation Pdiss 80 mW OUTPUT DC or peak AC load voltage VL 350 V Continuous DC load current at 25 °C, I 120 mA bidirectional L SSR output power dissipation Pdiss 550 mW SSR Ambient temperature range Tamb -40 to +85 °C Storage temperature range Tstg -40 to +150 °C Soldering temperature t = 10 s max. -

Learning Openaccess Problem Areas Programmers Need to Understand Kevin Nesmith Chief Architect

Learning OpenAccess Problem Areas Programmers Need to Understand Kevin Nesmith Chief Architect June 25, 2014 Innova&on Through Collabora&ve R&D Overview • Why teach “Learning OpenAccess?” • Why OpenAccess? • Documentaon and training • ProBlems geng started • Uli?es • lib.defs (cds.lib) • Domains • Observers • Namespaces • Translators • Hierarchy • Some helpful tools – oaScript – oaDeBugging Suite • Who’s involved in this OpenAccess effort Innova&on Through Collabora&ve R&D 2 Why teach “Learning OpenAccess” at IEEE? Innova&on Through Collabora&ve R&D “ipsa sciena potestas est” • “Knowledge itself is power” (Sir Francis Bacon) • Knowing more about the inner workings of OpenAccess will make you more – Producve – Valuable • Improve your joB related proBlem solving skills • Reviewing what you already know keeps the informaon fresh in your Brain • Even if you only rememBer 1% from today, its more than what you knew yesterday Innova&on Through Collabora&ve R&D 4 Background of OpenAccess • mid 1990’s, SEMATECH created Chip Hierarchical Design System: Technical Data (CHDStd) • 1999 SEMATECH asked Si2 to take ownership of the CHDStd program to find a way to make is successful • This eventually lead to a new project called OpenAccess • To address concerns of CHDStd, a replacement for the CHDStd API was needed • Si2 put out a call for a technology contriBu?on • Cadence answered the call Innova&on Through Collabora&ve R&D 5 WHY OPENACCESS? Innova&on Through Collabora&ve R&D OpenAccess as a Concept • Eliminate translaon steps in the EDA flow • Prevent -

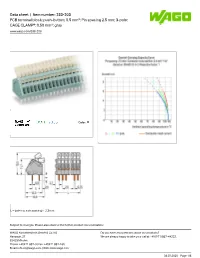

233-203 PCB Terminal Block; Push-Button; 0.5 Mm²; Pin Spacing 2.5 Mm; 3-Pole; CAGE CLAMP®; 0,50 Mm²; Gray

Data sheet | Item number: 233-203 PCB terminal block; push-button; 0.5 mm²; Pin spacing 2.5 mm; 3-pole; CAGE CLAMP®; 0,50 mm²; gray www.wago.com/233-203 Color: L = (pole no. x pin spacing) + 2.3 mm SubjectItem description to changes. Please also observe the further product documentation! WAGO Kontakttechnik GmbH & Co. KG Do you have any questions about our products? Hansastr. 27 We are always happy to take your call at +49 (571) 887-44222. 32423 Minden Phone: +49571 887-0 | Fax: +49571 887-169 Email: [email protected] | Web: www.wago.com 03.07.2020 Page 1/8 Data sheet | Item number: 233-203 www.wago.com/233-203 Item description Compact PCB terminal strips with CAGE CLAMP® connection and screwdriver actuation parallel or perpendicular to conductor entry Double solder pins for high mechanical Custom color combinations Data Electrical data Ratings per IEC/EN 60664-1 Ratings per IEC/EN 60664-1 Nominal voltage (III/3) 63 V Rated surge voltage (III/3) 2.5 kV Rated voltage (III/2) 160 V Rated surge voltage (III/2) 2.5 kV Nominal voltage (II/2) 320 V Rated surge voltage (II/2) 2.5 kV Rated current 6 A Legend (ratings) (III / 2) ≙ Overvoltage category III / Pollution degree 2 Approvals per UL 1059 Rated voltage UL (Use Group B) 150 V Rated current UL (Use Group B) 4 A Approvals per CSA Rated voltage CSA (Use Group B) 150 V Rated current CSA (Use Group B) 4 A Connection data Connection technology CAGE CLAMP® Actuation type Push-button Solid conductor 0,08 … 0,5 mm² / 28 … 20 AWG Fine-stranded conductor 0,08 … 0,5 mm² / 28 … 20 AWG Fine-stranded conductor; with insulated ferrule 0,25 mm² Fine-stranded conductor; with uninsulated ferrule 0,25 mm² SubjectStrip length to changes. -

Kretskorsdesign

Kretskorsdesign Schema Nätlista Nätlista Layout Simulering Schema ● Beskriver grafiskt vilka komponenter som finns i kretsen och hur de är sammankopplade. ● Behöver inte ha någon koppling till hur kretsen ser ut fysiskt. Nätlista ● Länken mellan den grafiska beskrivningen i schemat och layout eller simulering. ● Mer eller mindre automatiskt genererad textfil med anslutningarna mellan komponenters pinnar. ● Nät kan ges beskrivande namn i schemat, tex ”GND” ● Nät med samma namn är sammankopplade. Kan användas för att få ett tydligare schema. Layout ● Fysisk beskrivning av kretsen. ● Får information om vilka komponenter(och vilken fysisk kapsel) samt anslutningar mellan dessa från nätlistan. ● Hur komponenterna placeras på kortet och hur de fysiska ledningarna ser ut är upp till den som gör layouten. Vilka program finns det? ● Det finns många alternativ... ● Eagle – Historiskt väldigt populärt. – Gratisversion upp till 2 lager och 80x100mm. – Större kort och/eller kommersiellt bruk numera endast via abonnemang. ● Diptrace – Begränsningar på antalet pinnar, 300 eller 500 för ”non-profit”. – 1000 pinnar för 125$ ”non-profit”, 395$ för motsvarande kommersiella version. Open source ● KiCad – Har utvecklats mycket senaste åren. – Fokus har varit på att förbättra layout-delen. – Nästa version kommer att innehålla b.l.a simulering(ngspice) och förbättringar i schema-delen. ● gEDA/PCB – Lite mer löst sammanhållna verktyg. – PCB är förmodligen det äldsta open-source layoutprogrammet som är aktivt, första versionen kom 1990 för Atari Online ● Easyeda – Schema/layout/simulering. – Tillverkar kort, men genererar även gerberfiler. ● Upverter ● Circuitmaker – Från Altium. – Installeras lokalt, men kräver att man är uppkopplad. Tillverkning Layout Gerber, borr-fil Gerber ● En fil per lager. – Filändelsen brukar indikera vilket lager det ska vara ● En eller två borrfiler(pläterade/opläterade hål). -

An Introduction to Openaccess Scripting

An Introduction to OpenAccess Scripting James D. Masters Intel Corp Design Automation Conference June 6, 2011 1 What is it? • Standalone direct interface to OpenAccess (OA) – No dependencies beyond OA and no licensing fees – Performance and memory usage is good for a scripting language • Matches C++ API with some melding to native language features – Existing C++ API documentation can be referenced – Auto conversions to/from native types (e.g. strings, integers, floats) • Includes convenience functions to reduce code and improve productivity – More natural interface; e.g. native array of (1.234, 9.876) instead of oaPoint(1234, 9876) 2 How does it work? Perl API Python API Ruby API Tcl API C# API Language-Specific Bindings Type Mapping Type Mapping Type Mapping Type Mapping Type Mapping Common Wrapper Architecture Interface Common SWIG Framework OA API C++ Programming Interface • Common interface through SWIG ensures cross-language consistency and reuse • All languages interface OA through the official OA API 3 Basic type mapping • Some basic OA types are mapped to native types in the target language Perl Python Ruby Tcl C# oaBoolean integer bool Boolean integer bool oa*Int integer int Fixnum integer int, uint, long,ulong oaFloat/Double Float float Float float float/double oaString string string String string string oaArray array array Array list IList<T> oaTime oaTime oaTime Time oaTime DateTime oaTimestamp integer int Fixnum integer uint oaComplex oaComplex complex OaComplex oaComplex oaComplex oaPoint oaPoint/array oaPoint/array OaPoint/Array -

Pulsonix Users Guide Pulsonix Users Guide 3

Pulsonix Design System Users Guide 2 Pulsonix Users Guide Pulsonix Users Guide 3 Copyright Notice Copyright ã WestDev Ltd. 2001-2018 Pulsonix is a Trademark of WestDev Ltd. All rights reserved. E&OE Copyright in the whole and every part of this software and manual belongs to WestDev Ltd. and may not be used, sold, transferred, copied or reproduced in whole or in part in any manner or in any media to any person, without the prior written consent of WestDev Ltd. If you use this manual you do so at your own risk and on the understanding that neither WestDev Ltd. nor associated companies shall be liable for any loss or damage of any kind. WestDev Ltd. does not warrant that the software package will function properly in every hardware software environment. Although WestDev Ltd. has tested the software and reviewed the documentation, WestDev Ltd. makes no warranty or representation, either express or implied, with respect to this software or documentation, their quality, performance, merchantability, or fitness for a particular purpose. This software and documentation are licensed 'as is', and you the licensee, by making use thereof, are assuming the entire risk as to their quality and performance. In no event will WestDev Ltd. be liable for direct, indirect, special, incidental, or consequential damage arising out of the use or inability to use the software or documentation, even if advised of the possibility of such damages. WestDev Ltd. reserves the right to alter, modify, correct and upgrade our software programs and publications without notice and without incurring liability. Microsoft, Windows, Windows NT and Intellimouse are either registered trademarks or trademarks of Microsoft Corporation. -

EDA Scripting Unleashed: Real-Life Examples Using Oascript and Oaxpop

EDA Scripting Unleashed: Real-Life Examples Using oaScript and oaxPop James D. Masters Intel Corp Si2CON October 6, 2015 1 Agenda • oaScript overview • oaxPop overview • Intel’s experience with oaScript and oaxPop – Framework bundle of required packages – Performance observations – Density Calculator application – Methodology Checker application • oaScript/oaxPop Roadmap • Summary 2 oaScript overview • Standalone direct interface to OpenAccess (OA) using Perl, Python, Ruby, or Tcl – Enables rapid development of powerful OA-based software – Performance and memory usage is mostly comparable to that of a C++ application (a few exceptions will be mentioned later) • Matches OA C++ API very closely – Existing C++ API documentation can be referenced – Auto conversion of types between C++ and scripting language • Includes convenience functions to reduce code and improve productivity • Initiated in 2009, and refined over the past 6 years in Si2’s oaScript working group (code base is stable) 3 oaScript interaction with OA API (via SWIG) Language-Specific Perl API Python API Ruby API Tcl API Bindings Type Mapping Type Mapping Type Mapping Type Mapping Common Wrapper Architecture Interface Common SWIG Framework C++ Programming OA API Interface • Uses the Simplified Wrapper and Interface Generator (SWIG) tool to expose C++ APIs to scripting languages – Common interface through SWIG ensures cross-language consistency and reuse – All languages interface OA through the official OA API 4 oaxPop overview • Provides high-speed polygon manipulation capabilities -

Pulsonix PCB Design

Pulsonix PCB Design Effortless PCB Layouts Pulsonix PCB Layout Construction Lines Pulsonix provides an expert design environment to get your boards Unique to Pulsonix, construction lines provide user-definable 'guide' produced fast with as little effort as possible.With unparalleled ease lines within your design. Use construction lines to create complex of use, Pulsonix provides a feature-rich toolset to get the job done board outlines or design items and to align irregular shapes.With efficiently. Everything in Pulsonix is logical, easy to setup and easy to their own layer, colour and style, construction lines are valuable for all use. Even complex design constraint rules can be easily defined using 2D creation without the need to import complex shapes from highly accessible dialogs. outside of your PCB design environment. Technology files for fast start-up True Mixed Technology Support Just like templates used for other desktop products, Pulsonix has a Technology is supported for standard plated through holes, surface unique system of technology files for fast start-up. Customise and mount devices/technologies, blind and buried vias and laser/plasma pre-define items such as Design rules, Layers, Materials, Spacing rules drilled micro-vias. Pads with slots or non-round holes are easily and Copper/Thermal rules as well as styles for text, tracks, pads, lines achieved using standard pad style definitions or custom pad shapes. to name a few. Company standards can be created in one file then used and shared by all Pulsonix users.Technology files can be created and updated as you design to create a master file containing all your design settings. -

Pulsonix Design System V11.0 Update Notes

Pulsonix Design System V11.0 Update Notes 2 Pulsonix Version 11.0 Update Notes Copyright Notice Copyright ã WestDev Ltd. 2000-2021 Pulsonix is a Trademark of WestDev Ltd. All rights reserved. E&OE Copyright in the whole and every part of this software and manual belongs to WestDev Ltd. and may not be used, sold, transferred, copied or reproduced in whole or in part in any manner or in any media to any person, without the prior written consent of WestDev Ltd. If you use this manual you do so at your own risk and on the understanding that neither WestDev Ltd. nor associated companies shall be liable for any loss or damage of any kind. WestDev Ltd. does not warrant that the software package will function properly in every hardware software environment. Although WestDev Ltd. has tested the software and reviewed the documentation, WestDev Ltd. makes no warranty or representation, either express or implied, with respect to this software or documentation, their quality, performance, merchantability, or fitness for a particular purpose. This software and documentation are licensed 'as is', and you the licensee, by making use thereof, are assuming the entire risk as to their quality and performance. In no event will WestDev Ltd. be liable for direct, indirect, special, incidental, or consequential damage arising out of the use or inability to use the software or documentation, even if advised of the possibility of such damages. WestDev Ltd. reserves the right to alter, modify, correct and upgrade our software programs and publications without notice and without incurring liability. -

Pycells for an Open Semiconductor Industry

PROC. OF THE 8th EUR. CONF. ON PYTHON IN SCIENCE (EUROSCIPY 2015) 3 PyCells for an Open Semiconductor Industry Sepideh Alassi∗†, Bertram Winter‡ F Abstract—In the modern semiconductor industry, automatic generation of pa- 2 DEVELOPMENT rameterized and recurring layout structures plays an important role and should be present as a feature in Electronic Design Automation (EDA)-tools. Currently these layout generators are developed with a proprietary programming language OpenAccess [OpenAccess] has been established as standard and can be used with a specific EDA-tool. Therefore, the semiconductor com- for storing design data in the semiconductor industry and panies find the development of the layout generators that can be used in all builds the foundation for interoperability of EDA-tools. Ope- state of the art EDA-tools which support OpenAccess database appealing. The nAccess is a file based database and manages logical design goal of this project is to develop computationally efficient layout generators with Python (PyCells), for ams AG technologies, that possess all the features of data (schematics) as well as artwork data (layout) for manu- comprehensive layout generators. facturing. The reference implementation for accessing design data within the database is written in C++. The company Index Terms—PyCells, Semiconductor, OpenAccess Ciranova (now acquired by Synopsys) developed a Python wrapper [PythonAPI] for the OpenAccess C++ class library with the goal to access and modify design data through 1 INTRODUCTION Python. Additionally, they provide an integrated development The number of companies active in modern semiconductor environment [SynopsysPyCellStudio] that enables interactive business is increasing every day which raises the demand for development and debugging of Python code, while the effects cheaper EDA-tools. -

INDIAN INSTITUTE of TECHNOLOGY GANDHINAGAR Ground Floor, Room No

INDIAN INSTITUTE OF TECHNOLOGY GANDHINAGAR Ground Floor, Room No. 111, Academic Block no. 3, Palaj, Gandhinagar - 382 355. Email id – [email protected] Website: www.iitgn.ac.in Date: 03.12.2019 Tender No.: IITGN/MAKERBHAVAN/NONCONS/2019-20/333 Last date: 23rd December, 2019 on/before 05:00 PM SUB: Invitation of sealed tender (two bids) for Supply and Installation of “Desktop PCB Prototyping Machine” as per details and specifications shown in the Annexure-I at IIT Gandhinagar Maker Bhavan. Dear Sir/Madam, Indian Institute of Technology Gandhinagar (IITGN) invites sealed tender (two bids) for Supply and Installation of “Desktop PCB Prototyping Machine” as per details and specifications shown in the Annexure-I on the following terms & conditions: 1. If the supplier/firm is manufacturer/authorized dealer/sole distributor of any item/equipment(s), the latest certificate to this effect should be attached. 2. The tender documents are to be submitted in two parts as Technical Offer and Financial offer: a.) The “Technical offer” should include the detailed specifications of main item/equipment and its accessories. All items should be numbered as indicated in the Annexure-I. The bidder should submit ‘Technical Compliance Report’ as per Annexure-II of the quoted item/equipment. b.) The financial offer should include the cost of main item/equipment and its accessories numbered as in Annexure-I. If there is any separate cost for installation etc. that should be quoted separately. The total cost should be quoted in words as well as figures (typed or printed). Amendment should be avoided. Amendments, if any, should be duly initialled, failing which the offers are liable to be rejected.