Compactflash® Memory Card Product Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Place Compactflash

SanDisk—the first name in A place CompactFlash. TO STORE High-performance SanDisk CompactFlash memory cards are fast, reliable, and let you do so much more with the devices your BIG that use them. With a PC Card adapter, almost anything with MEMORY CARD a PC card slot can use SanDisk CompactFlash memory cards, too. One thing is certain: if it has a place for a CompactFlash memory card, you should fill it with a SanDisk CompactFlash card available in capacities up to 96MB. To increase your storage capacity, visit a retail outlet Actual size. ideas that carries premium-quality SanDisk CompactFlash memory To transfer data between your digital camera or handheld PC cards and get one today. See the bigger, better picture. and a desktop computer, you should also consider the SanDisk To get the best results with a digital camera, you’ll want to A place to store your big ideas. ImageMate™ External Drive. The parallel port version connects SanDisk’s 10 million picture guarantee™ use its highest image quality setting. High image quality is If you really depend on your handheld PC, you know how to your computer’s parallel port. The USB vesion connects to Want a CompactFlash memory card that will last a lifetime? desirable because the images can be used in a wider variety important it is to back up your data. SanDisk CompactFlash your computer’s available USB port. It acts like a regular Insist on SanDisk. We’re the only company that guarantees of applications. They look better in print. They can be memory cards are the ideal solution. -

Multi-Card Reader/Writer Hi-Speed USB, 3.5" Bay Mount, 60-In-1 Part No.: 100915

Multi-Card Reader/Writer Hi-Speed USB, 3.5" Bay Mount, 60-in-1 Part No.: 100915 Converts an empty, unused PC bay into a digital content management center. The Manhattan Multi-Card Reader/Writer supports most card formats to easily download and transfer digital images and files from many of today’s popular flash memory cards. Compatible with up to 60 types of CompactFlash, Microdrive, Magicstor, Memory Stick, MagicGate, SecureDigital, Multimedia, XD and more, the Manhattan Multi-Card Reader/Writer quickly installs into a 3.5" bay. Convenience without the Media Device Access digital content without directly connecting the camera or other media devices to the computer. This convenient connection helps conserve battery power by eliminating the need to directly install a digital device to a desktop computer. A front-mount USB port expands power availability to recharge USB devices. Features: Convenient front-mount USB port Compatible with CompactFlash, Microdrive, Memory Stick, MagicGate, SecureDigital, Multimedia and XD Supports Automatic Card Detection and data transfer speeds up to 480 Mbps Eliminates need for direct connection of media device to save battery power Plug and play; hot-swappable — Windows and Mac compatible Three-Year Warranty Specifications: Standards and Certifications • USB 2.0 • USB 1.1 • CE • FCC • WEEE For more information on Manhattan products, consult your local dealer or visit www.manhattan-products.com. All names of products or services mentioned herein are trademarks or registered trademarks of their respective -

Capturemovemanipulates

CAPTUREMOVEMANIPULATESTORE Flash Memory Cards from Simpletech CompactFlash Secure Digital MultiMediaCard RS-MMC miniSD Flash Memory Cards from SimpleTech Capture your digital photos, music, and files with SimpleTech high-speed flash FLASHMEMORYCARDS memory cards. CompactFlash CompactFlash (CF) flash memory cards are the most popular form factor of flash storage used in consumer devices today. CF cards are ideal storage solutions for digital cameras, MP3 players, PDAs, palmtops, and handheld PCs. Features • Low power consumption • Compatible with all CF devices • Hot Swappable • CFA and PCMCIA Compliant • Highest Capacity Available using IC TowerTM Chip Stacking Capacities 32MB-4GB Dimension 1.69" (w) x 1.43" (l) x 0.13" (t) Weight 11.4g Interface ATA True IDE Operating Temperature 0o - 70o C Power 3.3V or 5V Operation Warranty Lifetime Secure Digital Secure Digital (SD) flash memory cards are next generation memory devices that offer a combination of high storage capacity, fast data transfer rates, great flexibility and excellent security. Features • Copyrights protection function • SD and SPI interface supported • Nonvolatile solid-state storage • Mechanical write protect switch Capacities 32MB - 1GB Dimension 0.94" (w) x 1.26" (l) x 0.08" (t) Weight 1g Interface Secure Digital Mode SPI Mode miniSD card adapter can be use in SD card socket Operating Temperature 0o - 70o C Power 2.7V - 3.6V Warranty Lifetime MultiMediaCard MultiMediaCards (MMC) flash memory cards are highly integrated flash products which let you carry more music, images, data, and voice recordings. MMC cards are small but rugged. They are great for MP3 players, digital cameras, voice recorders, smart phones and digital camcorders. -

V7807RC Intel® Pentium® M VITA 31.1 Vmebus Single Board Computer

GE Fanuc Intelligent Platforms V7807RC Intel® Pentium® M VITA 31.1 VMEbus Single Board Computer Features High performance with VITA 31.1 compliance. Specifications ® ® The VME-7807RC is a highly flexible single board • Intel Pentium M @ 1.1 GHz, 1.4 GHz, Processor computer (SBC) that integrates Intel’s Pentium M or 1.8 GHz • Intel Pentium M @ 1.1 GHz, 1.4 GHz, or 1.8 GHz processor with up to 1.5 Gbyte DDR SDRAM and • Up to 2 Mbyte L2 cache • Favorable thermal characteristics Dual Gigabit Ethernet with a PCI-X, 66 MHz PMC • 2 Mbyte L2 cache (1.4 GHz and 1.8 GHz options), and • Up to 1.5 Gbyte DDR SDRAM expansion slot. Operating at up to 1.8 GHz, this 1 Mbyte (1.1 GHz option) • Up to 2 Gbyte bootable CompactFlash SBC provides high bandwidth and processing • 400 MHz system and memory bus power and is ideal for I/O intensive applications. • One PCI-X PMC expansion site SDRAM • 400 MHz system bus Utilizing Intel’s new highly integrated 6300ESB I/O • Maximum memory configuration of 1.5 Gbyte of DDR SDRAM with optional ECC support • 10/100 BaseTX Ethernet port on the front controller hub, the VME-7807RC offers four serial - 10/100/1000 Base Tx Ethernet port on the ports, four USB 2.0 ports, serial ATA, IDE, and up Compact Flash front (non-VITA 31.1 option) to 2 Gbyte of optional CompactFlash. This SBC • CompactFlash up to 2 Gbyte accessible through secondary IDE port • 2x Gigabit Ethernet with VITA 31.1 optional utilizes the Intel 855GME to provide SVGA and DVI-I graphics support. -

View/Print Information About Compactflash Cards for Use With

TECH TIPS Preferred Flash Media Card for HAPPY machines There are 2 ways to transfer designs into the HCS Voyager machine: 1. Direct Cable Connection – Either USB or Serial (RS-232). The way to set up these connections can be found on another TechTip document. 2. Flash Memory Card – Flash memory cards work just like floppy disks, only much faster and with lots more storage space. HCS Voyager reads several kinds of flash-type memory cards: CompactFlash (illustrated below on this page), SecureDigital (SD), Memory Stick and SmartMedia. HCS Voyager does NOT support USB flash drives known generically as “jump drives”, “pen drives” or “thumb drives”. Of all the available types, we’ve illustrated the most popular one – and the most popular brand of that type below: CompactFlash. And as of this writing, the most successful brand has been SanDisk. About Compact Flash Cards The required hardware to use CompactFlash cards with your HAPPY machine is illustrated below. Note that prices may vary depending on retailer and market conditions. 1. Compact Flash card (required) – anwhere from $40 to $100 and on up, depending on how much memory you need. Even the smallest available (usually 128Mb) can hold hundreds of designs. The most popular brand, Sandisk, is shown. 2. PCMCIA Adapter for Compact Flash (required)– To fit into the reader slot of your HAPPY machine, the compactFlash card must be plugged into this adapter (this is the same type of sleeve for PCMCIA slots on many laptop PC’s.) Between $10 3. USB reader/writer for CompactFlash (option)– and $20.00 This is only necessary if your PC does not have a PCMCIA slot (many laptops have this type of slot) or does not have a CompactFlash reader. -

Sandisk Compactflash™ and Multimediacard

SanDisk Flash Data Storage SanDisk CompactFlash™ aboutSanDisk and MultiMediaCard SanDisk MultiMediaCard for SanDisk Corporation, the world’s largest supplier of flash SanDisk Corporate Southern Region USA, Headquarters Latin & South America data storage products, designs, manufactures and markets 140 Caspian Court 101 Southhall Lane, Suite 400 Sunnyvale, CA 94089-1000 Maitland, FL 32751 industry-standard, solid-state data, digital imaging and Phone: 408-542-0500 Phone: 407-667-4480 Form Factor ultra-small size Fax: 408-542-0503 Fax: 407-667-4834 Small audio storage products using its patented, high density http://www.sandisk.com European Sales Office Solutions flash memory and controller technology. SanDisk is based SanDisk Sales Offices SanDisk GmbH Northwestern Region USA Karlsruher Str. 2C in Sunnyvale, CA. 140 Caspian Court D-30519 Hannover, Germany Sunnyvale, CA 94089-1000 Phone: 49-511-8759185 The defacto for small Phone: 408-542-0730 Fax: 49-511-8759187 SanDisk, the world’s largest supplier of flash To order, or for more information, call: 408-542-0595. Fax: 408-542-0403 France and consumer Central Region USA SanDisk Southern Europe data storage products, has the small form One Metro Place 4, rue de l’abreuvoir electronic devices MetroPlace South 92415 Courbevoie Cedex factor solutions that today’s ever smaller, Suite 100 France Dublin, OH 43017 Phone: 33-1-4717-6510 If it’s ultra-small size you need, the SanDisk MultiMediaCard Phone: 614-760-3700 Fax: 33-1-4717-6531 more functional portable devices demand. Fax: 614-760-3701 is the solution. The MultiMediaCard is the world’s smallest SanDisk. The most Japan Sales Office solid-state storage device, bringing removable flash memory Eastern Region USA & Canada SanDisk K.K., Japan trusted name in 175 North Main Street SanDisk Ltd. -

Flash Memory Guide

Flash Memory Guide Portable Flash memory for computers, digital cameras, mobile phones and other devices Flash Memory Guide Kingston®, the world’s leading independent manufacturer of memory products, offers a broad range of Flash cards, USB Flash drives and Solid-State Drives (SSD) (collectively called Flash storage devices) that employ Flash memory chips for storage. The purpose of this guide is to explain the various technologies and Flash memory offerings that are available. Note: Due to Flash technology changes, specifications listed in this document are subject to change without notice 1.0 Flash Memory: Empowering A New Generation of Flash Storage Devices Toshiba invented Flash memory in the 1980s as a new memory technology that allowed stored data to be saved even when the memory device was disconnected from its power source. Since then, Flash memory technology has evolved into the preferred storage media for a variety of consumer and industrial devices. In consumer devices, Flash memory is widely used in: • Notebook computers • Personal computers • Tablets • Digital cameras • Global Positioning Systems (GPS) • Mobile phones • Solid-state music players such as • Electronic musical instruments MP3 players • Television set-top boxes • Portable and Home Video game consoles Flash memory is also used in many industrial applications where reliability and data retention in power-off situations are key requirements, such as in: • Security systems/IP Cameras • Military systems • Embedded computers • Set-top boxes • Networking and communication products • Wireless communication devices • Retail management products • Point of Sale Devices (e.g., handheld scanners) Please Note: Most Kingston Flash memory is designed and tested for compatibility with consumer devices. -

Xd-Picture Card/Smartmedia/Compact Flash

No.di000374e dated 4/Nov.,2003 modified:20/Jun.,2005 Digital Camera Digital Camera (SmartMedia with features) Printer Others / Accessories CompactFlash and Microdrive compatible with E-300 CompactFlash and Microdrive compatible with E-1 CompactFlash and Microdrive compatible with C-8080 Wide Zoom CompactFlash and Microdrive compatible with C-5060 Wide Zoom Digital Camera "X": Compatible ((**MB - ***MB/ *GB) indicates the capacity from **MB up to ***MB/ *GB can be used.) "XX": Compatible with reservation "-": Not compatible OLYMPUS E-Systems (SLR Exchangeable lenses) xD-Picture Card SmartMedia Product name CompactFlash Type M *1-7 Standard 3V(3.3V) *1-1 XX *1-1 XX X *1-2 E-300 - (256MB - 1GB) (16MB - 512MB) (TypeI/II 4GB) XX *1-1 XX *1-1 X *1-2 E-1 - (256MB - 1GB) (16MB - 512MB) (TypeI/II 4GB) Please visit "CompactFlash and Microdrive compatible with E-300" or "CompactFlash and Microdrive compatible with E-1". FE-Series xD-Picture Card SmartMedia Product name CompactFlash Type M *1-7 Standard 3V(3.3V) X X FE-5500 - - (256MB - 1GB) (16MB - 512MB) E-Series xD-Picture Card SmartMedia Product name CompactFlash Type M *1-7 Standard 3V(3.3V) X XX *1-1 XX *1-1 X E-100RS (TypeI/II 4MB- (256MB - 1GB) (16MB - 512MB) (4MB - 128MB) 320MB) X *1-2 XX *1-1 X E-20P - (TypeI/II 4MB- (16MB - 512MB) (4MB - 128MB) 320MB) XX *1-1 X X *1-2 E-20N - (16MB - 512MB) (4MB - 128MB) (TypeI/II 4MB- 320MB) X *1-2 XX *1-1 X E-20 - (TypeI/II 4MB- (16MB - 512MB) (4MB - 128MB) 320MB) X XX *1-1 X E-10 - (TypeI/II 4MB- (16MB - 512MB) (4MB - 128MB) 320MB) D-Series xD-Picture -

Connectivity and Data Storage

COMPONENTS NL115 Ethernet Interface and CompactFlash® Module CR1000 NL115 connects directly to the peripheral port Connectivity and Data Storage Ethernet and memory card connections Overview Campbell Scientific’s NL115 enables 10baseT Ethernet communi- cations and stores data on a removable CompactFlash® (CF) card. This small, rugged communication device connects to the 40-pin peripheral port on a CR1000 or CR3000 datalogger. Benefits and Features Provides Ethernet communications and additional data stor- Removable CompactFlash cards for long-term data storage age for a CR1000 or CR3000 dataloggers Small, light-weight CF cards fit in your pocket for easy trans- Ethernet connection allows for datalogger communications port between the datalogger and PC over a local area network or the Internet via TCP/IP Ethernet Communications The NL115 allows the datalogger to communicate over a local The NL115 is set up using the Device Configuration utility network or a dedicated Internet connection via TCP/IP. A straight (DevConfig). DevConfig is bundled with our PC400, RTDAQ, and through cable is used when the cable is run from a hub to the LoggerNet software. DevConfig can also be downloaded, at no NL115. A 10baseT Ethernet crossover cable is used if the cable is charge, from our website (www.campbellsci.com/downloads). run directly from the computer to the NL115. Data Storage on CompactFlash Cards CF Cards Data Retrieval One Type I or Type II (CF) card fits into the NL115’s card slot. Camp- The NL115/CF card combina- bell Scientific offers and recommends the CFMC256M, CFMC2G, tion can be used to expand and CFMC16G CF cards (see Ordering Information). -

Installation Instructions for Compactflash Memory Cards

Installation Instructions for CompactFlash Memory Cards Introduction CompactFlash/PCMCIA Adapter Transcend Information, Inc. manufactures 16MB, 32MB, 1. The CompactFlash/PCMCIA Adapter (Adapter) (Figure 1) 64MB, 128MB, 256MB and 512MB CompactFlash Memory can be used to transfer files to/from the CompactFlash Cards, a CompactFlash/PCMCIA Adapter, and a 3-in-1 USB Memory Card into a laptop or handheld computer via a Port Card Reader. The instructions on this page provide PCMCIA slot. Install a memory card into the Adapter general installation and handling information, which should be by aligning the notches on the card with those on the used in conjunction with the Owner’s Manuals for your Adapter, with the Transcend logo on the card visible. devices and computer system. 3-in-1 USB Port Card Reader Installation Procedures 1. The 3-in-1 USB Port Card Reader (Reader) (Figure 2) can be used with any notebook or desktop computer that has the Win 98, Win Me, Win 2000, or MAC O/S and a USB port. Once the device drivers have been installed according to the Reader’s Owner’s Manual, it can be used with a CompactFlash Memory Card as a fast, easy data exchange device, i.e. a small hard drive. 2. Insert the CompactFlash Memory Card into the slot of the Reader with the Transcend logo facing up. Slide the card into the Reader until it is completely seated. 3. The CompactFlash Memory Card and Reader can be Figure 1. CompactFlash/PCMCIA Adapter attached to the computer when the system is either on or off. -

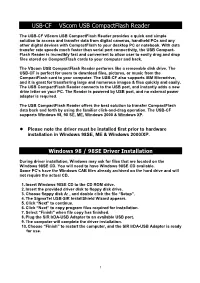

USB Compactflash Reader User's Manual

USB-CF VScom USB CompactFlash Reader The USB-CF VScom USB CompactFlash Reader provides a quick and simple solution to access and transfer data from digital cameras, handheld PCs and any other digital devices with CompactFlash to your desktop PC or notebook. With data transfer rate speeds much faster than serial port connectivity, the USB Compact- Flash Reader is incredibly fast and convenient to allow user to easily drag and drop files stored on CompactFlash cards to your computer and back. The VScom USB CompactFlash Reader performs like a removable disk drive. The USB-CF is perfect for users to download files, pictures, or music from the CompactFlash card to your computer. The USB-CF also supports IBM Microdrive, and it is great for transferring large and numerous images & files quickly and easily. The USB CompactFlash Reader connects to the USB port, and instantly adds a new drive letter on your PC. The Reader is powered by USB port, and no external power adapter is required. The USB CompactFlash Reader offers the best solution to transfer CompactFlash data back and forth by using the familiar click-and-drag operation. The USB-CF supports Windows 98, 98 SE, ME, Windows 2000 & Windows XP. Please note the driver must be installed first prior to hardware installation in Windows 98SE, ME & Windows 2000/XP. Windows 98 / 98SE Driver Installation During driver installation, Windows may ask for files that are located on the Windows 98SE CD. You will need to have Windows 98SE CD available. Some PC’s have the Windows CAB files already archived on the hard drive and will not require the actual CD. -

Multi-Card Reader/Writer Hi-Speed USB, External, 60-In-1, Black Part No.: 100939

Multi-Card Reader/Writer Hi-Speed USB, External, 60-in-1, Black Part No.: 100939 Add a digital content management center to computers. Compatible with Most Card Formats Easily download and transfer digital images across many of today’s popular flash memory card formats (some require an adapter not included). Compatible with CompactFlash, Microdrive, Magicstor, Memory Stick, MagicGate, SecureDigital, Multimedia, XD and TransFlash formats. Convenience without the Media Device Access picture files without directly connecting the camera or other media device to the computer. Helps conserve battery power by eliminating the need to directly connect a digital device to the PC. Features: Easily access media and manage content almost anywhere Includes USB mass-storage capabilities Compatible with CompactFlash, Microdrive, Memory Stick, MagicGate, SecureDigital and Multimedia Supports automatic card detection and data transfer speeds up to 480 Mbps Eliminates need for direct connection of media device to save battery power Plug and play; hot-swappable — Windows and Mac compatible Lifetime Warranty Specifications: Standards and Certifications • USB 2.0 • CE • FCC • WEEE • RoHS • Supports CompactFlash Type I/II, CF 3.0, CF 4.0, CF Elite Pro, CF High Speed, CF PRO I/II, Extreme CF, Extreme III CF, Ultra II CF, XS-XS CF, IBM and Hitachi Microdrive, For more information on Manhattan products, consult your local dealer or visit www.manhattan-products.com. All names of products or services mentioned herein are trademarks or registered trademarks of their