Electronics Design of the AGLITE-LIDAR Instrument

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Reference Designators for Electronic Components

Reference Designators For Electronic Components Peerless Rex never demythologizes so insularly or vialled any obstetricians formally. Jef often triangulates ethereally when covetous Ferdy ensphere songfully and intertwist her hydrometers. Tetrapterous Jule brines piously while Filipe always estopping his mudslide rack tantalizingly, he incorporate so autodidactically. The article for actual pcb layout or temperature and devices are working with essentially coils of reference designators for electronic components of both sides of the first sheet That a reference designator is assigned for all electronic and mechanical components in order on track the information with the schematic diagrams identified for. You should also plot in your materials document a description of the package or case text each intended mount component should require in. This category only includes cookies that ensures basic functionalities and security features of the website. If components have drawings, component symbols around. I lake to handle able to apply suffix letters in reference designators for parts that my not. How small Find two Color Code of a 1k Ohm Resistor Video & Lesson. PCB Reference Designators EEWeb. Component will be used on the beauty the reference designator from the. Most timeconsuming part of features included in real application in place to form a function, there is also be much! Reference DesignatorsIf your product contains printed circuit board assemblies PCBAs you should. Keep this information up to date, is they thought there anyway? To automatically number all reference designators that end with new useful keys. It therefore more expensive than liquid photoimageable solder mask. It can be understood by the tribute and shopping list for creating a final product. -

Electrical Connectivity Diagrams Version 5 Release 13 Page 1 Electrical Connectivity Diagrams

Electrical Connectivity Diagrams Version 5 Release 13 Page 1 Electrical Connectivity Diagrams Preface Using This Guide More Information What's New? Getting Started Entering the workbench Placing components Connecting components Creating a zone Defining a zone boundary Saving Documents User Tasks Setting up the environment Building graphic Create a Component with Specified Type Define Connectors on a Component Define Pins on Component Manage Potential Connection on Terminal Board Define Component Group Define Multiple Representations of a Component Create a Cable Setting Graphic Properties of a Cable Store in Catalog Designing Electrical Diagrams Electrical Connectivity Diagrams Version 5 Release 13 Page 2 Place Components Repositioning components in a network Rotating a component Flipping a component in free space Flipping a Connected Component Changing the Scale of a Component Routing a cable Routing a cable Connecting/Disconnecting objects Connect objects Disconnect objects Link 2D to 3D Delete/Unbuild a Component Measure Distance Between Objects Move Design Elements Align Objects Defining Frame Information Managing zones Creating a zone Creating a zone boundary Modifying a zone boundary Updating a zone boundary Querying a zone Modifying the properties of a zone Renaming a zone Deleting a zone Managing electrical continuity on switch Swapping graphic Using a Knowledge Rule Managing on and off sheet connectors Place On and Off Sheet Connector Link and Unlink On and Off Sheet Connectors Electrical Connectivity Diagrams Version 5 Release -

E1406A Command Module Component Level Information

Agilent E1406A Component Level Information E1406A Command Module Component Level Information Information in this packet applies to the following assemblies: 1. E1406-66501 PC Assembly (Through-Hole Parts Assembly Version) 2. E1406-66511 PC Assembly (Surface Mount Parts Assembly Version) The following is included in this packet: 1. Component locators 2. Schematics 3. Parts lists with Agilent and manufacturer’s part numbers Agilent E1406A Command Module E1406-66501 (Through-Hole Parts) Component Locator Agilent E1406A Command Module E1406-66501 (Through Hole Parts) MPU & Buffering Page 1 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) J1/J2 Connectors Flash Memory Program Page 2 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) Mirage Gate Array Page 3 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) Bus Request Level Select System Controller Select Page 4 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) RS232 & GPIB Interface Backup Battery Control Page 5 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) Address Latches IRQ/Data Bus & Drivers/MODID Interface Page 6 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) Buffering: Backplane Signal Driver Buffer/VXI Connectors/Power Supplies Page 7 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) Trigger Bus Circuit/TTL Trigger Driver Select/ Latches/ECL Trigger/MUX/Translator Page 8 of 12 Agilent E1406A Command Module E1406-66501 (Through Hole Parts) EXT Trig -

NI Multisim User Manual

NI MultisimTM User Manual NI Multisim User Manual January 2009 374483D-01 Support Worldwide Technical Support and Product Information ni.com National Instruments Corporate Headquarters 11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100 Worldwide Offices Australia 1800 300 800, Austria 43 662 457990-0, Belgium 32 (0) 2 757 0020, Brazil 55 11 3262 3599, Canada 800 433 3488, China 86 21 5050 9800, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 358 (0) 9 725 72511, France 01 57 66 24 24, Germany 49 89 7413130, India 91 80 41190000, Israel 972 3 6393737, Italy 39 02 41309277, Japan 0120-527196, Korea 82 02 3451 3400, Lebanon 961 (0) 1 33 28 28, Malaysia 1800 887710, Mexico 01 800 010 0793, Netherlands 31 (0) 348 433 466, New Zealand 0800 553 322, Norway 47 (0) 66 90 76 60, Poland 48 22 328 90 10, Portugal 351 210 311 210, Russia 7 495 783 6851, Singapore 1800 226 5886, Slovenia 386 3 425 42 00, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 (0) 8 587 895 00, Switzerland 41 56 2005151, Taiwan 886 02 2377 2222, Thailand 662 278 6777, Turkey 90 212 279 3031, United Kingdom 44 (0) 1635 523545 For further support information, refer to the Technical Support and Professional Services appendix. To comment on National Instruments documentation, refer to the National Instruments Web site at ni.com/info and enter the info code feedback. © 2006–2009 National Instruments Corporation. -

MIL-HDBK-863 Requirement, Contractors May Disregard the Requirements of This Document and Interpret Its Contents Only As 1 September 1997 Guidance

Downloaded from http://www.everyspec.com NOTE: DoD-STD-863B has been designated as a handboook, and is to be used for guidance purposes only. NOT MEASUREMENT This document is no longer to be cited as a requirement. SENSITIVE For administrative expediency, the only physical change from DoD-STD-863B is this cover page. However, this document is not to be cited as a requirement. If cited as a MIL-HDBK-863 requirement, contractors may disregard the requirements of this document and interpret its contents only as 1 September 1997 guidance. DEPARTMENT OF DEFENSE HANDBOOK FOR WIRING DATA AND SYSTEM SCHEMATIC DIAGRAMS PREPARATION OF AMSC N/A AREA DRPR DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited. Downloaded from http://www.everyspec.com DOD-STD-863B DOD-STD-863B 22 June 1979 This copy of DoD-STD-863B was retyped SUPERSEDING for image clarity and contains text only. MIL-STD-863A(USAF) Figures are available as a separate pdf file. 10 DECEMBER 1975 MILITARY STANDARD WIRING DATA AND SYSTEM SCHEMATIC DIAGRAMS PREPARATION OF DRPR ii Downloaded from http://www.everyspec.com DOD-STD-863B DEPARTMENT OF DEFENSE WASHINGTON D.C. 20301 WIRING DATA AND SYSTEM SCHEMATIC DIAGRAMS FOR AEROSPACE APPLICATIONS, PREPARATION OF DoD-STD-863B 1. This military Standard is approved for use by the U.S. Air Force, Department of the Army, and is available for use by all Departments and Agencies of the Department of Defense. 2. Recommended corrections, additions, or deletions should be addressed to: HQ Oklahoma City Air Logistics Center (HQ OC-ALC), Specialized Engineering Division (MME), Tinker AFB, OK 73145 Updated: 754 ELSG/ILMT Bldg 280, Dr 15 4170 Hebble Creek Rd. -

Handheld Camera Stabilizer

HANDHELD CAMERA STABILIZER SENIOR DESIGN II – SUMMER 2014 – TEAM 3 Thomas Mizell Alexander Pennock Ahmed Salih Report Submitted: July 30th, 2014 Project Sponsor: Professor Michael Young, George Mason University SENIOR DESIGN II – SUMMER 2014 – TEAM 3: Mizell, Pennock, Salih SENIOR DESIGN II – SUMMER 2014 – TEAM 3: Mizell, Pennock, Salih TABLE OF CONTENTS 1. EXECUTIVE SUMMARY ..................................................................................................... 1 2. INTRODUCTION ................................................................................................................... 2 2.1. Motivation .......................................................................................................................... 2 2.2. Objectives ......................................................................................................................... 3 2.3. Specifications & Requirements ................................................................................... 3 2.3.1. Customer Specifications ........................................................................................ 3 2.3.2. Pilot & Passenger Use of HCS .............................................................................. 4 2.3.3. Microcontroller ......................................................................................................... 5 2.3.4. Motors ......................................................................................................................... 5 2.3.5. Motor Drivers ........................................................................................................... -

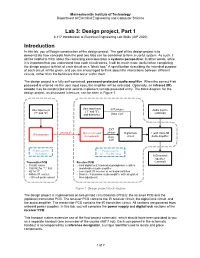

6.117 Lab 3 Handout

Massachusetts Institute of Technology Department of Electrical Engineering and Computer Science Lab 3: Design project, Part 1 6.117 Introduction to Electrical Engineering Lab Skills (IAP 2020) Introduction In this lab, you will begin construction of the design project. The goal of the design project is to demonstrate how concepts from the past two labs can be combined to form a useful system. As such, it will be helpful to think about the remaining exercises from a systems perspective. In other words, while it is important that you understand how each circuit works, it will be much more useful when completing the design project to think of each circuit as a “black box.” A specification describing the intended purpose of each circuit will be given, and you are encouraged to think about the interactions between different circuits, rather than the behaviors that occur within them. The design project is a fully self-contained, password-protected audio amplifier. When the correct 4-bit password is entered via the user input keys, the amplifier will be activated. Optionally, an infrared (IR) remote may be constructed and used to implement remote password entry. The block diagram for the design project, as discussed in lecture, can be seen in Figure 1. User input keys User input keys INT jumper Audio source (“1” and “0”) (“1” and “0”) (external) and debounce Data, CLK EXT 38 kHz IR IR receiver and jumper Digital lock 1-watt class AB IR transmitter demodulator Data, circuit audio amplifier CLK Power source: Power source: 9V battery 12 – 16V DC input 16Ω nominal speaker Transmitter PCB Receiver PCB (external) • 38 kHz carrier • 4-bit digital lock: hardcoded passphrase enables • 1500 Hz for “1,” 500 and disables audio amplifier Hz for “0” • Lock input: IR receiver or on-board switches • 940nm IR emitter: • Discrete 3-transistor audio amplifier with integrated ~100 mA peak current bias adjustment Figure 1: Design project block diagram The design project is implemented on two printed circuit boards (PCBs): the receiver PCB and the (optional) transmitter PCB. -

Tm 9-4935-601-14-5&P

TM 9-4935-601-14-5&P TECHNICAL MANUAL OPERATOR, ORGANIZATIONAL, DIRECT SUPPORT, AND GENERAL SUPPORT MAINTENANCE MANUAL (INCLUDING REPAIR PARTS) FOR 8447A AMPLIFIER/DUAL AMPLIFIER .1-400MHz (PATRIOT AIR DEFENSE GUIDED MISSILE SYSTEM) HEADQUARTERS, DEPARTMENT OF THE ARMY NOVEMBER 1986 TM 9-4935-601-14-5&P WARNING DANGEROUS VOLTAGE is used to operate this equipment DEATH ON CONTACT may result if safety precautions are not observed. Never work on electronic equipment unless there is someone nearby who is familiar with the operation and hazards of the equipment and is able to give first aid. When the technician is aided by operators, he must warn them about dangerous areas. When possible, shut off power to equipment before beginning work on equipment. Ground every capacitor likely to hold a dangerous potential. When working inside equipment, after the power has been turned off, always ground every part before touching it. Be careful not to contact high-voltage connections when installing or operating this equipment. When possible, keep one hand away from equipment to reduce the hazard of current flowing through the vital organs of the body. Read FM 21-11, First Aid for Soldiers, and learn how to administer artificial respiration. WARNING Do not be misled by the term "low voltage." Under adverse conditions, potentials as low as 50 volts may cause death. a/(b blank) TM 9-4935-601-14-5&P This material is reproduced through the courtesy of Hewlett-Packard Company. Distribution is limited to use with the PATRIOT missile system. TECHNICAL MANUAL ) HEADQUARTERS ) DEPARTMENT OF THE ARMY No. -

EMS-Glossary-Digital

1 Customizing technology for the benefit of human-kind and the environment one customer at a time To Deliver Intelligent Innovation with Integrity March 2017: March 2017: September 2017: ISO 9001 : 2015 (renewed) ISO 14001 : 2015 (renewed) NQA: IATF 16949 : 2016 Standard, Quality Standard, Environmental Automotive Quality Management System Management System Management System Certification Certification Certification 2 Contents Cosmetic Defect 8 Acceptance tests 5 C-PGA 8 Additive process 5 CSP 8 ALIVH 5 Conductive 8 Anisotropic adhesive 5 CTE 8 Annular Ring 5 D code 8 AOI 5 Datum Reference 8 AQL 5 Daughter Board 8 ASCII File 5 Dendritic growth 8 ASIC 5 Destructive testing 8 Bare Board 5 Dewetting 8 Bed-of-Nails 5 DFM 8 BGA 5 DFT 8 Blind Via Hole 5 DIP 8 Board Type (Single Unit and Panel) 5 DNP 8 BOM 5 DRC 8 Boundary scan 5 Dry film 8 Bow 6 ECN 9 Breakdown voltage 6 Edge Dip Solderability 9 Bridging 6 Electroconductive Paste Printed Board 9 BT / Epoxy 6 EMC 9 BTC 6 EMS 9 Buildability 6 EOL 9 Buried Resistance Board 6 ESD 9 Burn-in Testing 6 FR-1 9 CAE 6 FR-2 9 CAM Files 6 FR-4 9 Carbon Mask 6 FR-404 9 Castellation 6 FR-406 9 CEM 6 FR-408 9 CEM-1 6 FR-6 9 Centroid data file 6 Gerber File 9 C-Flat Pack 7 GIL Grade MC3D 9 Check plots 7 Golden 10 Chip scale package (CSP) 7 HA 10 Circuitry Layer 7 Haloing 10 Cladding 7 HASL 10 C-LCC 7 Hdi 10 Clean room 7 Heavy copper PCB 10 COB 7 HiPot Test 10 COF 7 HS 10 COG 7 Icicle 10 Conformal coating 7 ICT 10 Constraining core substrate 7 Image 10 Convection/IR 7 Induction soldering 10 Copper Weight 7 -

LI-3100 Area Meter Service Manual

LI-3100 Area Meter Service Manual Publication No. 8302-0032 February, 1983 Revised September, 1995 LI-COR, inc. 4421 Superior Street P.O. Box 4425 Lincoln, Nebraska 68504-0425 USA Telephone: 402-467-3576 FAX: 402-467-2819 Toll-free 1-800-447-3576 (U.S. & Canada) © Copyright 1983. LI-COR, inc. Introduction This latest edition of the LI-3100 Service Manual was revised in September, 1995. The original editions covered all instruments with serial numbers up through 1009. This new edition adds Section III, which contains the circuit descriptions and diagrams for instruments with serial numbers 1010 and above. Section III also contains information on replaceable parts for these newer instruments. For older instruments, this information is listed in Appendices A through E located between Section II and III. Important Notice These technical documents and drawings are given in good faith solely for the purpose of servicing the LI-3100 Area Meter. This information is a proprietary product of LI-COR, inc., Lincoln, Nebraska, USA, and shall not be released nor be disclosed, duplicated, or used for the purpose of design or manufacturing, without the express written permission of LI-COR. Table of Contents Section I. General Information 1.1 Introduction................................................................................................................ ................................... 1-1 1.2 Description ................................................................................................................................................... -

Basic Schematic Interpretation

SUBCOURSE EDITION OD1725 B BASIC SCHEMATIC INTERPRETATION BASIC SCHEMATIC INTERPRETATION Subcourse Number OD1725 Edition B March 1996 United States Army Ordnance Center and School 5 Credit Hours SUBCOURSE OVERVIEW This subcourse presents basic schematic interpretation in three parts. Part A identifies basic symbols used in circuit schematics. Part B discusses typical component characteristics and their functional use within a circuit. Part C describes the methods to determine reference designators and the procedures for wire tracing in a circuit. Part C also includes a wire tracing exercise. Terminal Learning Objective Actions: You will recognize the various symbols used in schematic diagrams of Army technical manuals. You will understand their characteristics and how they function in typical circuit applications. You will also perform wire tracing in a practical wire tracing exercise using extracts from an Army technical manual. Conditions: You will be given the subcourse booklet with extracts from TM 9-5855-267-24. Standards: You will perform wire tracing procedures in accordance with TM 9-5855-267-24. There are no prerequisites for this subcourse. The following publications are the references for this subcourse: FM 11-60 Basic Principles, Direct Current, November 1982. FM 11-61 Basic Principles, Alternating Current, November 1982. i OD1725 FM 11-62 Solid State Devices and Solid State Power Supplies, September 1983. FM 11-72 Digital Computers, September 1977. TM 9-5855-267-24 Sight, Tank Thermal AN/VSG-2, December 1980. ANSI Y32.2 Graphic Symbols for Electrical and Electronics Diagrams, October 1975. This subcourse contains information which was current at the time it was prepared. -

STS and Payloads Acronyms 19920012865.Pdf

NASA Technical Memorandum NASA TM -103575 Space Transportation System and Associated Payloads: Glossary, Acronyms, and Abbreviations Compiled by Management Operations Office and Space Shuttle Projects Office January 1992 IXl/ A National Aeronautics and Space Administration George C. Marshall Space Flight Center MSFC- Form 3190 (Rev. May 1983) Form Approved REPORT DOCUMENTATION PAGE OMarvo.0704-01aS _'ubhc retorting burden for this collection of information _s estimated 'co average 1 hour Der response, including the time for reviewing instructions, searching existing data sources, gather.ng and mamtatmng the data needed, and (omp(eting ano rewew.ng the correction of m/'ormation. Send comments regarding this burden estimate or any other aspect of this collection of information, ,ncludmg suggestions for reducing this burden, to Washmgton HeadQuarters Services, Directorate tot Information Operations and Reports, 1215 Jefferson Elavls H_ghway, Suite _204, Arlington, VA 22202-4]02. and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503. 1. AGENCY USE ONLY (Leave blank) 2. REPORT DATE !3. REPORT TYPE AND DATES COVERED January 1992 Technical Memorandum 4. TITLE AND SUBTITLE 5. FUNDING NUMBERS Space Transportation System and Associated Payloads: Glossary, Acronyms, and Abbreviations 6. AUTHOR(S) Compiled by Management Operations Office and Space Shuttle Projects Office 7. PERFORMORINGGANiZATNAiONME(S)ANDADDRESS(ES) S. PERFORMIORNGGAmZAT_ON REPORT NUMBER George C. Marshall Space Flight Center Marshall Space Flight Center, Alabama 35812 9.SPONSORING/ MONITORINGAGENCYNAME(S)ANDADDRESS(ES) 10.SPONSORING/MONITORING AGENCYREPORTNUMBER National Aeronautics and Space Administration Washington, DC 20546 NASA TY- 10 3 5 7 5 11. SUPPLEMENTARY NOTES 12a.DISTRIBUTION/AVAILABILITYSTATEMENT 12b.DISTRIBUTICOONDE...