CSS555C Micropower Timer (With Internal Timing Capacitor) GENERAL PART DESCRIPTION the CSS555C Is a Micropower Version of the Popular 555 Timer IC

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Page 1 of 19 a Plethora of NE-555 Data

A Plethora Of NE-555 data - NE555 Tutorials Page Page 1 of 19 - - - - - - - - - - - - - - - - Copyright © January 28th 1996 ..... Brought to you by Unitech Electronics Pty. Ltd. Following in the footsteps of the "primitive" but quite successful 4 pin OM802 timer IC manufactured by Philips semiconductor way back in 1969, a new and very innovative IC known as the NE-555 timer IC was released to the masses, being introduced around May 1971 by the then Signetics Corporation, to become known as the NE-555 / SE-555. It was called "The Ubiquitous Timer chip" and was also the very first very mass-produced commercially produced timer IC available at that time.The designers had no real idea what product life it would have, nor how brilliantly successful it would be, lasting well over 25 years still in mass-production today. [1971- 1996 ] The NE-555 would prove to be a " hit " and provide Electronic Engineers, Circuit Designers and a host of "Hobby Tinkerers" with a relatively novel and highly economical timer chip that was indeed very stable at timing all the way up to its maximum timing or oscillating frequency of 200KHz and in a very short time proved to be a very "user-friendly" timer integrated circuit for both simple and complex monostable as well as brilliant astable applications. Invented by a clever Swiss born gentleman by the name of Hans R. Camenzind in 1970, the NE-555 went on to become a legend in the industry, Since this versatile device became commercially available in May 1971, a plethora of highly innovative and very unique and "ever-so-ingenious" circuits has emerged and many circuits have been developed and demonstrated to the "N-th" degree in a variety of reputed "trade-only" journals, professional "Engineering Monthly" Journals as well as the vast numbers of excellent hobbiest publications globally, the likes of SILICON CHIP (SC) and ELEKTOR , Practical Electronics (PE) , Electronics Australia (EA) and Electronics Today International (ETI) to name but just a few. -

Optically Operated Circuit to Sense the Intensity of the Surrounding Light

1 Optically Operated Circuit to Sense the Intensity of the surrounding Light PRUTHVI.K.S ,, ABHIRAM.RDr.AIT, Bangalore and , TEJUS. P , Dr.AIT [email protected] Abstract—The transistor is the key active component in II. BIPOLAR TRANSISTOR BIASING practically all modern electronics, and is considered by many to be A very proper biasing of transistor is a very crucial measure one of the greatest inventions of the twentieth century. Transistors are invariably used in tremendous applications but its use is mostly for any transistor operation that decides the performance and as integrated form. The essential usefulness of a transistor comes efficiency of the device. There are many ways of biasing a from its ability to use a small signal applied between one pair of its BJT but the very stable way of biasing is the voltage divider terminals to control a much larger signal at another pair of configuration and hence it is been implemented in our light terminals. This property is called gain. This is the only basic intensity sensing circuit. In this section we discuss on the principle used to make an Optically Operated Circuit. An LED various ways of biasing a BJT and finally conclude that the (Light Emitting Diode) connected at the output pair of terminals voltage divider way of biasing is the best. light whose intensity is proportional to the surrounding light intensity. Case 1(Using two supplies) Keywords—Transistor biasing, LDR, phototransistors, 555 timer circuit, relay. I. INTRODUCTION he transistor is the fundamental building block of modern T electronic devices, and is ubiquitous in modern electronic systems. -

I. Introduction

EXPERIMENT 7. SCHMITT TRIGGER AND MULTIVIBRATOR CIRCUITS I. Introduction I.I Objectives The purpose of this experiment is to get familiar with different types of Schmitt trigger and multivibrator circuits and their implementations. I.II. Prerequisites You are expected to get familiar with the basics of the Schmitt trigger and multivibrator circuits. You can start reading your lecture notes and the section titled “CMOS Schmitt Trigger Circuits,” from your text book by Thomas A. Demassa and Zack Ciccone (pages 437-439). These pages are the introduction parts, and they explain what basically hysteresis is, and why it may be needed. However, that chapter explains digital Schmitt trigger circuits. What we construct in the laboratory are analog ones. Detailed information on these analog Schmitt trigger circuits and multivibrator circuits can be found in “Microelectronics Circuits” by Adel S. Sedra, Kenneth C. Smith. Reading these two references and completing the preliminary work will help you to understand the topic prior to your actual lab session and also it will help you in interpreting your experiment results. Experiment 7: Schmitt Triggers and Multivibrator Circuits All Rights Reserved. (e-mail: [email protected] ) by Eren Aydın and Barış Bayram © 2015 Page 1 of 7 II. Preliminary Work 1) Draw IC. Explain the aim of the the internal block diagram of 555 timer components inside 555 timer. 2) Consider the monostable multivibrator circuit given in Fig. What kind of input signal should be applied to the circuit for proper operation? Explain operation principle of this circuit in detail drawing required graphs. Moreover1 design a circuit doing the same operation using NAND gates, an inductor and a resistor. -

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC 555 AIM To design and set up astable multivibrator of 1000 Hz frequency and 60% duty cycle using IC 555 THEORY IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series connection of three resistors inside the IC sets the reference voltage levels to the two 2 1 comparators at V and V , the output of these comparators setting or resetting the flip- 3 CC 3 CC flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage. In the stable state the 푄 output of the flip-flop is high (ie Q low). This makes the output (pin 3) low because of the buffer which basically is an inverter.The flip-flop circuit also operates a transistor inside the IC, the transistor collector usually being driven low to discharge a timing capacitor connected at pin 7. The description of each pin s described below, Pin 1: (Ground): Supply ground is connected to this pin. Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator. When trigger of amplitude greater than (1/3)Vcc is applied to this terminal circuit switches to quasi-stable state. Pin 3: (Output) Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low at this pin will reset output. For normal operation pin 4 is connected to Vcc. -

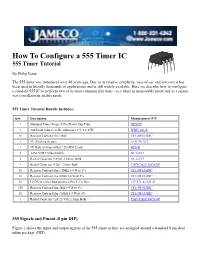

How to Configure a 555 Timer IC 555 Timer Tutorial

How To Configure a 555 Timer IC 555 Timer Tutorial By Philip Kane The 555 timer was introduced over 40 years ago. Due to its relative simplicity, ease of use and low cost it has been used in literally thousands of applications and is still widely available. Here we describe how to configure a standard 555 IC to perform two of its most common functions - as a timer in monostable mode and as a square wave oscillator in astable mode. 555 Timer Tutorial Bundle Includes: Qty. Description Manufacturer P/N 1 Standard Timer Single 8-Pin Plastic Dip Tube NE555P 1 400-Point Solderless Breadboard 3.3"L x 2.1"W WBU-301-R 10 Resistor Carbon Film 10kΩ CF1/4W103JRC 1 9V Alkaline Battery ALK 9V 522 1 9V Battery Snap with 6" 26AWG Leads BC6-R 2 3-Pin SPDT Slide Switch SS-12E17 2 Radial Capacitor 0.01µF 2.54mm Bulk SS-12E17 1 Radial Capacitor 4.7µF 2.5mm Bulk TAP475K025SCS-VP 10 Resistor Carbon Film 1.0MΩ 1/4 Watt 5% CF1/4W105JRC 10 Resistor Carbon Film 220Ω 1/4 Watt 5% CF1/4W221JRC 10 LED Uni-Color Red 660nm 2-Pin T-1¾ Box UT1871-81-M1-R 100 Resistor Carbon Film 3kΩ 1/4 Watt 5% CF1/4W302JRC 10 Resistor Carbon Film 330kΩ 1/4 Watt 5% CF1/4W334JRC 1 Radial Capacitor 1µF 25 Volt 2.5mm Bulk TAP105K025SCS-VP 555 Signals and Pinout (8 pin DIP) Figure 1 shows the input and output signals of the 555 timer as they are arranged around a standard 8 pin dual inline package (DIP). -

Title: Clap Switch

Title: Clap Switch I. Summary A Clap Switch circuit uses a microphone within the circuit to detect noises to turn the LED on. A clap switch circuit can be used in homes and businesses to turn on things such as: lights, TVs, or whatever it is set up to the clap switch. In many cases you can snap your fingers, clap your hands, or even speak to it. In fact, with modern technology, you can use commands to activate a piece/pieces of technology to allow it to turn on/off from anywhere within the room of the Clap Switch. II. Objective Individuals will construct a Clap Switch circuit and gain based knowledge on the 555 timer IC, BC547 Transistor and the condenser microphone. Also, individuals will get to see exactly how you can turn things on by a simply clap, snap, and/or the use of the voice. III. Industry Clap Switches can be installed into businesses and homes to allow individuals to turn lights and a number of technology on or off by using claps, snaps, or his/her voice. Clap Switches gives individuals the ability to remain seated or lying down to turn devices on or off. Also, this device is important to industries because technology is growing at an extreme rate and with the component within the Clap Switch it can help advance technology even more. In today’s world, we use voice control within our mobile devices, as well as, devices like the Echo, Google Home, etc. Within these devices that I previously listed, you can turn on a number of technologies by giving it simple voice commands, which is something that a great number of companies are working on – on a daily basis. -

Project Documentation

2013 AEAS Active Electronic Assault System Project Documentation Group 16 Karena Stout, Ryan Sivek, Alex Balogh i University of Central Florida 4/14/2013 Abstract Active Electronic Assault System (AEAS) is the senior design project for Group 16 overseen by the College of Engineering and Computer Science at the University of Central Florida. The project aims to provide an accurate firefight simulation tool that could potentially lead to the replacement of currently used out-of-date laser based systems. AEAS will use various sensors and communications subsystems to determine location and orientation of users and weapons in the field. This data will be communicated to a main server that calculates bullet trajectories and sends accurate hit notifications. System component selection and designs are presented and test procedures outlined. Project milestones and budget are discussed, and expected uses of the results of this effort are considered. i ii Table of Contents 1. Executive Summary ......................................................................................................... 1 2. Background ...................................................................................................................... 4 2.1. Vision .......................................................................................................................... 5 2.2. Specifications .............................................................................................................. 6 3. System Concept ............................................................................................................... -

The 555 Timer: Principles of Operation

Evil Mad Scientist Laboratories / evilmadscientist.com 1285 Forgewood Ave. Sunnyvale CA 94089 Questions? Please contact us: [email protected] Educational Supplement The 555 Timer: Principles of Operation What’s inside a 555 timer chip, and how does it work? Supplementary documentation for the “Three Fives” and 555SE Discrete 555 Timer Kits The 555 timer is one of the most iconic and popular Throughout the years there have been a great many integrated circuits of all time. It was designed in 1970 by Hans derivatives and descendants of the original 555 – low power R. Camenzind for the Signetics Corporation. Today – half a and low voltage types, dual and quad-555 chips, ultra-tiny century later – it is still an immensely popular circuit building surface mount versions, and countless implementations of the block. By some estimates, over a billion 555 timer circuits are 555 circuit itself. built every year. Amongst these derivatives are our Three Fives and 555SE kits: The 555 was the first commercially available integrated circuit both discrete implementations of the "equivalent circuit" from of its type and found immediate and widespread use as a the NE555 datasheet, built up using resistors and individual circuit “clock” oscillator and timing delay generator. The original ’3904 and ‘3906 transistors. These are, so to speak, “dis- Signetics NE555 datasheet described the function of the chip integrated circuits,” containing essentially the same components as follows: that you might find on the die of a 555 IC. “The NE/SE 555 monolithic timing circuit is a highly stable As with the integrated circuit version of the 555, you can build controller capable of producing accurate time delays, or working timer and oscillator circuits out of the discrete version, oscillation. -

Basic Electronics 18Eln14/24

ATME COLLEGE OF ENGINEERING MYSURU-570028 BASIC ELECTRONICS NOTES FOR 1st SEMESTER SUBJECT CODE: 18ELN14 Vision To develop highly skilled and globally competent professionals in the field of Electronics and Communication Engineering to meet industrial and social requirements with ethical responsibility. Mission To provide State-of-art technical education in Electronics and Communication at undergraduate and post-graduate levels, to meet the needs of the profession and society and achieve excellence in teaching-learning and research. To develop talented and committed human resource, by providing an opportunity for innovation, creativity and entrepreneurial leadership with high standards of professional ethics, transparency and accountability. To function collaboratively with technical Institutes/Universities/Industries, offer opportunities for interaction among faculty-students and promote networking with alumni, industries and other stake-holders. Program outcomes (POs) Engineering Graduates will be able to: PO1. Engineering knowledge: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems. PO2. Problem analysis: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences. PO3. Design/development of solutions: Design solutions for complex engineering problems and design system components or -

555 Timer Circuits

Modular Electronics Learning (ModEL) project * SPICE ckt v1 1 0 dc 12 v2 2 1 dc 15 r1 2 3 4700 r2 3 0 7100 .dc v1 12 12 1 .print dc v(2,3) .print dc i(v2) .end V = I R 555 Timer Circuits c 2018-2021 by Tony R. Kuphaldt – under the terms and conditions of the Creative Commons Attribution 4.0 International Public License Last update = 21 July 2021 This is a copyrighted work, but licensed under the Creative Commons Attribution 4.0 International Public License. A copy of this license is found in the last Appendix of this document. Alternatively, you may visit http://creativecommons.org/licenses/by/4.0/ or send a letter to Creative Commons: 171 Second Street, Suite 300, San Francisco, California, 94105, USA. The terms and conditions of this license allow for free copying, distribution, and/or modification of all licensed works by the general public. ii Contents 1 Introduction 3 2 Tutorial 5 3 Questions 11 3.1 Conceptual reasoning .................................... 15 3.1.1 Reading outline and reflections .......................... 16 3.1.2 Foundational concepts ............................... 17 3.1.3 Applying foundational concepts to an astable 555 circuit ............ 18 3.1.4 Adjustable duty cycle ............................... 19 3.1.5 Sequential timer circuit .............................. 20 3.1.6 Purpose of the Control terminal ......................... 21 3.1.7 Capacitor energy .................................. 21 3.1.8 Battery-powered 555 ................................ 22 3.1.9 555-based triangle and square wave oscillator .................. 23 3.2 Quantitative reasoning ................................... 25 3.2.1 Miscellaneous physical constants ......................... 26 3.2.2 Introduction to spreadsheets .......................... -

Implementation of 555 Timer Using Greenpak AN-CM-278

Application Note Implementation of 555 Timer using GreenPAK AN-CM-278 Abstract This application note illustrates the behavior of all operation modes of the 555 timer IC and shows the implementation details of the 555 timer internals, with all its operation modes, using the SLG46110V. This application note comes complete with design files which can be found in the References section. AN-CM-278 Implementation of 555 Timer using GreenPAK Contents Abstract ................................................................................................................................................ 1 Contents ............................................................................................................................................... 2 Figures .................................................................................................................................................. 2 Tables ................................................................................................................................................... 2 1 Terms and Definitions ................................................................................................................... 3 2 References ..................................................................................................................................... 3 3 Introduction.................................................................................................................................... 4 4 System Overview .......................................................................................................................... -

Water Aliasing

Water Aliasing Design Review TA: Luke Wendt ECE 445 March 10, 2017 Project Contributors: Atreyee Roy Siddharth Sharma 1 Table of Contents 1. Introduction .................................................................................................................... 3 1.1 Objective ........................................................................................................ 3 1.2 Background .................................................................................................... 3 1.3 High Level Requirements .............................................................................. 3 2. Design ............................................................................................................................. 4 2.1 Block Diagram ................................................................................................ 4 2.2 Physical Design ............................................................................................... 6 2.3 Block Design ................................................................................................... 7 2.3.1 Lighting Unit ....................................................................................... 7 2.3.2 User Interface ...................................................................................... 13 2.3.3 Water Unit ........................................................................................... 14 2.3 Risk Analysis ..................................................................................................