Ultra-Low-Power 2.4 Ghz Hartley Oscillator

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ariel Moss EE 254 Project 6 12/6/13 Project 6: Oscillator Circuits The

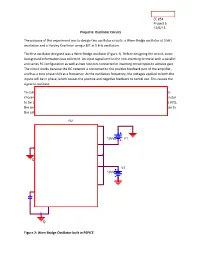

Ariel Moss EE 254 Project 6 12/6/13 Project 6: Oscillator Circuits The purpose of this experiment was to design two oscillator circuits: a Wien-Bridge oscillator at 3 kHz oscillation and a Hartley Oscillator using a BJT at 5 kHz oscillation. The first oscillator designed was a Wien-Bridge oscillator (Figure 1). Before designing the circuit, some background information was collected. An input signal sent to the non-inverting terminal with a parallel and series RC configuration as well as two resistors connected in inverting circuit types to achieve gain. The circuit works because the RC network is connected to the positive feedback part of the amplifier, and has a zero phase shift at a frequency. At the oscillation frequency, the voltages applied to both the inputs will be in phase, which causes the positive and negative feedback to cancel out. This causes the signal to oscillate. To calculate the time constant given the cutoff frequency, Calculation 1 was used. The capacitor was chosen to be 0.1µF, which left the input, series, and parallel resistors to be 530Ω and the output resistor to be 1.06 kHz. The signal was then simulated in PSPICE, and after adjusting the output resistor to 1.07Ω, the circuit produced a desired simulation with time spacing of .000335 seconds, which was very close to the calculated time spacing. (Figures 2-3 and Calculations 2-3). R2 1.07k 10Vdc V1 R1 LM741 4 2 V- 1 - OS1 530 6 OUT 0 3 5 + 7 OS2 U1 V+ V2 10Vdc Cs Rs 0.1u 530 Cp Rp 0.1u 530 0 Figure 2: Wien-Bridge Oscillator built in PSPICE Ariel Moss EE 254 Project 6 12/6/13 Figure 3: Simulation of circuit Next the circuit was built and tested. -

Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University

Marquette University e-Publications@Marquette Master's Theses (2009 -) Dissertations, Theses, and Professional Projects Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University Recommended Citation Stave, Nicholas Jon, "Analysis of BJT Colpitts sO cillators - Empirical and Mathematical Methods for Predicting Behavior" (2019). Master's Theses (2009 -). 554. https://epublications.marquette.edu/theses_open/554 ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR by Nicholas J. Stave, B.Sc. A Thesis submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science Milwaukee, Wisconsin August 2019 ABSTRACT ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR Nicholas J. Stave, B.Sc. Marquette University, 2019 Oscillator circuits perform two fundamental roles in wireless communication – the local oscillator for frequency shifting and the voltage-controlled oscillator for modulation and detection. The Colpitts oscillator is a common topology used for these applications. Because the oscillator must function as a component of a larger system, the ability to predict and control its output characteristics is necessary. Textbooks treating the circuit often omit analysis of output voltage amplitude and output resistance and the literature on the topic often focuses on gigahertz-frequency chip-based applications. Without extensive component and parasitics information, it is often difficult to make simulation software predictions agree with experimental oscillator results. The oscillator studied in this thesis is the bipolar junction Colpitts oscillator in the common-base configuration and the analysis is primarily experimental. The characteristics considered are output voltage amplitude, output resistance, and sinusoidal purity of the waveform. -

Oscillator Design

Oscillator Design •Introduction –What makes an oscillator? •Types of oscillators –Fixed frequency or voltage controlled oscillator –LC resonator –Ring Oscillator –Crystal resonator •Design of oscillators –Frequency control, stability –Amplitude limits –Buffered output –isolation –Bias circuits –Voltage control –Phase noise 1 Oscillator Requirements •Power source •Frequency-determining components •Active device to provide gain •Positive feedback LC Oscillator fr = 1/ 2p LC Hartley Crystal Colpitts Clapp RC Wien-Bridge Ring 2 Feedback Model for oscillators x A(jw) i xo A (jw) = A f 1 - A(jω)×b(jω) x = x + x d i f Barkhausen criteria x f A( jw)× b ( jω) =1 β Barkhausen’scriteria is necessary but not sufficient. If the phase shift around the loop is equal to 360o at zero frequency and the loop gain is sufficient, the circuit latches up rather than oscillate. To stabilize the frequency, a frequency-selective network is added and is named as resonator. Automatic level control needed to stabilize magnitude 3 General amplitude control •One thought is to detect oscillator amplitude, and then adjust Gm so that it equals a desired value •By using feedback, we can precisely achieve GmRp= 1 •Issues •Complex, requires power, and adds noise 4 Leveraging Amplifier Nonlinearity as Feedback •Practical trans-conductance amplifiers have saturating characteristics –Harmonics created, but filtered out by resonator –Our interest is in the relationship between the input and the fundamental of the output •As input amplitude is increased –Effective gain from input -

Oscillator Circuits

Oscillator Circuits 1 II. Oscillator Operation For self-sustaining oscillations: • the feedback signal must positive • the overall gain must be equal to one (unity gain) 2 If the feedback signal is not positive or the gain is less than one, then the oscillations will dampen out. If the overall gain is greater than one, then the oscillator will eventually saturate. 3 Types of Oscillator Circuits A. Phase-Shift Oscillator B. Wien Bridge Oscillator C. Tuned Oscillator Circuits D. Crystal Oscillators E. Unijunction Oscillator 4 A. Phase-Shift Oscillator 1 Frequency of the oscillator: f0 = (the frequency where the phase shift is 180º) 2πRC 6 Feedback gain β = 1/[1 – 5α2 –j (6α – α3) ] where α = 1/(2πfRC) Feedback gain at the frequency of the oscillator β = 1 / 29 The amplifier must supply enough gain to compensate for losses. The overall gain must be unity. Thus the gain of the amplifier stage must be greater than 1/β, i.e. A > 29 The RC networks provide the necessary phase shift for a positive feedback. They also determine the frequency of oscillation. 5 Example of a Phase-Shift Oscillator FET Phase-Shift Oscillator 6 Example 1 7 BJT Phase-Shift Oscillator R′ = R − hie RC R h fe > 23 + 29 + 4 R RC 8 Phase-shift oscillator using op-amp 9 B. Wien Bridge Oscillator Vi Vd −Vb Z2 R4 1 1 β = = = − = − R3 R1 C2 V V Z + Z R + R Z R β = 0 ⇒ = + o a 1 2 3 4 1 + 1 3 + 1 R4 R2 C1 Z2 R4 Z2 Z1 , i.e., should have zero phase at the oscillation frequency When R1 = R2 = R and C1 = C2 = C then Z + Z Z 1 2 2 1 R 1 f = , and 3 ≥ 2 So frequency of oscillation is f = 0 0 2πRC R4 2π ()R1C1R2C2 10 Example 2 Calculate the resonant frequency of the Wien bridge oscillator shown above 1 1 f0 = = = 3120.7 Hz 2πRC 2 π(51×103 )(1×10−9 ) 11 C. -

Hertly Oscillator

Name of Experiment: Construct a Hartley Oscillator and Determine its Frequency of Oscillation. Objectives: After completing this experiment we would able to learn: 1. How a tank circuit operates. 2. How it produces sinusoidal signal. 3. How a Hartley Oscillator operates. History: The Hartley oscillator was invented by Ralph V.L. Hartley while he was working for the Research Laboratory of the Western Electric Company. Hartley invented and patented the design in 1915 while overseeing Bell System's transatlantic radiotelephone tests; it was awarded patent number 1,356,763 on October 26, 1920. Theory: A Hartley oscillator is essentially any configuration that uses two series-connected coils and a single capacitor (see Colpitts oscillator for the equivalent oscillator using two capacitors and one coil). Although there is no requirement for there to be mutual coupling between the two coil segments, the circuit is usually implemented this way. It is made up of the following: • Two inductors in series, which need not be mutual • One tuning capacitor Advantages of the Hartley oscillator include: • The frequency may be adjusted using a single variable capacitor • The output amplitude remains constant over the frequency range • Either a tapped coil or two fixed inductors are needed Disadvantages include; Harmonic-rich content if taken from the amplifier and not directly from the LC circuit The basic LC Oscillator circuit is that they have no means of controlling the amplitude of the oscillations and also, it is difficult to tune the oscillator to the required frequency. If the cumulative electromagnetic coupling between L1 and L2 is too small there would be insufficient feedback and the oscillations would eventually die away to zero. -

RF Oscillators

Islamic University of Gaza Communications Engineering I (Lab.) Faculty of Engineering Prepared by: Electrical Department Eng. Mohammed K. Abu Foul Experiment # (1) RF Oscillators Prelab: 1. Describe the conditions of oscillation that the Colpitts oscillator and Hartley oscillator can operate in a proper way. 2. Try to design a Hartley oscillator as shown in figure 1.9 with 5 MHz output frequency, and then find the values of C3, L1 and L2. 3. Briefly describe the advantages of crystal oscillator. 4. Briefly describe the design concepts of voltage controlled oscillators. Experiment Objectives: 1. To understand the basic theory of oscillators. 2. To design and implement the Colpitts and Hartley oscillators. 3. To design and implement the crystal and voltage controlled oscillators. 4. To understand the measurement and calculation of the output frequency of oscillator. Experiment theory: Nowadays, wireless communication is widely used in and expanded rapidly. Therefore, RF oscillators become one of the important members in wireless communications. The characteristic of oscillator is that it can produce sinusoidal wave or square wave at output terminal without any input signal. So oscillator becomes an important role no matter for modulated signals or carrier signals. In this experiment, we will focus on the theory of feedback oscillators and the design and implementation of different kinds of oscillators. Besides, we can also learn to measure and calculate the output frequency of oscillators in this experiment. 1. The operation theory of oscillators. Figure 1.1 shows the basic block diagram of the oscillator circuit. It includes an amplifier and a resonator, which comprise the positive feedback network. -

Oscilators Simplified

SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN TAB BOOKS Inc. Blue Ridge Summit. PA 172 14 FIRST EDITION FIRST PRINTING Copyright O 1987 by TAB BOOKS Inc. Printed in the United States of America Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein. Library of Cangress Cataloging in Publication Data Horn, Delton T. Oscillators simplified, wtth 61 projects. Includes index. 1. Oscillators, Electric. 2, Electronic circuits. I. Title. TK7872.07H67 1987 621.381 5'33 87-13882 ISBN 0-8306-03751 ISBN 0-830628754 (pbk.) Questions regarding the content of this book should be addressed to: Reader Inquiry Branch Editorial Department TAB BOOKS Inc. P.O. Box 40 Blue Ridge Summit, PA 17214 Contents Introduction vii List of Projects viii 1 Oscillators and Signal Generators 1 What Is an Oscillator? - Waveforms - Signal Generators - Relaxatton Oscillators-Feedback Oscillators-Resonance- Applications--Test Equipment 2 Sine Wave Oscillators 32 LC Parallel Resonant Tanks-The Hartfey Oscillator-The Coipltts Oscillator-The Armstrong Oscillator-The TITO Oscillator-The Crystal Oscillator 3 Other Transistor-Based Signal Generators 62 Triangle Wave Generators-Rectangle Wave Generators- Sawtooth Wave Generators-Unusual Waveform Generators 4 UJTS 81 How a UJT Works-The Basic UJT Relaxation Oscillator-Typical Design Exampl&wtooth Wave Generators-Unusual Wave- form Generator 5 Op Amp Circuits -

Analog Circuits (EC-405) Unit : I Topic : Oscillator

Name of Faculty : Prof. L N Gahalod Designation : Associate Professor Department : Electronics & Communication Subject : Analog Circuits (EC-405) Unit : I Topic : Oscillator Analog Circuits (EC-405) Page 1 UNIT – I Feedback Amplifier and Oscillators 1.8 Oscillator: Any circuit that generates an alternating signal is called oscillator. To generate ac signal, the circuit is supplied energy from a dc source. The oscillators have variety of applications. In some application we need signal of low frequencies, in other of very high frequencies. For example, to test the performance of a stereo amplifier, we need an oscillator of variable frequency in audio range (20Hz – 20kHz), which is called audio frequency generator. Generation of high frequency is essential in all communication system. For example in radio and television broadcasting, the transmitter radiates the signal using a carrier of very high frequency. Some applications of communication system with their frequency band is given below. 550 kHz – 22 MHz Radio broadcasting 88 MHz – 108 MHz for FM radio 1 GHz – 4 GHz for DTH, TV and satellite Communication Figure 1.18: Block diagram of Oscillator Figure 1.18 shows that oscillator is an electronics source of alternating current or voltage having sine, square or saw tooth waves. Oscillator is a circuit which generates an ac source without requiring any externally applied input signal. It is a circuit which converts dc energy into ac energy at very high frequency. 1.9 Comparison between Amplifier and Oscillator: Comparision between an amplifier and an oscillator is explained in table 2. Analog Circuits (EC-405) Page 2 Amplifier Oscillator 1. -

Chapter-5 Oscillators

Unit– IV Oscillators Index 4.1 Types of feedback(Positive and Negative) 4.2 Principle of oscillation. 4.3 Oscillators: Hartley and Colpitts 4.1 Types of feedback(Positive and Negative) Feedback in amplifier In amplifier circuit, when a small signal is taken from the output and given to the input. It is called feedback in amplifier. • Input voltage Vi is given to an amplifier having gain A. Output voltage is Vo. • Feedback V f = β Vo is given to the input. • Β is the feedback factor. Value of the β is less than 1. • Due to feedback , input to the amplifier changes from Vi to Vi’ • If the feedback is in phase opposition to the input signal it is called degenerative feedback or negative feedback. Vi’ = Vi – V f • If the feedback is in phase with the input signal it is called positive feedback. Vi’ = Vi + V f 4.2 Principle of oscillation. Oscillator An electronic device that generates sinusoidal oscillation of desired frequency is known as oscillator. Oscillation are produced without any external signal source. The only input power to an oscillator is the d.c.power supply.In fact oscillator is the amplifier with positive feedback in which no input signal is given. Oscillators convert dc to ac. Oscillator ac out dc in Some possible output waveforms Damped oscillation in LC tuned circuit: • A tank or oscillatory circuit is a parallel form of inductor and capacitor elements which produces the electrical oscillations of any desired frequency. • Both these elements are capable of storing energy. Whenever the potential difference exists across a capacitor plates, it stores energy in its electric field. -

W9HE Amplifiers

Introduction Rather than try to give you the material so that you can answer the questions from “first principles," I will provide enough information that you can recognize the correct answer to each question. Chapter 6 Notes In no particular order, the necessary “nuggets:” 1. Junction transistors are current controlled and therefore have relatively low input impedance. Field effect devices, including vacuum tubes, are voltage controlled and therefore have relatively high input impedance. Vacuum tubes are implicitly diodes as well. Transistor input and output elements can be reversed and the device would operate somewhat. 2. See attached amplifier circuits sheet. Another phrase for “common word" amplifer is “grounded word" amplifer. The key is determining which lead is at signal ground level. The lead may not be at DC ground for bias reasons. If a lead is connected to the power supply via a capacitor in parallel with a resistor then that lead is at signal ground. 3. See attached oscillators circuits sheet. Oscillators can be built using any type of amplifier. All that is required is a gain greater than 1 with positive feed back. The major classes of oscillators are named according to the method of providing that feedback. If the feedback circuit is a divided capacitor, then the oscillator is a Colpitts oscillator. The memory key is C for capacitance. If the feedback circuit is a divided inductor, then the oscillator is a Hartley oscillator. The memory key is H for Henries of inductance. If the feedback circuit is a crystal, then the oscillator os a Pierce oscillator. -

Oscillator Designguide

Oscillator DesignGuide September 2004 Notice The information contained in this document is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material. Warranty A copy of the specific warranty terms that apply to this software product is available upon request from your Agilent Technologies representative. Restricted Rights Legend Use, duplication or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 for DoD agencies, and subparagraphs (c) (1) and (c) (2) of the Commercial Computer Software Restricted Rights clause at FAR 52.227-19 for other agencies. Agilent Technologies 395 Page Mill Road Palo Alto, CA 94304 U.S.A. Copyright © 1998-2004, Agilent Technologies. All Rights Reserved. Acknowledgments Mentor Graphics is a trademark of Mentor Graphics Corporation in the U.S. and other countries. Microsoft®, Windows®, MS Windows®, Windows NT®, and MS-DOS® are U.S. registered trademarks of Microsoft Corporation. Pentium® is a U.S. registered trademark of Intel Corporation. PostScript® and Acrobat® are trademarks of Adobe Systems Incorporated. UNIX® is a registered trademark of the Open Group. Java™ is a U.S. trademark of Sun Microsystems, Inc. ii Contents 1 Oscillator QuickStart Guide Using DesignGuides................................................................................................ -

Design and Fabrication of LC-Oscillator Tool Kits Based Op-Amp for Engineering Education Purpose

See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/299434924 Design and Fabrication of LC-Oscillator Tool Kits Based Op-Amp for Engineering Education Purpose Article · January 2016 DOI: 10.11591/ijeecs.v1.i1.pp88-100 CITATIONS READS 5 1,966 3 authors, including: Syifaul Fuada Hakkun Elmunsyah Universitas Pendidikan Indonesia State University of Malang 146 PUBLICATIONS 507 CITATIONS 24 PUBLICATIONS 16 CITATIONS SEE PROFILE SEE PROFILE Some of the authors of this publication are also working on these related projects: Visible Light Communication Devices and Systems View project Contribution entrepreneurial knowledge, skills competence, and self-efficacy to student entrepreneurship readiness of multimedia expertise at vocational high school on Malang View project All content following this page was uploaded by Syifaul Fuada on 11 February 2017. The user has requested enhancement of the downloaded file. Indonesian Journal of Electrical Engineering and Computer Science Vol. 1, No. 1, January 2016, pp. 88 ~ 100 DOI: 10.11591/ijeecs.v1.i1.pp88-100 88 Design and Fabrication of LC-Oscillator Tool Kits Based Op-Amp for Engineering Education Purpose Syifaul Fuada1, Hakkun Elmunsyah2, Suwasono3 1Bandung Institute of Techology (ITB), Bandung, West Java, Indonesia 2,3State University of Malang (UM), Malang, East Java, Indonesia e-mail: [email protected] Abstract Tool kit is one of learning media that have important role in engineering education, the author has been finished in developing tool kit with oscillator “LC circuit” topic. This oscillator can generate a sinusoidal wave with constant frequency and amplitude. With this tool kit wish the student can develop their skill and applicated in electrical, electronic, communication circuits and systems area.