Low Power Multivibrator Circuits Using Subthreshold Adiabatic Logic

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Multivibrator Circuits

Multivibrator Circuits Bistable multivibrators Multivibrators Circuits characterized by the existence of some well defined states, amongst which take place fast transitions, called switching processes. A switching process is a fast change in value of a current or a voltage, the fast process implying the existence of positive reaction loops, or negative resistances. The switching can be triggered from outside, by means of command signals, or from inside, by slow charge accumulation and the reaching of a critical state by certain electrical quantities in the circuit. Circuits have two, well defined states, which can be either stable or unstable A stable state is a state, in which the circuit, in absence of a driving signal, can remain for an unlimited period of time The circuit can remain in an unstable state only for a limited period of time, after which, in the absence of any exterior command signals, it switches into the other state. The multivibrator circuits can be grouped, according to their number of stable (steady) states, into: - flip-flops (bistable circuits) with both states being stable - monostable circuits , having a stable and an unstable state - astable circuits , with both states being unstable Flip-flop circuits The main feature of the flip-flop circuits is the existence of two stable states, in which the circuit may remain for a long time. The switching from one state to the other is triggered by command signals Flip flop: an example for a sequential circuit (a circuit with outputs that present logical values depending on a certain sequence of signals, that have previously existed in the circuit). -

Npn Transistor Pnp Transistor

ELL 100 - Introduction to Electrical Engineering LECTURE 23: BIPOLAR JUNCTION TRANSISTOR (BJT) 1 CONTENTS • Introduction • Construction & working principle of BJT • Common-base and common-emitter circuits 2 BJT INTRODUCTION • Bipolar: Both electrons and holes (positively charged quasi- particles, absence of electron) contribute to current flow • Junction: Consists of an n- (or p-) type silicon sandwiched between two p- (or n-) type silicon regions • Transistor: 3-terminal device (Base, Emitter, Collector) Two types: npn & pnp 3 Bipolar Junction Transistor (BJT) 4 Various Types of General-Purpose or Switching Transistors: (a) Low Power (b) Medium Power (c) Medium to high power 5 First Working Transistor, Invented in 1947. Earliest Raytheon Blue transistors, Replica of 1st device made by first appearing in 1955 Shockley, Bardeen & Brattain at Bell Labs 6 Applications: Transistor As Switch 7 Applications: Transistor As Relay (Switch) Single channel 5V relay breakout board 8 Applications: Transistor As Amplifier TDA7297 Power Amplifier & Audio amplifier Module 9 Applications: Transistors in Radio 10 Applications: Transistor in Oscillator Colpitts Oscillator 11 Applications: Transistor in Oscillator Astable Multivibrator 12 Transistors in Timer Circuits 13 Transistor As NOT Gate 14 Transistors in NAND Gate 15 Bipolar Junction Transistor (BJT) The three terminals of the BJT are called the Base (B), the Collector (C) and the Emitter (E). n p p n n p npn transistor pnp transistor 16 Bipolar Junction Transistor (BJT) npn pnp 17 p-n-p Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 18 n-p-n Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 19 BJT Construction 20 Bipolar Junction Transistor (BJT) Basic Principle The voltage between two terminals (B and E) controls the current through the third terminal (C). -

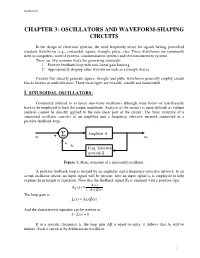

Chapter 3: Oscillators and Waveform-Shaping Circuits

mywbut.com CHAPTER3:OSCILLATORSANDWAVEFORM-SHAPING CIRCUITS Inthedesignofelectronicsystems,theneed frequentlyarises forsignals havingprescribed standardwaveforms(e.g.,sinusoidal, square,triangle,pulse,etc).Thesewaveformsarecommonly usedincomputers,controlsystems,communicationsystemsandtestmeasurementsystems. Therearetwocommonwaysforgeneratingsinusoids: 1. Positivefeedbackloopwithnon-lineargainlimiting 2. Appropriatelyshapingotherwaveformssuchasatrianglewaves. Circuitsthatdirectlygeneratesquare,triangleandpulsewaveformsgenerallyemploycircuit blocksknownasmultivibrators.Threebasictypesarebistable,astableandmonostable. I.SINUSOIDALOSCILLATORS: Commonly referred to as linear sine-wave oscillators although some forms of non-linearity havetobeemployedtolimittheoutputamplitude.Analysisofthecircuitsismoredifficultass-plane analysis cannot be directly applied to the non-linear part of the circuit. The basic structure of a sinusoidal oscillator consists of an amplifier and a frequency selective network connected in a positivefeedbackloop. AmplifierA xS + Σ xO + xf Freq.Selective networkβ Figure1:Basicstructureofasinusoidaloscillator. Apositive-feedbackloopisformedbyanamplifierandafrequency-selectivenetwork.Inan actualoscillatorcircuit,noinputsignalwillbepresent;hereaninputsignalxsisemployedtohelp explaintheprincipleofoperation.NotethatthefeedbacksignalXFissummedwithapositivesign: A(s) A (s) = f 1− A(s) β (s) Theloopgainis: )s(L =A(s) β (s) Andthecharacteristicequationcanbewrittenas: 1-L(s)=0 If at a specific frequency -

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC 555 AIM To design and set up astable multivibrator of 1000 Hz frequency and 60% duty cycle using IC 555 THEORY IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series connection of three resistors inside the IC sets the reference voltage levels to the two 2 1 comparators at V and V , the output of these comparators setting or resetting the flip- 3 CC 3 CC flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage. In the stable state the 푄 output of the flip-flop is high (ie Q low). This makes the output (pin 3) low because of the buffer which basically is an inverter.The flip-flop circuit also operates a transistor inside the IC, the transistor collector usually being driven low to discharge a timing capacitor connected at pin 7. The description of each pin s described below, Pin 1: (Ground): Supply ground is connected to this pin. Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator. When trigger of amplitude greater than (1/3)Vcc is applied to this terminal circuit switches to quasi-stable state. Pin 3: (Output) Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low at this pin will reset output. For normal operation pin 4 is connected to Vcc. -

An Electronic Switch ?Or Transient Studies

AN ELECTRONIC SWITCH ?OR TRANSIENT STUDIES A THESIS Presented to the Faculty of the Division of Graduate Studies Georgia Institute of Technology In Partial Fulfillment of the Requirements for the Degree Master of Science in Slectrical Engineering by Marshall Joseph McCann September 1949 107545 ii AN ELECTRONIC SWITCH FOR TRANSIENT STUDIES Approved: zf r ~~v Bate Approved by Chairman A up. d±, f^4f ACKNOWLEDGMENTS I wish to express my sincerest thanks to Prof. M. A. Honnell for his patient guidance and assistance, which were an immense aid in the prosecution of this work. I am also indebted to the Photographic and Repro duction Laboratory at the State Engineering Experiment Station of the Georgia Institute of Technology for their splendid cooperation with the photographic work herein. iv TABLE 0? CONTENTS PAGE Acknowledgments iii List of figures vi I- Introduction 1 II- A Survey of the Literature 3 Mechanical Systems.. • 3 Electronic Systems 4 III- Design Considerations for an Electronic Switch 8 General , , 8 Possible Approaches 8 IV- The Switch 12 V- The Square Wave Generator 16 Design Requirement s 16 Symmetrical Multivibrator 16 Improvement of Waveform 22 VI- The Synchronizing Section 37 General 37 Phase Shifting 27 Amplification and V/ave shaping 29 Synchronization of the Multivibrator 39 Summary of the Synchronizing Action 31 VII- Operation 34 VIII- Siamples of Operation 37 Lumped Constant Circuits 37 V P-4GE VIII- Examples of Operation (continued) Transmission Line Transients 41 IX- Summary • 46 appendix I, Analysis of Plate-Inductance Compensation of the Multivibrator 47 appendix II, Scaling of Circuits for A-C Transients 50 appendix III, Parts List 55 Bibliography ... -

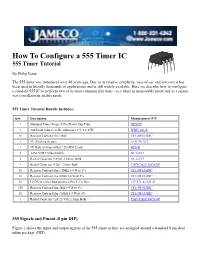

How to Configure a 555 Timer IC 555 Timer Tutorial

How To Configure a 555 Timer IC 555 Timer Tutorial By Philip Kane The 555 timer was introduced over 40 years ago. Due to its relative simplicity, ease of use and low cost it has been used in literally thousands of applications and is still widely available. Here we describe how to configure a standard 555 IC to perform two of its most common functions - as a timer in monostable mode and as a square wave oscillator in astable mode. 555 Timer Tutorial Bundle Includes: Qty. Description Manufacturer P/N 1 Standard Timer Single 8-Pin Plastic Dip Tube NE555P 1 400-Point Solderless Breadboard 3.3"L x 2.1"W WBU-301-R 10 Resistor Carbon Film 10kΩ CF1/4W103JRC 1 9V Alkaline Battery ALK 9V 522 1 9V Battery Snap with 6" 26AWG Leads BC6-R 2 3-Pin SPDT Slide Switch SS-12E17 2 Radial Capacitor 0.01µF 2.54mm Bulk SS-12E17 1 Radial Capacitor 4.7µF 2.5mm Bulk TAP475K025SCS-VP 10 Resistor Carbon Film 1.0MΩ 1/4 Watt 5% CF1/4W105JRC 10 Resistor Carbon Film 220Ω 1/4 Watt 5% CF1/4W221JRC 10 LED Uni-Color Red 660nm 2-Pin T-1¾ Box UT1871-81-M1-R 100 Resistor Carbon Film 3kΩ 1/4 Watt 5% CF1/4W302JRC 10 Resistor Carbon Film 330kΩ 1/4 Watt 5% CF1/4W334JRC 1 Radial Capacitor 1µF 25 Volt 2.5mm Bulk TAP105K025SCS-VP 555 Signals and Pinout (8 pin DIP) Figure 1 shows the input and output signals of the 555 timer as they are arranged around a standard 8 pin dual inline package (DIP). -

DOCID: 3927952 Analysis of a Transistor Monostable Multivibrator

DOCID: 3927952 UNCLASSIFIED @>pproved for release by NSA on 11-29-2011, Transparencv Case# 6385J Analysis of a Transistor Monostable Multivibrator BY GILBERT M. NEILL Unclassified A demonstration of a simple and rapi,d process of numerical analysis, which furnishes practical, values for specific transisror circuit designs. The measured characteristics of the transistor, rather than rrwdels chosen for analytical, convenience, are used to get the final, val,ues. The explosive growth of the electronic digital computer during the postwar years has aroused a profound interest in switching circuits. One of the switching circuits that is used extensively in the modem_ computer is the multivibrator. The multivibrator (MV) has three forms: a-stable MV (or free-running), monostable MV (or single shot), and bi-stable MV (or flip-flop). The circuit to be analyzed is a monostable MV and was chosen because it is somewhat easier to analyze; but the S<Ulle principles apply to the other two. The pro fessional relevance of this paper does not lie in the circuit that is analyzed but in the method of analysis: that of making approxima tions and assumptions (later checked) as to the conditions in the circuit and then calculating specific values and waveforms. This method has wide application to digital and pulse circuits, and makes a relatively easy task out of an otherWise involved analysis. More over, when the analysis has been completed the designer is in an excellent position to note the effect of different component values and to make appropriate alterations. Our objective is to demon strate this method by calculating the important waveform voltages . -

Tuesday 2/19/19 Nonlinear Oscillators Our Definition: an Oscillator with a Periodic Non-Sinusoidal Output, Such As a Square Wave

Tuesday 2/19/19 Nonlinear Oscillators Our definition: an oscillator with a periodic non-sinusoidal output, such as a square wave. 1) Sinusoidal oscillator circuit with really high amplifier gain, much higher than necessary to satisfy the BSC Let’s revisit the Wein bridge oscillator (shown on next page) R3 of 15 kΩ achieved oscillation. Let’s make R3 by 25 kΩ and evaluate the difference. As R3 gets large, the tops of the output signal flatten out, more closely approximating a square wave. This forces more of the time varying signal to reside in the nonlinear range of the op amp, effectively clipping it. However, the bottom part of the output square wave is close to -4V, not 0V, as would be expected of a digital signal. A clipping diode can be added off the op amp output signal and applied to a 100 kΩ load resistor. This removes most of the negative going part of the periodic signal. Two CMOS inverters were added after the 100 kΩ load resistor, and fed to another 100 kΩ load resistor to square up the signal <see below>. 121 122 V(2) with R3 = 15 kΩ V(2) with R3 = 25 kΩ 123 Voltage waveform after the diode. Observe that the peak voltage has dropped due to the voltage drop across the diode. Voltage waveform after two CMOS inverters following the clipping diode circuit. 124 2) A rail-to-rail comparator added to the sinusoidal oscillator’s output This circuit can convert the sinusoidal output voltage to a square wave. More on Nonlinear Oscillators a. -

Noise Model of Relaxation Oscillators Due to Feedback Regeneration Based on Physical Phase Change

Noise Model of Relaxation Oscillators Due to Feedback Regeneration Based on Physical Phase Change Bosco Leung Electrical and Computer Engineering Department, University of Waterloo Waterloo, Ontario, Canada [email protected] Abstract— A new approach to investigate noise spikes due to regeneration in a relaxation oscillator is proposed. Noise spikes have not been satisfactorily accounted for in traditional phase noise models. This paper attempts to explain noise spikes/jump phenomenon by viewing it as phase change in the thermodynamic system(for example, from gas to liquid or magnetization of ferromagnet). Both are due to regeneration (positive feedback in oscillator as well as alignment of spin due to positive feedback in ferromagnet). The mathematical tool used is the partition function in thermodynamics, and the results mapped between thermodynamic system and relaxation oscillator. Theory is developed and formula derived to predict the magnitude of the jump, as a function of design parameter such as regeneration parameter or loop gain. Formulas show that noise increases sharply as regeneration parameter/loop gain approaches one, in much the same way when temperature approaches critical temperature in phase change. Simulations on circuits (Eldo) using CMOS as well as Monte Carlo simulations (Metropolis) on ferromagnet (Ising model) were performed and both show jump behaviour consistent with formula. Measurements on relaxation oscillators fabricated in 0.13um CMOS technology verify such behaviour, where the sharp increase in noise when regeneration parameter/loop gain is close to one, matches closely with the theoretical formula. Using the formula the designer can quantify the variation of noise spikes dependency on design parameters such as gm (device transconductance), R, I0, via their influence on regeneration parameter/loop gain. -

Operational Amplifier 741 As Monostable Multivibrator

Page 1 of 5 Operational Amplifier as mono stable multi vibrator Aim :- To construct a monostable multivibrator using operational amplifier 741 and to determine the duration of the output pulse generated and to compare it with that of theoretical value. Apparatus :- Operational amplifier ( IC 741 ), C.R.O., two power supplies to the operational amplifier, four non inductive fixed resistors (R 1, R 2, R 4 and R 5), one non-inductive variable resistor(R 3), two capacitors(C 1 andC 2), three diodes (D 1, D 2 and D 3) and connecting terminals. Formula :- Duration of the output pulse generated or time duration of quasi-stable state ̘̊ƍ̘̋ T = 2.303 x R3C1 log 10 ( ʛ Sec ̘̊ Where R1 and R 2 = Fixed non-inductive resistances ( Ω) R3 = Variable non-inductive resistance ( Ω) C1 = Capacitance ( μF) and if R1 = R 2 Then T = 0.693 R 3 C1 Figure P.S. Brahma Chary Page 2 of 5 Description :- The above figure is the circuit of the monostable multi vibrator. A capacitor C 1 is connected to the inverting terminal (2) of the operational amplifier from the ground and a diode D1 is connected in parallel to C 1 such that n of diode D 1 is grounded. Similarly a series combination of a capacitor C2 another diode D 2 is connected to the non-inverting terminal (3) of the operational amplifier as shown in the figure. The junction of C 2 and D 2 is grounded through a resistor R 4. The in put external triggering pulse is given to the capacitor C 2. -

Op Amp Circuits Schmitt Trigger, Monostable, and Astable Circuits

M.B. Patil, IIT Bombay 1 Op Amp Circuits Schmitt Trigger, Monostable, and Astable Circuits Positive and negative feedback The inverting amplifier circuit is shown in Fig. 1(a). Let us show qualitatively that the Vi Vi Vo Vo R2 R2 R1 R1 (a) (b) Figure 1: (a)Inverting amplifier, (b)Schmitt trigger. feedback in this circuit is negative. Consider an increase in the output voltage Vo. This causes R1 an increase in V− = Vo. Since the op amp output is Vo = AV (Vs − V−), an increase in R1 + R2 V− causes Vo to decrease. We see that there is a balancing process here: an increase in Vo has resulted in a decrease in Vo. The circuit is therefore stable, with the op amp operating in the linear region1. Consider now the circuit in Fig. 1(b), which is identical to the inverting amplifier except that the inverting and non-inverting inputs of the op amp have been interchanged. Imagine once R1 again Vo to have increased. Consequently, V+ = Vo also increases, and Vo = AV (V+ −Vs) R1 + R2 increases further. The feedback process is now positive, making the circuit unstable. In practice, the op amp output cannot increase or decrease indefinitely and saturates at +Vsat or −Vsat. Is such an unstable circuit of any use at all? It surely is, as we will see in this experiment. Vo versus Vi relationship When Vs is sufficiently large, the ouput voltage Vo of the circuit of Fig. 1(b) (known as the “Schmitt trigger”) is −Vsat as shown in Fig. 2. -

555 Timer As Monostable Multivibrator

555 TIMER AS MONOSTABLE MULTIVIBRATOR A monostable multivibrator (MMV) often called a one-shot multivibrator, is a pulse generator circuit in which the duration of the pulse is determined by the R-C network,connected externally to the 555 timer. In such a vibrator, one state of output is stable while the other is quasi-stable (unstable). For auto-triggering of output from quasi-stable state to stable state energy is stored by an externally connected capacitor C to a reference level. The time taken in storage determines the pulse width. The transition of output from stable state to quasi-stable state is accomplished by external triggering. The schematic of a 555 timer in monostable mode of operation is shown in figure. 555-timer-monostable-multivibrator Monostable Multivibrator Circuit details Pin 1 is grounded. Trigger input is applied to pin 2. In quiescent condition of output this input is kept at + VCC. To obtain transition of output from stable state to quasi-stable state, a negative-going pulse of narrow width (a width smaller than expected pulse width of output waveform) and amplitude of greater than + 2/3 VCC is applied to pin 2. Output is taken from pin 3. Pin 4 is usually connected to + VCC to avoid accidental reset. Pin 5 is grounded through a 0.01 u F capacitor to avoid noise problem. Pin 6 (threshold) is shorted to pin 7. A resistor RA is connected between pins 6 and 8. At pins 7 a discharge capacitor is connected while pin 8 is connected to supply VCC.