LM555 Timer Datasheet (Rev. D)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

OMAP2430 Applications Processor

TM Technology for Innovators OMAP2430 applications processor All-in-One Key features entertainment • Advanced Imaging, Video and Audio Accelerator (IVA™ 2) boosts video for 3G mobile performance in mobile phones by up to 4X and imaging performance by up to 1.5X phones • Delivering a multimedia experience with consumer electronics quality to the handset • Multi-engine parallel processing architecture for supporting complex usage scenarios • Built-in M-Shield™ mobile security technology enables value-added services and terminal security • Support for all major High Level Operating Systems (HLOS) aids applications development PRODUCT BULLETIN Leading imaging The new OMAP2430 processor from Texas Instruments (TI) delivers a new and video level of multimedia performance to third-generation (3G) mobile phones and performance other handheld systems. Leveraging TI’s proven OMAP™ 2 architecture, the OMAP2430 features an advanced imaging, video and audio accelerator (IVA™ 2) that provides a 4X improvement in video processing and 1.5X improvement in image processing over previously available solutions for mobile phones. The processor’s high video performance enables advanced codec algorithms that promote higher compression ratios allowing networks to support more data, bringing down costs for service providers and allowing them to deploy revenue- generating services such as mobile digital TV and mobile-to-mobile gaming. Support for these services, plus high-resolution, high-speed decode of standard video compression algorithms, brings a TV-like viewing quality and the familiar features of consumer electronics to mobile communications. The OMAP2430 is optimized for the complex applications characteristic of 3G wireless communications. Offering even higher performance than first-generation OMAP 2 processors while at a lower cost, the OMAP2430 processor provides the ultimate balance between multimedia performance, flexibility, power and cost. -

GS40 0.11-Μm CMOS Standard Cell/Gate Array

GS40 0.11-µm CMOS Standard Cell/Gate Array Version 1.0 January 29, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. -

Multivibrator Circuits

Multivibrator Circuits Bistable multivibrators Multivibrators Circuits characterized by the existence of some well defined states, amongst which take place fast transitions, called switching processes. A switching process is a fast change in value of a current or a voltage, the fast process implying the existence of positive reaction loops, or negative resistances. The switching can be triggered from outside, by means of command signals, or from inside, by slow charge accumulation and the reaching of a critical state by certain electrical quantities in the circuit. Circuits have two, well defined states, which can be either stable or unstable A stable state is a state, in which the circuit, in absence of a driving signal, can remain for an unlimited period of time The circuit can remain in an unstable state only for a limited period of time, after which, in the absence of any exterior command signals, it switches into the other state. The multivibrator circuits can be grouped, according to their number of stable (steady) states, into: - flip-flops (bistable circuits) with both states being stable - monostable circuits , having a stable and an unstable state - astable circuits , with both states being unstable Flip-flop circuits The main feature of the flip-flop circuits is the existence of two stable states, in which the circuit may remain for a long time. The switching from one state to the other is triggered by command signals Flip flop: an example for a sequential circuit (a circuit with outputs that present logical values depending on a certain sequence of signals, that have previously existed in the circuit). -

Integrated Step-Down Converter with SVID Interface for Intel® CPU

Product Order Technical Tools & Support & Folder Now Documents Software Community TPS53820 SLUSE33 –FEBRUARY 2020 Integrated Step-Down Converter with SVID Interface for Intel® CPU Power Supply 1 Features 3 Description The TPS53820 device is D-CAP+ mode integrated 1• Single chip to support Intel VR13.HC SVID POL applications step-down converter for low current SVID rails of Intel CPU power supply. It provides up to two outputs to • Two outputs to support VCCANA (5.5 A) and power the low current SVID rails such as VCCANA P1V8 (4 A) (5.5 A) and P1V8 (4 A). The device employs D-CAP+ • D-CAP+™ Control for Fast Transient Response mode control to provide fast load transient • Wide Input Voltage (4.5 V to 15 V) performance. Internal compensation allows ease of use and reduces external components. • Differential Remote Sense • Programmable Internal Loop Compensation The device also provides telemetry, including input voltage, output voltage, output current and • Per-Phase Cycle-by-Cycle Current Limit temperature reporting. Over voltage, over current and • Programmable Frequency from 800 kHz to 2 MHz over temperature protections are provided as well. 2 • I C System Interface for Telemetry of Voltage, The TPS53820 device is packaged in a thermally Current, Output Power, Temperature, and Fault enhanced 35-pin QFN and operates between –40°C Conditions and 125°C. • Over-Current, Over-Voltage, Over-Temperature (1) protections Table 1. Device Information • Low Quiescent Current PART NUMBER PACKAGE BODY SIZE (NOM) • 5 mm × 5 mm, 35-Pin QFN, PowerPAD Package TPS53820 RWZ (35) 5 mm × 5 mm (1) For all available packages, see the orderable addendum at 2 Applications the end of the data sheet. -

Npn Transistor Pnp Transistor

ELL 100 - Introduction to Electrical Engineering LECTURE 23: BIPOLAR JUNCTION TRANSISTOR (BJT) 1 CONTENTS • Introduction • Construction & working principle of BJT • Common-base and common-emitter circuits 2 BJT INTRODUCTION • Bipolar: Both electrons and holes (positively charged quasi- particles, absence of electron) contribute to current flow • Junction: Consists of an n- (or p-) type silicon sandwiched between two p- (or n-) type silicon regions • Transistor: 3-terminal device (Base, Emitter, Collector) Two types: npn & pnp 3 Bipolar Junction Transistor (BJT) 4 Various Types of General-Purpose or Switching Transistors: (a) Low Power (b) Medium Power (c) Medium to high power 5 First Working Transistor, Invented in 1947. Earliest Raytheon Blue transistors, Replica of 1st device made by first appearing in 1955 Shockley, Bardeen & Brattain at Bell Labs 6 Applications: Transistor As Switch 7 Applications: Transistor As Relay (Switch) Single channel 5V relay breakout board 8 Applications: Transistor As Amplifier TDA7297 Power Amplifier & Audio amplifier Module 9 Applications: Transistors in Radio 10 Applications: Transistor in Oscillator Colpitts Oscillator 11 Applications: Transistor in Oscillator Astable Multivibrator 12 Transistors in Timer Circuits 13 Transistor As NOT Gate 14 Transistors in NAND Gate 15 Bipolar Junction Transistor (BJT) The three terminals of the BJT are called the Base (B), the Collector (C) and the Emitter (E). n p p n n p npn transistor pnp transistor 16 Bipolar Junction Transistor (BJT) npn pnp 17 p-n-p Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 18 n-p-n Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 19 BJT Construction 20 Bipolar Junction Transistor (BJT) Basic Principle The voltage between two terminals (B and E) controls the current through the third terminal (C). -

Chapter 3: Oscillators and Waveform-Shaping Circuits

mywbut.com CHAPTER3:OSCILLATORSANDWAVEFORM-SHAPING CIRCUITS Inthedesignofelectronicsystems,theneed frequentlyarises forsignals havingprescribed standardwaveforms(e.g.,sinusoidal, square,triangle,pulse,etc).Thesewaveformsarecommonly usedincomputers,controlsystems,communicationsystemsandtestmeasurementsystems. Therearetwocommonwaysforgeneratingsinusoids: 1. Positivefeedbackloopwithnon-lineargainlimiting 2. Appropriatelyshapingotherwaveformssuchasatrianglewaves. Circuitsthatdirectlygeneratesquare,triangleandpulsewaveformsgenerallyemploycircuit blocksknownasmultivibrators.Threebasictypesarebistable,astableandmonostable. I.SINUSOIDALOSCILLATORS: Commonly referred to as linear sine-wave oscillators although some forms of non-linearity havetobeemployedtolimittheoutputamplitude.Analysisofthecircuitsismoredifficultass-plane analysis cannot be directly applied to the non-linear part of the circuit. The basic structure of a sinusoidal oscillator consists of an amplifier and a frequency selective network connected in a positivefeedbackloop. AmplifierA xS + Σ xO + xf Freq.Selective networkβ Figure1:Basicstructureofasinusoidaloscillator. Apositive-feedbackloopisformedbyanamplifierandafrequency-selectivenetwork.Inan actualoscillatorcircuit,noinputsignalwillbepresent;hereaninputsignalxsisemployedtohelp explaintheprincipleofoperation.NotethatthefeedbacksignalXFissummedwithapositivesign: A(s) A (s) = f 1− A(s) β (s) Theloopgainis: )s(L =A(s) β (s) Andthecharacteristicequationcanbewrittenas: 1-L(s)=0 If at a specific frequency -

Notes to Portfolio of Investments—March 31, 2021 (Unaudited)

Notes to portfolio of investments—March 31, 2021 (unaudited) Shares Value Common stocks: 99.36% Communication services: 9.92% Interactive media & services: 8.14% Alphabet Incorporated Class C † 4,891 $ 10,117,669 Facebook Incorporated Class A † 21,120 6,220,474 16,338,143 Wireless telecommunication services: 1.78% T-Mobile US Incorporated † 28,582 3,581,039 Consumer discretionary: 10.99% Automobiles: 1.91% General Motors Company † 66,899 3,844,017 Internet & direct marketing retail: 3.59% Amazon.com Incorporated † 2,329 7,206,112 Multiline retail: 1.69% Dollar General Corporation 16,717 3,387,199 Specialty retail: 3.80% Burlington Stores Incorporated † 15,307 4,573,732 Ulta Beauty Incorporated † 9,936 3,071,913 7,645,645 Consumer staples: 2.81% Food & staples retailing: 1.60% Sysco Corporation 40,883 3,219,127 Household products: 1.21% Church & Dwight Company Incorporated 27,734 2,422,565 Financials: 7.38% Capital markets: 4.85% CME Group Incorporated 7,970 1,627,713 Intercontinental Exchange Incorporated 24,575 2,744,536 S&P Global Incorporated 9,232 3,257,696 The Charles Schwab Corporation 32,361 2,109,290 9,739,235 Insurance: 2.53% Chubb Limited 13,181 2,082,203 Marsh & McLennan Companies Incorporated 24,610 2,997,498 5,079,701 Health care: 14.36% Biotechnology: 1.11% Alexion Pharmaceuticals Incorporated † 14,516 2,219,642 Health care equipment & supplies: 6.29% Align Technology Incorporated † 5,544 3,002,242 Boston Scientific Corporation † 79,593 3,076,269 See accompanying notes to portfolio of investments Wells Fargo VT Opportunity -

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC 555 AIM To design and set up astable multivibrator of 1000 Hz frequency and 60% duty cycle using IC 555 THEORY IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series connection of three resistors inside the IC sets the reference voltage levels to the two 2 1 comparators at V and V , the output of these comparators setting or resetting the flip- 3 CC 3 CC flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage. In the stable state the 푄 output of the flip-flop is high (ie Q low). This makes the output (pin 3) low because of the buffer which basically is an inverter.The flip-flop circuit also operates a transistor inside the IC, the transistor collector usually being driven low to discharge a timing capacitor connected at pin 7. The description of each pin s described below, Pin 1: (Ground): Supply ground is connected to this pin. Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator. When trigger of amplitude greater than (1/3)Vcc is applied to this terminal circuit switches to quasi-stable state. Pin 3: (Output) Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low at this pin will reset output. For normal operation pin 4 is connected to Vcc. -

An Electronic Switch ?Or Transient Studies

AN ELECTRONIC SWITCH ?OR TRANSIENT STUDIES A THESIS Presented to the Faculty of the Division of Graduate Studies Georgia Institute of Technology In Partial Fulfillment of the Requirements for the Degree Master of Science in Slectrical Engineering by Marshall Joseph McCann September 1949 107545 ii AN ELECTRONIC SWITCH FOR TRANSIENT STUDIES Approved: zf r ~~v Bate Approved by Chairman A up. d±, f^4f ACKNOWLEDGMENTS I wish to express my sincerest thanks to Prof. M. A. Honnell for his patient guidance and assistance, which were an immense aid in the prosecution of this work. I am also indebted to the Photographic and Repro duction Laboratory at the State Engineering Experiment Station of the Georgia Institute of Technology for their splendid cooperation with the photographic work herein. iv TABLE 0? CONTENTS PAGE Acknowledgments iii List of figures vi I- Introduction 1 II- A Survey of the Literature 3 Mechanical Systems.. • 3 Electronic Systems 4 III- Design Considerations for an Electronic Switch 8 General , , 8 Possible Approaches 8 IV- The Switch 12 V- The Square Wave Generator 16 Design Requirement s 16 Symmetrical Multivibrator 16 Improvement of Waveform 22 VI- The Synchronizing Section 37 General 37 Phase Shifting 27 Amplification and V/ave shaping 29 Synchronization of the Multivibrator 39 Summary of the Synchronizing Action 31 VII- Operation 34 VIII- Siamples of Operation 37 Lumped Constant Circuits 37 V P-4GE VIII- Examples of Operation (continued) Transmission Line Transients 41 IX- Summary • 46 appendix I, Analysis of Plate-Inductance Compensation of the Multivibrator 47 appendix II, Scaling of Circuits for A-C Transients 50 appendix III, Parts List 55 Bibliography ... -

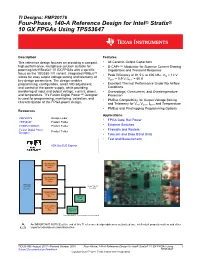

4-Phase, 140-A Reference Design for Intel® Stratix® 10 GX Fpgas Using

TI Designs: PMP20176 Four-Phase, 140-A Reference Design for Intel® Stratix® 10 GX FPGAs Using TPS53647 Description Features This reference design focuses on providing a compact, • All Ceramic Output Capacitors high-performance, multiphase solution suitable for • D-CAP+™ Modulator for Superior Current-Sharing powering Intel®Stratix® 10 GX FPGAs with a specific Capabilities and Transient Response focus on the 1SG280-1IV variant. Integrated PMBus™ • Peak Efficiency of 91.5% at 400 kHz, VIN = 12 V, allows for easy output voltage setting and telemetry of V = 0.9 V, I = 60 A key design parameters. The design enables OUT OUT programming, configuration, smart VID adjustment, • Excellent Thermal Performance Under No Airflow and control of the power supply, while providing Conditions monitoring of input and output voltage, current, power, • Overvoltage, Overcurrent, and Overtemperature and temperature. TI's Fusion Digital Power™ Designer Protection is used for programming, monitoring, validation, and • PMBus Compatibility for Output Voltage Setting characterization of the FPGA power design. and Telemetry for VIN, VOUT, IOUT, and Temperature • PMBus and Pinstrapping Programming Options Resources Applications PMP20176 Design Folder • FPGA Core Rail Power TPS53647 Product Folder CSD95472Q5MC Product Folder • Ethernet Switches Fusion Digital Power • Firewalls and Routers Product Folder Designer • Telecom and Base Band Units • Test and Measurement ASK Our E2E Experts CSD95472Q5MC Smart Power Stage CSD95472Q5MC Smart Power Stage TPS53647 ® Four-Phase Stratix 10 GX Controller Core Rail CSD95472Q5MC Smart Power Stage Onboard Load Generator CSD95472Q5MC Smart Power Intel® Load Stage Slammers Copyright © 2017, Texas Instruments Incorporated An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information. -

How to Configure a 555 Timer IC 555 Timer Tutorial

How To Configure a 555 Timer IC 555 Timer Tutorial By Philip Kane The 555 timer was introduced over 40 years ago. Due to its relative simplicity, ease of use and low cost it has been used in literally thousands of applications and is still widely available. Here we describe how to configure a standard 555 IC to perform two of its most common functions - as a timer in monostable mode and as a square wave oscillator in astable mode. 555 Timer Tutorial Bundle Includes: Qty. Description Manufacturer P/N 1 Standard Timer Single 8-Pin Plastic Dip Tube NE555P 1 400-Point Solderless Breadboard 3.3"L x 2.1"W WBU-301-R 10 Resistor Carbon Film 10kΩ CF1/4W103JRC 1 9V Alkaline Battery ALK 9V 522 1 9V Battery Snap with 6" 26AWG Leads BC6-R 2 3-Pin SPDT Slide Switch SS-12E17 2 Radial Capacitor 0.01µF 2.54mm Bulk SS-12E17 1 Radial Capacitor 4.7µF 2.5mm Bulk TAP475K025SCS-VP 10 Resistor Carbon Film 1.0MΩ 1/4 Watt 5% CF1/4W105JRC 10 Resistor Carbon Film 220Ω 1/4 Watt 5% CF1/4W221JRC 10 LED Uni-Color Red 660nm 2-Pin T-1¾ Box UT1871-81-M1-R 100 Resistor Carbon Film 3kΩ 1/4 Watt 5% CF1/4W302JRC 10 Resistor Carbon Film 330kΩ 1/4 Watt 5% CF1/4W334JRC 1 Radial Capacitor 1µF 25 Volt 2.5mm Bulk TAP105K025SCS-VP 555 Signals and Pinout (8 pin DIP) Figure 1 shows the input and output signals of the 555 timer as they are arranged around a standard 8 pin dual inline package (DIP). -

GS30 Product Overview

GS30 0.15-µm CMOS Standard Cell/Gate Array Version 1.0 February, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.