AN4030 Gate to Cathode Capacitor, Impact on Triac Immunity And

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

TRIAC Overvoltage Protection Using a Transil™

AN1966 Application note TRIAC overvoltage protection using a Transil™ Introduction In most of their applications, TRIACs are directly exposed to overvoltages coming from the mains, as described in IEC 61000-4-5 or IEC 61000-4-4 standards. When TRIACs are used to drive resistive loads (ex: temperature regulation), it is essential to provide them with efficient overvoltage protection to prevent any turn-on in breakover mode that could lead to device damage. A traditional method to clamp the voltage is to use a varistor in parallel across the TRIAC. But with high power loads (a few kW), the current through the varistor is very high in case of surge voltages (a few hundred amperes). The varistor is then not efficient enough, due to its dynamic resistor, to limit the TRIAC voltage to a low value. We present here a solution that can be used for these kinds of applications and also for all applications where TRIAC voltage protection is required. It should be noted that the overvoltages could also come from the overvoltages that appear at device turn-off due to the TRIAC holding current. This phenomenon occurs mainly with TRIACs controlling low rms current (15-50 mA), high inductive loads like valves. For more information about such behavior, please refer to AN1172. Contents 1 Why overvoltage protection is required . 2 2 Overvoltage protection solution . 3 3 Transil choice for efficient TRIAC voltage protection . 6 3.1 Normal operation: check VRM voltage . 6 3.2 Surge voltage clamping: check max VCL voltage . 6 4 Experimental validation example . 8 5 Conclusion . -

Triac Control with a Microcontroller Powered from a Positive Supply

AN440 Application note Triac control with a microcontroller powered from a positive supply Introduction This application note explains how to implement a control circuit to drive an AC switch (Triac, ACS or ACST) in case the microcontroller unit (MCU) is supplied with a positive voltage. The driving circuit will also depends on the kind of Triac used and also if other supplies (positive or negative) are available. We also deal about the case of insulated or non-insulated supplies. It is recommended to refer to AN4564 which explains why positive supplies are usually implemented and how simple solutions can be implemented to get a negative supply. Refer also to AN3168 for information about AC switch control circuits in case the microcontroller is supplied with a negative power supply. AN440 - Rev 4 - March 2020 www.st.com For further information contact your local STMicroelectronics sales office. AN440 Positive supply defintion and AC switch triggering quadrants 1 Positive supply defintion and AC switch triggering quadrants 1.1 Positive power supply A positive power supply is a supply where its reference level (VSS) is connected to the mains (line or neutral). The VDD level is then above the mains terminal as shown in Figure 1. If the supply is a 5 V power supply, then VDD is 5 V above the mains reference. This is why such a supply is called a positive supply (compared to a negative supply as shown in AN3168). Figure 1. Positive supply basic schematic 1.2 AC switch triggering quadrants To switch-on an AC switch, like any bipolar device, a gate current must be applied between its gate pin (G) and its drive reference terminal (refer also to AN3168). -

An Application of TRIAC to Capacitor Motor for Hermetic Compressor K

Purdue University Purdue e-Pubs International Compressor Engineering Conference School of Mechanical Engineering 1984 An Application of TRIAC to Capacitor Motor for Hermetic Compressor K. Nakane Y. Tozaki H. Sakamoto Follow this and additional works at: https://docs.lib.purdue.edu/icec Nakane, K.; Tozaki, Y.; and Sakamoto, H., "An Application of TRIAC to Capacitor Motor for Hermetic Compressor" (1984). International Compressor Engineering Conference. Paper 449. https://docs.lib.purdue.edu/icec/449 This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact [email protected] for additional information. Complete proceedings may be acquired in print and on CD-ROM directly from the Ray W. Herrick Laboratories at https://engineering.purdue.edu/ Herrick/Events/orderlit.html AN APPLICA'l'ION OF 'l'RIAC TO CAPACI'l'OR 1-10'l'OR FOR lll~Rt~IC'riC COMPRSSO!l Ka.zuhiro Nakane, Yasuhiro To?.nki,. Ilirota.ka Sakamoto Shizuoka. Worlw, Mitsubishi Electri.c Corporation Shizuoka City , Ja.pan ABSTRACT oncy and output rati.ngo are 100 V ,50/60 J!v. and 100 11. It is a. 1mi 1 t-in motor for the rotary type This paper refers to a.n n.pplication study of 'l'lUAC hermetic compressor shown in Ji'ie;. 2. 'l'hore are to PSC motor for thft hermetic compessor. It is three types of the wirings of the starting device 1-1ell lcnown that 'l'HIAC rlel nys pharJa ane,le of the for thifl motor,as shown i.n lcig, 3. A shows CSR current and has no losses if it is consider(\ as moto:r,n shows P'l'C asoist CSR motor and C sho~1s ideal flwitch. -

Thyristors & Triacs

APPLICATION NOTE Thyristors & Triacs - Ten Golden Rules for Success In Your Application. This Technical Publication aims to provide an threshold current IGT, within a very short time known as interesting, descriptive and practical introduction to the the gate-controlled turn-on time, tgt, the load current can golden rules that should be followed in the successful flow from ’a’ to ’k’. If the gate current consists of a very use of thyristors and triacs in power control applications. narrow pulse, say less than 1µs, its peak level will have to increase for progressively narrower pulse widths to Thyristor guarantee triggering. A thyristor is a controlled rectifier where the When the load current reaches the thyristor’s latching unidirectional current flow from anode to cathode is current IL, load current flow will be maintained even after initiated by a small signal current from gate to cathode. removal of the gate current. As long as adequate load current continues to flow, the thyristor will continue to akconduct without the gate current. It is said to be latched ON. Note that the VGT,IGT and IL specifications given in data g are at 25 ˚C. These parameters will increase at lower temperatures, so the drive circuit must provide adequate Fig. 1. Thyristor. voltage and current amplitude and duration for the The thyristor’s operating characteristic is shown in lowest expected operating temperature. Fig. 2. Rule 1. To turn a thyristor (or triac) ON, a gate current On-state ≥ Forward IGT must be applied until the load current is current characteristic ≥ IL. This condition must be met at the lowest expected operating temperature. -

How to Implement a SCR Or a Triac in a Hybride Relay Application

AN4993 Application note How to implement an SCR or a Triac in hybrid relay applications Introduction This document gives some key information about the design of the solid-state silicon AC switch stage of a hybrid relay, which can drive resistive, capacitive or inductive AC loads, such as: heater resistors, motors for industry, power tools or appliance applications. Section 1 describes the hybrid relay principle. Circuit and functional diagram is the first topic to be handled followed by its advantages and drawbacks and finally the main targeted applications are listed. Section 2 specifies different ways to drive the AC switch implemented on the hybrid relay circuit. Section 3 provides some design tips to pass electromagnetic compatibility standards, especially to reduce EMI noise. March 2017 DocID030191 Rev 1 1/23 www.st.com Contents AN4993 Contents 1 Hybrid relay ...................................................................................... 5 1.1 General schematic ............................................................................ 5 1.2 Advantages and drawbacks .............................................................. 6 1.3 Applications ....................................................................................... 7 1.3.1 Water and room heaters ..................................................................... 7 1.3.2 Home automation smart plug ............................................................. 7 1.3.3 Inrush limiter for power supply .......................................................... -

Issues, Models and Solutions for Triac Modulated Phase Dimming of LED Lamps

Issues, Models and Solutions for Triac Modulated Phase Dimming of LED Lamps Dustin Rand (Raytheon), Brad Lehman* (Northeastern University), Anatoly Shteynberg (Exclara, Inc.) *Dept. ECE; Northeastern University; Boston, MA 02115; [email protected] Abstract - This paper discusses the difficulties in dimming Edison metric tons of carbon emission, as well as alleviate the need of socket LED lamps directly from residential phase modulated more than 40 1000MW power stations [9,10]. dimmer switches. In order to explain these difficulties PSpice Dimmers models for the dimmers are proposed that necessarily include Residential dimmers are designed to meet the needs of diac characteristics to improve accuracy. A method to dim the homeowners and architects in both style and function. LEDs from the residential dimmers is discussed. Commercial companies offer a complete line of residential dimmers with an amazing array of colors that coordinate with the most popular interior colors and finishes. Commercial I. INTRODUCTION: LED LIGHTING - THE NEXT dimmers and dimming systems are designed to meet the TECHNOLOGICAL REVOLUTION? requirements of architects and specifiers of commercial spaces such as hotels, restaurants, offices and warehouses. Within the last few years, new LED materials and What is a Phase Modulated Dimmer? improved production processes have resulted in bright LEDs Incandescent bulbs primarily utilize phase modulating in colors throughout the visible spectrum with efficacies dimming through triac switches to control the power sent to greater than incandescent lamps [1,2]. In fact, recent the bulb. Dimming fluorescent lighting is possible by technological breakthroughs [3-7] in the high brightness retrofitting the lighting switches/infrastructure with electronic “White Light” LEDs have experts predicting that the “bright or other dimming ballasts. -

AN3168 Non-Insulated SCR / Triac Control Circuits

AN3168 Application note Non-insulated SCR / Triac control circuits Introduction In alternating current applications the direct current power supply for low-voltage electronic devices (MCU, LEDs, optocouplers, Triacs and so on) can be provided using one of several different circuits. There are traditionally two major types of power supplies used in appliances, capacitive power supply and linear power supply using a step-down transformer. Today, designers are using more and more switches mode power supplies (SMPS) to achieve higher output current levels and especially lower standby power consumption. The power supply choice is a trade-off between several parameters. These are the cost, the required power, the output voltage level and polarity, the standby power consumption and the necessity or not of an electrical insulation between the mains and the low output DC voltage. This application note considers only non-insulated power supplies. After a brief description of the triggering quadrants and key parameters for SCR, Triac, ACS and ACST, the usual control circuits are described according to the output voltage polarity of the power supply. Finally, some examples of negative power supply circuits are introduced. March 2010 Doc ID 17193 Rev 1 1/20 www.st.com AN3168 Contents Contents 1 Triggering quadrants and key parameters . 3 2 Triggering circuits . 6 2.1 Two kind of power supply bias . 6 2.2 Gate resistor value definition . 6 2.3 SCR and Triac triggering circuit with a positive power supply . 7 2.4 Triac and ACS / ACST triggering circuit with negative power supply . 8 2.5 SCR triggering circuit with negative power supply . -

Thyristors and Triacs Control Gate Trigger Circuits

1 Lab no. 3 THYRISTORS AND TRIACS CONTROL GATE TRIGGER CIRCUITS 1. Introduction The thyristor is a power semiconductor device with the control terminal called grid or gate (G). The device name comes from the similarity of operation with the gas triode: thiratron transistor. Because the thyristors are mainly used in the controlled rectifier structures, the technical literature calls them as SCR (Semiconductor Controlled Rectifiers) devices. After the series manufacture start in 1957 until the ‘80s of the twentieth century the thyristor was the leader of power semiconductor devices with control electrode. Despite the fact that the thyristor is a half controlled device (through the gate terminal can be only turned on) this switch remains favourite in a wide range of applications because it is robust, can be easily controlled and can operates in high power structures at high voltages and currents with low power conduction losses. To operate, every thyristor require a drive (trigger, control) circuit that provides gate current pulses to induce the on-state. These pulses must have a certain amplitude and duration. The device remains latched in on-state until it is reverse biased. Thus, in forward biased conditions, after the turn-on process, the gate current can be interrupted. Thyristors can be found in various applications such as phase-controlled rectifiers, AC voltage variators, starters, static breakers, cycloconverters, etc. Depending on the requirements, are available on the market several types of thyristors: common thyristors (used in phase-controlled converters at low switching frequency, high voltages and currents), fast thyristors (with a small blocking time), optical thyristors (light-activated through optical fibers), etc. -

Thyristors Triacs Precautions For

Common Item R07ZZ0011EJ0200 Thyristor・Triac (Previous: REJ27G0020-0100) Rev.2.00 Precautions for Use Aug.7.2019 Contents 1. Use of Thyristors ..................................................................................................................................... 2 (1) How to select current rating .............................................................................................................................. 2 (2) How to select withstanding voltage class........................................................................................................ 2 (3) Cautions on dv/dt ................................................................................................................................................ 3 (4) Cautions on di/dt ................................................................................................................................................. 3 (5) Measures to prevent false triggering ............................................................................................................... 3 2. Use of Triacs ........................................................................................................................................... 4 (1) How to select current rating .............................................................................................................................. 4 (2) How to select withstanding voltage class........................................................................................................ 4 (3) -

TRIAC Specifications and Recommendations (Turn‐On Behavior)

White Paper TRIAC Specifications and Recommendations (Turn‐On Behavior) 5110 Roanoke Place Suite 101 College Park, MD 20740 ph: 301-474-0607 fax: 240-757-2195 www.dfrsolutions.com [email protected] Unless otherwise indicated, this presentation is considered a draft report Introduction Wiki defines a TRIAC as an electronic component approximately equivalent to two silicon‐controlled rectifiers (SCRs/thyristors) joined in inverse parallel (paralleled but with the polarity reversed) and with their gates connected together. This results in a bidirectional electronic switch which can conduct current in either direction when it is triggered (turned on) and thus doesn't have any polarity. It can be triggered by either a positive or a negative voltage being applied to its gate electrode. Once triggered, the device continues to conduct until the current through it drops below a certain threshold value, the holding current, such as at the end of a half‐cycle of alternating current (AC) main power. This makes the TRIAC a very convenient switch for AC circuits, allowing the control of very large power flows with milliampere‐scale control currents. In addition, applying a trigger pulse at a controllable point in an AC cycle allows one to control the percentage of current that flows through the TRIAC to the load (phase control). OVERVIEW DfR was requested by a customer to identify the critical triac part parameters and determine the margins necessary to ensure the successful operation of their Modular control system. The current triac used is a sensitive gate type. Turn on control circuit o Turn on (latch) when you apply the triggering voltage to the gate and support the valve station current and voltage output to energize the specified number and type of solenoid loads . -

RC Snubber Circuit Design for Triacs

AN437 Application note RC snubber circuit design for TRIACs Introduction When a TRIAC controls inductive loads, the mains voltage and the load current are not in phase. To limit the slope of the reapplied voltage and ensure right TRIAC turn-off, designer usually used a snubber circuit connected in parallel with the TRIAC. This circuit can also be used to improve TRIAC immunity to fast transient voltages. The subject of this paper is, first of all, to analyze the snubber circuit functions and to propose a method for snubber circuit design in order to improve turn-off commutation. Contents 1 Snubber circuit functions and drawback . 2 1.1 Turn-off improvement . 2 1.1.1 TRIAC turn-off reminder . 2 1.1.2 Snubber circuit benefit at TRIAC turn-off . 3 1.2 Overvoltage limitation at turn-off . 4 1.3 Immunity to fast voltage transient improvement . 5 1.4 Turn-on stress due to snubber circuit discharge . 5 2 How to design snubber circuit for turn-off improvement . 7 2.1 Step response of an RLC series circuit . 7 2.2 RC snubber circuit design . 9 2.2.1 Is the snubber circuit required? . 9 2.2.2 Resistor and capacitor snubber circuit design . 10 3 Conclusion . 14 Appendix A RLC series circuit step response explanation . 15 Revision history . 17 October 2007 Rev 2 1/18 www.st.com Snubber circuit functions and drawback AN437 1 Snubber circuit functions and drawback 1.1 Turn-off improvement 1.1.1 TRIAC turn-off reminder When a TRIAC switches from on-state to off-state, the current passes through zero and the supply voltage is reapplied instantaneously across the structure. -

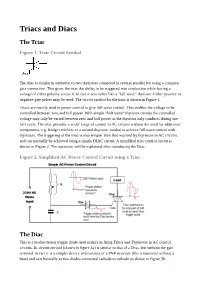

Triacs and Diacs the Triac

Triacs and Diacs The Triac Figure 1. Triac Circuit Symbol The triac is similar in operation to two thyristors connected in reverse parallel but using a common gate connection. This gives the triac the ability to be triggered into conduction while having a voltage of either polarity across it. In fact it acts rather like a "full wave" thyristor. Either positive or negative gate pulses may be used. The circuit symbol for the triac is shown in Figure 1. Triacs are mainly used in power control to give full wave control. This enables the voltage to be controlled between zero and full power. With simple "half wave" thyristor circuits the controlled voltage may only be varied between zero and half power as the thyristor only conducts during one half cycle. The triac provides a wider range of control in AC circuits without the need for additional components, e.g. bridge rectifiers or a second thyristor, needed to achieve full wave control with thyristors. The triggering of the triac is also simpler than that required by thyristors in AC circuits, and can normally be achieved using a simple DIAC circuit. A simplified triac control circuit is shown in Figure 2. The operation will be explained after introducing the Diac. Figure 2. Simplified AC Power Control Circuit using a Triac The Diac This is a bi-directional trigger diode used mainly in firing Triacs and Thyristors in AC control circuits. Its circuit symbol (shown in figure 3a) is similar to that of a Triac, but without the gate terminal, in fact it is a simpler device and consists of a PNP structure (like a transistor without a base) and acts basically as two diodes connected cathode to cathode as shown in figure 3b.