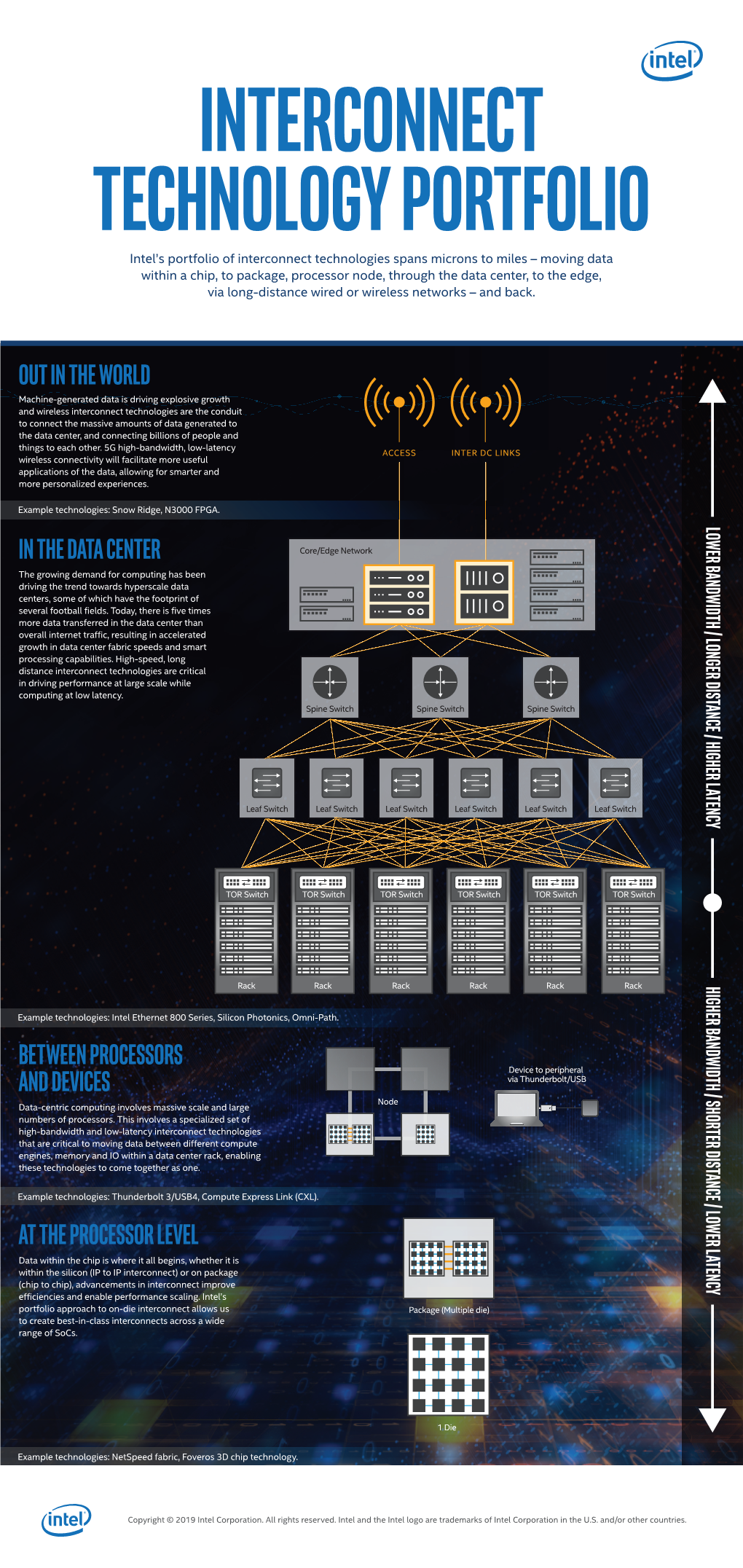

Interconnect Infographic

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Summit™ M5x Protocol Analyzer / Jammer for PCI Express® 5.0

Summit™ M5x Protocol Analyzer / Jammer for PCI Express® 5.0 The Summit M5x is Teledyne LeCroy’s highest performance PCI Express analyzer, Key Features offering both inline probing and direct tapping approaches to protocol capture - the best in overall diversity in probing methods. Find errors fast • One button error check Inline operation provides advanced features such as: real-time error injection (jammer) • Fast upload speed for PCI Express 4.0 specification; support for data rates of 2.5 GT/s, 5.0 GT/s, 8.0 • Large trace memory GT/s, and 16.0 GT/s; full data capture on bidirectional link widths of x1, x2, x4, x8 and • Powerful triggering/filtering x16 for up to 16 GT/s; and up to 128GB of trace memory. See and understand the traffic ® • Get useful information Direct tapping operation supports PCIe 5.0 protocol analysis with speeds up to • More choices of data views 32GT/s at up to x8 link widths. The Summit M5x is ideal for high-performance protocol • More ways to analyze data development of add-in boards, switches, servers and workstations, and for customers • Custom decoding and reports currently working on PCIe. Data capture Flexible Hardware Analyzer for CXL (Compute Express Link) Links. • 100% data capture at 32.0 GT/s The Summit M5x PCIe 5.0 Protocol Analyzer is a Support is provided for CXL.io, CXL.mem and high-end analyzer that offers important analysis CXL.cache with full decoding from the FLIT layer Deep memory buffer features for new application development. to the CXL Message layers. -

Multiport M.2 NGFF PS/2 HDMI Firewire Network SATA IDE Mini

Connection-Know-How www.delock.com RF Memory SATA Displayport Graphics / Video radio frequency technology Cards SATA SATA male female Dualport HDMI + Displayport Cinch Video Cinch Video Cfast female female male female N plug F plug eSATA SATA male female S-Video female Compact Flash female Sub-D Displayport Displayport male female eSATAp eSATAp TNC Coaxial NEW male female Scart male plug plug Serial Serial mini mini 9 pin 9 pin Displayport Displayport Contact Golden Strip male female male female eSATApd male SD SD 4.0 DMS male DMS female female female RP-TNC RP-TNC UHS-I-Card UHS-II-Card plug jack Slim SATA 13 pin male Null Modem 8 pin male HDMI VGA Micro SATA 16 pin VGA Parallel 25 pin male female M.2 NGFF male male HDMI A HDMI A FME FME male female plug jack M.2 NGFF Key B+M Micro SATA 16 pin female Parallel 25 pin female VHDCI-68 male HDMI HDMI mini-C mini-C M.2 NGFF Key B male female SATA 22 pin male BNC BNC Sub-D 15 pin Gameport VHDCI-68 female plug jack male M.2 NGFF Key M SATA 22 pin female HDMI HDMI micro-D micro-D male female Sub-D 15 pin Gameport SMA SMA female LFH 60 male plug jack mini PCIe SAS male Multiport Sub-D 37 pin male PS/2 miniPCIe female mSATA female RP-SMA RP-SMA NEU plug jack BNC Stecker miniPCIe male mSATA male Sub-D 37 pin female Multiport female BNC Buchse PS/2 female SMB SMB plug jack Audio USB Mobile DVI FireWire MCX MCX plug jack Audio Stereo iPhone 30 pin female DVI-D Dual Link 24+1 USB 2.0 A USB 2.0 A FireWire A FireWire A female male male female 6 pin 6 pin male female UHF UHF Stereo 3 pin Stereo 3 pin -

Thunderbolt™-To- 8Gb/S Fibre Channel Desklink™ Device Thunderlink™ FC 1082

Tech Sheet Thunderbolt™-to- 8Gb/s Fibre Channel Desklink™ Device ThunderLink™ FC 1082 ATTO’s 8Gb/s Fibre Channel to Thunderbolt Desklink Technical Features Device product provides the highest performing SAN • Dual 8Gb/s Fibre Channel Ports storage connectivity for content creation, streaming • (2) Optical SFPs+ included media and high performance and low latency workflows. • Dual 10Gbps Thunderbolt with Display Industry Proven Technology Port and PCIe Support ATTO has over 25 years of experience developing first-to-market high performance and • Thunderbolt certified for Mac and PC reliable storage connectivity solutions for customers. ATTO ThunderLink Fibre Channel products now provide creative professionals using Thunderbolt-enabled hosts, cost • Dual ports enable daisy-chaining up effective access to storage not previously available using FireWire or USB. The integrated to six devices family of ThunderLink products boasts an extensive list of customer design wins and • Exclusive Advanced Data Streaming certifications with respected industry partners. (ADS™) Technology Flexible Connectivity Solutions • ATTO ConfigTool for customized performance settings With dual channel configuration, and support for load balancing and failover, the 8Gb/s Fibre Channel Desklink Devices are an ideal solution for users looking to achieve the highest • Proven interoperable with leading I/O and data throughput for advanced video and access to IT applications. ThunderLink storage hardware and software 8Gb/s Fibre Channel Desklink Devices offer driver support for Mac OS® X 10.6.8 and later vendors and Windows® 7 and 8.1 (Linux® when Thunderbolt enabled platforms become available), • Complete SAN connectivity when providing a single connectivity solution for customers with heterogeneous operating combined with ATTO FibreConnect system environments. -

SC20를 통해 본 HPC 기술 동향 HPC Technology Through SC20

Electronics and Telecommunications Trends SC20를 통해 본 HPC 기술 동향 HPC Technology Through SC20 어익수 (I.S. Eo, [email protected]) 슈퍼컴퓨팅기술연구센터 책임연구원 모희숙 (H.S. Mo, [email protected]) 슈퍼컴퓨팅기술연구센터 책임연구원 박유미 (Y.M. Park, [email protected]) 슈퍼컴퓨팅기술연구센터 책임연구원/센터장 한우종 (W.J. Han, [email protected]) 인공지능연구소 책임연구원/연구위원 ABSTRACT High-performance computing (HPC) is the underpinning for many of today’s most exciting new research areas, to name a few, from big science to new ways of fighting the disease, to artificial intelligence (AI), to big data analytics, to quantum computing. This report captures the summary of a 9-day program of presentations, keynotes, and workshops at the SC20 conference, one of the most prominent events on sharing ideas and results in HPC technology R&D. Because of the exceptional situation caused by COVID-19, the conference was held entirely online from 11/9 to 11/19 2020, and interestingly caught more attention on using HPC to make a breakthrough in the area of vaccine and cure for COVID-19. The program brought together 103 papers from 21 countries, along with 163 presentations in 24 workshop sessions. The event has covered several key areas in HPC technology, including new memory hierarchy and interconnects for different accelerators, evaluation of parallel programming models, as well as simulation and modeling in traditional science applications. Notably, there was increasing interest in AI and Big Data analytics as well. With this summary of the recent HPC trend readers may find useful information to guide the R&D directions for challenging new technologies and applications in the area of HPC. -

Drivestation™ Ultra Series PERFORMANCE MATTERS HD-D/R6, HD-HN/R6

DriveStation™ Ultra Series PERFORMANCE MATTERS HD-D/R6, HD-HN/R6 BLAZING FAST SPEEDS & LARGEST CAPACITY DESKTOP DAS IN THE INDUSTRY Bualo's DriveStationTM Ultra is a high performance, high capacity direct attached storage solution ideal for businesses that demand fast data transfer speeds for large les, such as 4k high resolution video. The DriveStation Ultra is available in either a ten-drive or six-drive desktop model, with capacities ranging from 12 TB to 80 TB, the largest capacity desktop DAS available today. With multi-interface support, Mac® users can experience blazing fast speeds using a Thunderbolt 2 connector, while PC users can also connect through high-speed USB 3.0 and eSATA interfaces. RAID 6 support provides extra protection that allows up to two hard drives to fail without data loss. The DriveStation Ultra is equipped with either enterprise or NAS hard drives designed for continuous operation. Extremely fast data transfers for both Mac and PCs and safe data storage with RAID options make the DriveStation Ultra an ideal solution for storing large les quickly and safely. FEATURES THUNDERBOLT 2 SPEEDS HIGH PERFORMANCE HARD DRIVES The DriveStation Ultra comes equipped with two The DriveStation Ultra features 10 helium-lled enterprise Thunderbolt 2 connectors, allowing Mac users to experience hard drives for the 80 TB model, and 6 or 10 NAS hard drives write speeds up to 1243 MB/s using RAID 0. With the fastest for the 12 TB, 24 TB & 40 TB models. These high performance connection available, it’s an ideal solution for transferring hard drives are optimized for continuous 24/7/365 operation and storing large les such as 4k high resolution videos. -

Designware IP for Cloud Computing Socs

DesignWare IP for Cloud Computing SoCs Overview Hyperscale cloud data centers continue to evolve due to tremendous Internet traffic growth from online collaboration, smartphones and other IoT devices, video streaming, augmented and virtual reality (AR/VR) applications, and connected AI devices. This is driving the need for new architectures for compute, storage, and networking such as AI accelerators, Software Defined Networks (SDNs), communications network processors, and solid state drives (SSDs) to improve cloud data center efficiency and performance. Re-architecting the cloud data center for these latest applications is driving the next generation of semiconductor SoCs to support new high-speed protocols to optimize data processing, networking, and storage in the cloud. Designers building system-on-chips (SoCs) for cloud and high performance computing (HPC) applications need a combination of high-performance and low-latency IP solutions to help deliver total system throughput. Synopsys provides a comprehensive portfolio of high-quality, silicon-proven IP that enables designers to develop SoCs for high-end cloud computing, including AI accelerators, edge computing, visual computing, compute/application servers, networking, and storage applications. Synopsys’ DesignWare® Foundation IP, Interface IP, Security IP, and Processor IP are optimized for high performance, low latency, and low power, while supporting advanced process technologies from 16-nm to 5-nm FinFET and future process nodes. High-Performance Computing Today’s high-performance computing (HPC) solutions provide detailed insights into the world around us and improve our quality of life. HPC solutions deliver the data processing power for massive workloads required for genome sequencing, weather modeling, video rendering, engineering modeling and simulation, medical research, big data analytics, and many other applications. -

HP Z440, Z640, and Z840 Workstation Series Maintenance and Service Guide

HP Z440, Z640, and Z840 Workstation Series Maintenance and Service Guide Copyright Information Warranty Trademark Credits © Copyright 2014, 2016 HP Development The information contained herein is subject to Microsoft and Windows are U.S. registered Company, L.P. change without notice. The only warranties for trademarks of the Microsoft group of HP products and services are set forth in the companies. Third Edition: November 2016 express warranty statements accompanying such products and services. Nothing herein Intel, Intel Xeon, and Thunderbolt are First Edition: October 2014 should be construed as constituting an trademarks of Intel Corporation in the U.S. and other countries. Part Number: 748721-004 additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. Bluetooth is a trademark owned by its proprietor and used by Hewlett-Packard Windows 8: Not all features are available in all Company under license. editions of Windows 8. This workstation may require upgraded and/or separately purchased ENERGY STAR is a registered trademark owned hardware, drivers, and/or software to take full by the U.S. Environmental Protection Agency advantage of Windows 8 functionality. Go to (EPA). http://www.microsoft.com for details. Red Hat is a registered trademark of Red Hat, Windows 7: This workstation may require Inc. in the United States and other countries. upgraded and/or separately purchased hardware and/or a DVD drive to install the Windows 7 software and take full advantage of Windows 7 functionality. Go to http://www.microsoft.com for details. About this guide This guide provides service and maintenance information, technical details and configuration guidance for the HP Z440, Z640, and Z840 Workstations. -

Apogee Ensemble Thunderbolt Audio Interface

Apogee Ensemble Thunderbolt Audio Interface User’s Guide Fall 2014 Contents Overview!...........................................................................................................5 Introduction!................................................................................................................5 Features!.......................................................................................................................5 Package Contents!......................................................................................................6 Ensemble Thunderbolt Panel Tour!...........................................................................7 Front Panel!.................................................................................................................7 Rear Panel!..................................................................................................................8 Display!........................................................................................................................9 Input Settings Display Screen!..................................................................................9 Getting Started!...............................................................................................10 Precautions when powering Ensemble On/Off!......................................................10 Thunderbolt Notes!....................................................................................................10 Ensemble Software!..................................................................................................11 -

TAKING OCP to the NEXT LEVEL – WORKLOAD OPTIMIZATION Krishna Paul Principal Engineer Data Center Group

TAKING OCP TO THE NEXT LEVEL – WORKLOAD OPTIMIZATION Krishna Paul Principal Engineer Data Center Group Consume. Collaborate. Collaborate. Contribute. Contribute. OPEN COMPUTE HISTORY OF COMMITMENT AND LEADERSHIP 2011 +25 +80 Founding Contributions and Products Board Member Enablements with Partners of OCP Consume. Collaborate. Collaborate. Contribute. Contribute. GETTING TO $10B IN OCP DEPLOYMENT Workload Open Management Integrated Optimized Solutions Consume. Collaborate. Collaborate. Contribute. Contribute. NEW OCP COMPUTE PLATFORMS THIS YEAR Mount Olympus Next Gen Platform Cooper Lake Processor Platforms for Cascade Lake Processor 2S 4S (2x 2S) 8S (4x 2S) Consume. Collaborate. Collaborate. Contribute. Contribute. *Other names and brands may be claimed as property of others. INTEL® HIGH-DENSITY, CLOUD-OPTIMIZED PLATFORM Cloud-Optimized Platform 2U 450mm x 780mm 4S Intel® Xeon® Scalable processors 48 DDR4 memory slots, SATA/SAS/NVMe 2.5” SSD drive bays Available in second half 2019 *Other names and brands may be claimed as property of others. Consume. Collaborate. Collaborate. Contribute. Contribute. OCP CARDS SUPPORT NEW AI ACCELERATORS INTEL® NERVANA™ NEURAL NETWORK PROCESSOR (NNP) FOR TRAINING: FOR INFERENCE: Nervana™ Dedicated deep learning training acceleration Dedicated deep learning inference acceleration Optimized memory and interconnects 10nm Intel® process node In production in 2019 In production in 2019 Intel is a proud partner of the community Consume. Collaborate. Collaborate. Contribute. Contribute. *Other names and brands may be claimed as property of others. ANNOUNCING A NEW CPU-TO-DEVICE INTERCONNECT STANDARD COMPUTE EXPRESS LINK (CXL) ▪ New CXL specification and consortium ▪ Memory coherent, high-speed interconnect ▪ Initial spec donated by Intel ▪ Intel® believes there is an opportunity for an OCP working group to define new form factors for CXL ▪ Optimized stack with x16 PCI Express Gen 5 physical and electrical connection (32 GT/s) ▪ Use cases include AI, networking, media, graphics and more ▪ Availability expected 2021 Consume. -

Lacie D2 Thunderbolt 3 USB-C User Manual

LaCie d2 Thunderbolt 3 USB-C User Manual Model: Click here to access an up-to-date online version of this document. You will also find the most recent content as well as expandable illustrations, easier navigation, and search capability. Contents 1 .R .e .g .u . l.a .t o. r. y. .C . o. m. p. l.i a. n. c. e. .4 . .F .C .C . .D . e. c.l a. r. a. t.i o. .n . o. f. .C .o . n. f.o . r.m . .a .n .c .e . 4. .F .C .C . .C . l.a .s s. .A . .I n. f.o . r.m . .a .t i.o . n. 4. .F .C .C . .C . a. u. t.i o. .n . 4. .I m. .p . o. r. t.a .n .t . N. .o .t e. :. F. C. .C . R. .a .d .i a. t.i o. n. E. x. p. o. .s u. .r e. .S .t .a .t e. m. .e .n .t . 4. .I n. d. u. s. t.r .y . C. .a .n .a .d .a . .5 . .I m. .p . o. r. t.a .n .t . N. .o .t e. .f o. .r .m . .o .b . i.l e. d. e. v. i.c .e .u . s.e . .5 . .N . o. t.e . I.m . .p .o .r .t a. n. .t e. .p .o .u . r. l.' u. .t i.l i.s .a .t i.o .n . .d .e .d .i s. p. o. .s i.t .i f.s . m. .o . b. i.l e. -

Dual 4K 60Hz Monitor Thunderbolt™ 3 Dock - Pcie M.2 Slot and SD Reader

Dual 4K 60Hz Monitor Thunderbolt™ 3 Dock - PCIe M.2 Slot and SD Reader Product ID: TB3DK2DPM2 This compact Thunderbolt™ 3 dock is built for productivity, transforming your Thunderbolt 3 MacBook Pro or Windows® laptop into a dual-4K workstation with up to 40Gbps of throughput. The high- performance dock features a PCIe M.2 SSD slot for enhanced data storage, three USB ports, an SD card reader, a Gigabit Ethernet port, a downstream Thunderbolt 3 port for daisy-chaining, plus 85W Power Delivery. Create a Dual-4K 60Hz Workstation Great for Ultra HD tasks, the dual-4K docking station supports 4K resolution on two monitors: • 1x DisplayPort and 1x Thunderbolt 3 USB-C display (4096 x 2160p @60Hz) (USB-C to DP cable or USB-C video adapter may be required) Connect to a single 5K monitor at 60Hz. www.startech.com 1 800 265 1844 Add Data Storage The Thunderbolt 3 dock’s built-in PCIe M.2 SSD enclosure supports transfer speeds up to 1500MB/s with the addition of a PCIe M.2 SSD for ultra-fast data access, enhanced storage, and application buffering and caching. Fast SD Card Access Transfer photos or videos from your SD cards to your Thunderbolt 3 laptop. The dock’s SD slot supports SD 4.0 and UHS-II with transfer speeds up to 270MB/s. Connect Your Devices Connect peripherals with three USB ports - one USB-C port (10G) with up to 3A charging and two USB-A ports (5G) with Fast-Charge and Sync. The GbE port (with PXE Boot and WoL support) provides reliable wired network access. -

USB4™ Thunderbolt3™ Compatibility Requirements Specification

USB4™ Thunderbolt3™ Compatibility Requirements Specification Version 1.0 January 2021 Copyright © 2021 USB Implementers Forum, Inc. All rights reserved. Version 1.0 - ii - USB4™ Thunderbolt3™ Compatibility January 2021 Requirements Specification Release History Ver s io n Co mments I s s ue Dat e 1 .0 First release Jan u ary 2021 Copyright © 2021 USB Implementers Forum, Inc. All rights reserved. Version 1.0 - iii - USB4™ Thunderbolt3™ Compatibility January 2021 Requirements Specification Copyright © 2021, USB Implementers Forum, Inc. All rights reserved THIS SPECIFICATION IS PROVIDED TO YOU “AS IS” WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS. USB Type-C™, USB-C™ and USB4™ are trademarks of the Universal Serial Bus Implementers Forum (USB-IF). Thunderbolt™ is a trademark of Intel Corporation. All product names are trademarks, registered trademarks, or service marks of their respective owners. Copyright © 2021 USB Implementers Forum, Inc. All rights reserved. Version 1.0 - iv - USB4™ Thunderbolt3™ Compatibility January 2021 Requirements Specification Acknowledgement of Technical Contribution A pple I nc. Christine Krause Intel Corporation Ziv Kab iry Shlomi Abekasis Shay Sudman Zohar Shauly Oren Salomon Kopzon Vladislav Reuven Rozic Abdul (Rahman) Ismail Aruni P Nelson Gal Yedidia Benjamin Hacker Brad Saunders Copyright © 2021 USB Implementers Forum, Inc.