SECTION 1 INTRODUCTION and DESCRIPTION Dectape Provides the Flexibility, Speed, and Storage Capabilities of Magnetic Tape Wh'ile

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pdp11-40.Pdf

processor handbook digital equipment corporation Copyright© 1972, by Digital Equipment Corporation DEC, PDP, UNIBUS are registered trademarks of Digital Equipment Corporation. ii TABLE OF CONTENTS CHAPTER 1 INTRODUCTION 1·1 1.1 GENERAL ............................................. 1·1 1.2 GENERAL CHARACTERISTICS . 1·2 1.2.1 The UNIBUS ..... 1·2 1.2.2 Central Processor 1·3 1.2.3 Memories ........... 1·5 1.2.4 Floating Point ... 1·5 1.2.5 Memory Management .............................. .. 1·5 1.3 PERIPHERALS/OPTIONS ......................................... 1·5 1.3.1 1/0 Devices .......... .................................. 1·6 1.3.2 Storage Devices ...................................... .. 1·6 1.3.3 Bus Options .............................................. 1·6 1.4 SOFTWARE ..... .... ........................................... ............. 1·6 1.4.1 Paper Tape Software .......................................... 1·7 1.4.2 Disk Operating System Software ........................ 1·7 1.4.3 Higher Level Languages ................................... .. 1·7 1.5 NUMBER SYSTEMS ..................................... 1-7 CHAPTER 2 SYSTEM ARCHITECTURE. 2-1 2.1 SYSTEM DEFINITION .............. 2·1 2.2 UNIBUS ......................................... 2-1 2.2.1 Bidirectional Lines ...... 2-1 2.2.2 Master-Slave Relation .. 2-2 2.2.3 Interlocked Communication 2-2 2.3 CENTRAL PROCESSOR .......... 2-2 2.3.1 General Registers ... 2-3 2.3.2 Processor Status Word ....... 2-4 2.3.3 Stack Limit Register 2-5 2.4 EXTENDED INSTRUCTION SET & FLOATING POINT .. 2-5 2.5 CORE MEMORY . .... 2-6 2.6 AUTOMATIC PRIORITY INTERRUPTS .... 2-7 2.6.1 Using the Interrupts . 2-9 2.6.2 Interrupt Procedure 2-9 2.6.3 Interrupt Servicing ............ .. 2-10 2.7 PROCESSOR TRAPS ............ 2-10 2.7.1 Power Failure .............. -

PDP-8 Simulator Manual

PDP-8 Simulator Usage 30-Apr-2020 COPYRIGHT NOTICE The following copyright notice applies to the SIMH source, binary, and documentation: Original code published in 1993-2016, written by Robert M Supnik Copyright (c) 1993-2016, Robert M Supnik Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions: The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software. THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL ROBERT M SUPNIK BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. Except as contained in this notice, the name of Robert M Supnik shall not be used in advertising or otherwise to promote the sale, use or other dealings in this Software without prior written authorization from Robert M Supnik. 1 Simulator Files.............................................................................................................................3 -

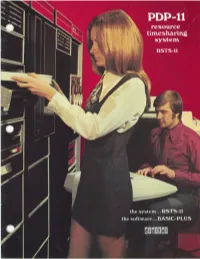

Dec Pdp-11, 1970

resource sharing: timesharing use of high-speed input/outp RSTSll terminal users may have Examples of the value of the Resource another terminal exclusive use of any peripheral 09 a Sharing concept are: one user may use the punched-card file whi8 timesharing system (except the disk, line printer, card reader, tape and BASIC program he ha% which is a shared device). They may use disk files for performing a "batch" off-line card punch. - it as long as needed, and then return it adrmnistrative data processing task; for assignment to another user. The another terminal user may use a ability to enter, store, and retrieve DECtape unit for retrieving or creating a programs and data files using high-speed tape file intended for off-line storage; peripheral devices makes RSTS-11 a true and when thecard reader is free, yet general-purpose problem-solving system. RSTS for business and administrative problem solving One of the most difficult problems facing Potential On-Line Administrative business today is increasing the Applications include: productivity of costly, hard-to-find clerks and secretaries. RSTS-11's power and Order Entry/Accounts Receivable/ flexibility offer the benefits of reduced Sales Analysis costs, increased customer satisfaction, Inventory Control/Accounts Payable and increased job satisfaction for clerical Data Entry with automatic error workers. checking, editing, and verification Inquiry-Response for "instant" access How RSTSll Benefits Administrative to records. Applications Journals, general ledger, and other account records are stored on-line for RSTSll can be dedicated in quick access from high-speed disk administrative application systems. The storage, thus reducing paper handling. -

A New Architecture for Mini-Computers -- the DEC PDP-11

Reprinted from - AFIPS - Conference Proceedings, Volume 36 Copyright @ by AFlPS Press Montvale, New Jersey 07645 A new architecture for mini-computers- The DEC PDP-11 by G. BELL,* R. CADY, H. McFARLAND, B. DELAGI, J. O’LAUGHLINandR. NOONAN l?i&l Equipment Corporation Maynard, Massachusetts and W. WULF Carnegit+Mellon University Pittsburgh, Fcriiisylvnnia INTRODUCTION tion is not surprising since the basic architectural concepts for current mini-computers were formed in The mini-computer** has a wide variety of uses: com- the early 1960’s. First, the design was constrained by munications controller; instrument controller; large- cost, resulting in rather simple processor logic and system pre-processor ; real-time data acquisition register configurations. Second, application experience systems . .; desk calculator. Historically, Digital was not available. For example, the early constraints Equipment Corporation’s PDP-8 Family, with 6,000 often created computing designs with what we now installations has been the archetype of these mini- consider weaknesses : computers. In some applications current mini-computers have 1. limited addressing capability, particularly of limitations. These limitations show up when the scope larger core sizes of their initial task is increased (e.g., using a higher 2. few registers, general registers, accumulators, level language, or processing more variables). Increasing index registers, base registers the scope of the task generally requires the use of 3. no hardware stack facilities more comprehensive executives and system control 4. limited priority interrupt structures, and thus programs, hence larger memories and more processing. slow context switching among multiple programs This larger system tends to be at the limit of current (tasks) mini-computer capability, thus the user receives 5. -

The DEC PDP-8 Vectors

The ISP of the PDP-8 Pc is about the most trivial in the book. Chapter 5 — It has only a few data operators, namely, <—,+, (negate), -j, It on A, / 2, X 2, (optional) X, /, and normalize. operates words, The DEC PDP-8 vectors. there are microcoded integers, and boolean However, instructions, which allow compound instructions to be formed in Introduction 1 a single instruction. is the levels dis- The PDP-8 is a single-address, 12-bit-word computer of the second The computer straightforward and illustrates 1. look at it from the down." generation. It is designed for task environments with minimum cussed in Chap. We can easily "top arithmetic computing and small Mp requirements. For example, The C in PMS notation is it can be used to control laboratory devices, such as gas chromoto- 12 graphs or sampling oscilloscopes. Together with special T's, it is C('PDP-8; technology:transistors; b/w; programmed to be a laboratory instrument, such as a pulse height descendants:'PDP-8/S, 'PDP-8/I, 'PDP-8/L; antecedents: 'PDP-5; analyzer or a spectrum analyzer. These applications are typical Mp(core; #0:7; 4096 w; tc:1.5 /is/w); of the laboratory and process control requirements for which the ~ 4 it Pc(Mps(2 w); machine was designed. As another example, can serve as a instruction length:l|2 w message concentrator by controlling telephone lines to which : 1 address/instruction ; occasion- typewriters and Teletypes are attached. The computer operations on data/od:(<— , +, —\, A, —(negate), X 2, stands alone as a small-scale general-purpose computer. -

The Computer History Simulation Project

The Computer History Simulation Project The Computer History Simulation Project The Computer History Simulation Project is a loose Internet-based collective of people interested in restoring historically significant computer hardware and software systems by simulation. The goal of the project is to create highly portable system simulators and to publish them as freeware on the Internet, with freely available copies of significant or representative software. Simulators SIMH is a highly portable, multi-system simulator. ● Download the latest sources for SIMH (V3.5-1 updated 15-Oct-2005 - see change log). ● Download a zip file containing Windows executables for all the SIMH simulators. The VAX and PDP-11 are compiled without Ethernet support. Versions with Ethernet support are available here. If you download the executables, you should download the source archive as well, as it contains the documentation and other supporting files. ● If your host system is Alpha/VMS, and you want Ethernet support, you need to download the VMS Pcap library and execlet here. SIMH implements simulators for: ● Data General Nova, Eclipse ● Digital Equipment Corporation PDP-1, PDP-4, PDP-7, PDP-8, PDP-9, PDP-10, PDP-11, PDP- 15, VAX ● GRI Corporation GRI-909 ● IBM 1401, 1620, 1130, System 3 ● Interdata (Perkin-Elmer) 16b and 32b systems ● Hewlett-Packard 2116, 2100, 21MX ● Honeywell H316/H516 ● MITS Altair 8800, with both 8080 and Z80 ● Royal-Mcbee LGP-30, LGP-21 ● Scientific Data Systems SDS 940 Also available is a collection of tools for manipulating simulator file formats and for cross- assembling code for the PDP-1, PDP-7, PDP-8, and PDP-11. -

System Generation Notes

08/8 System Generation Notes Order No. AA-H606A-TA 08/8 System Generation Notes Order No. AA-H606A-TA March 1979 ABSTRACT This document describes the procedures for getting on line with 05/8. SUPERSESSION/UPDATE INFORMATION: This manual supersedes and updates information in the 05/8 Handbook (DEC-S8-0SHBA-A-D) and the 05/8 Handbook Update (DEC·S8·0SHBA·A·DN4). OPERATING SYSTEM AND VERSION: 05/8 V3D. To order additional copies of this document, contact the Software Distribution Center, Digital Equipment Corporation, Maynard, Massachusetts 01754 digital equipment corporation • maynard. massachusetts First Printing, March 1979 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software on equipment that is not supplied by DIGITAL or its affiliated companies. Copyright © 1979 by Digital Equipment Corporation The postage-prepaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist us in pre paring future documentation. The following are trademarks of Digital Equipment Corporation: DIGITAL DECsystem-10 MASSBUS DEC DEC tape OMNIBUS POP DIBOL OS/8 DECUS EDUSYSTEM PHA UNIBUS FLIP CHIP RSTS COMPUTER -

Timeline of Computer History

Timeline of Computer History By Year By Category Search AI & Robotics (55) Computers (145) Graphics & Games (48) Memory & Storage (61)(61) Networking & The Popular Culture (50) Software & Languages (60) Manchester Mark I Williams- 1947 Kilburn tube EDSAC 1949 Manchester Mark I Williams-Kilburn tube At Manchester University, Freddie Williams and Tom Kilburn develop the Williams-Kilburn tube. The tube, tested in 1947, was the first high-speed, entirely electronic memory. It used a cathode ray tube (similar to an analog TV picture tube) to store bits as dots on the screen’s surface. Each dot lasted a fraction of a second before fading so the information was constantly refreshed. Information was read by a metal pickup plate that would detect a change in electrical charge. Maurice Wilkes with EDSAC Maurice Wilkes and his team at the University of Cambrid construct the Electronic Delay Storage Automatic Calcula (EDSAC). EDSAC, a stored program computer, used me delay line memory. Wilkes had attended the University of Pennsylvania's Moore School of Engineering summer sessions about the ENIAC in 1946 and shortly thereafter Magnetic drum memory began work on the EDSAC. 1950 MIT - Magnetic core memory ERA founders with various magnetic drum memories Eager to enhance America’s codebreaking capabilities, the US Navy contracts with Engineering Research Associates (ERA) for a stored program computer. The result was Atlas, completed in 1950. Atlas used magnetic drum memory, which stored information on the outside of a rotating cylinder coated with ferromagnetic material and circled by read/write heads in Jay Forrester holding early core memory plane fixed positions. -

TU58 Dectape II User's Guide

EK-OTU58-UG-001 TU58 DECtape II User's Guide digital equipment corporation • maynard, massachusetts 1st Editi on, October 1978 The drawings and specifications herein are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of equipment described herein without written permission. Copyright © 1978 by Digital Equipment Corporation The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no re sponsibility for any errors which may appear in this man ual. Printed in U.S.A. This document was set on DIGITAL's DECset-SOOO computerized typesetting system. The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts: DIGITAL DECsystem-lO MASSBUS DEC DECSYSTEM-20 OMNIBUS PDP DIBOL OS/8 DECUS EDUSYSTEM RSTS UNIBUS VAX RSX VMS lAS CONTENTS CHAPTER 1 INTRODUCTION l.1 SCOPE ................................................................................................................ 1-1 l.2 GENERAL DESCRIPTION ............................................................................... 1-1 l.3 BLOCK DIAGRAM ........................................................................................... 1-3 l.3.1 Drive Control ............................................................................................... 1-4 1.3.2 Processor ...................................................................................................... 1-4 1.4 -

Ah-T545b-Mc Lcp5 Lcp-5 Cpu Clustr Dia Cjkl5b0 (C)1983-85

Bl A f:CJKL580 lCP-5 CPU CL»TR OIAG mCYll 50(1046 ) 0' JMl-85 09:28 PAtt ^ CJKLSe.Pll 07 jAN-85 »:05 '>E0 0001 5706 .HEM 5709 5710 5711 5712 5715 5714 5715 5716 5717 57l« 5719 5720 5721 5722 5725 5724 5725 5726 5727 5728 5729 IDENTIFICATION 5750 5751 5752 5755 5754 PRODUCT CODE: AC-T544B-nC 5755 5756 PRODUCT NAME: CJKL5B0 LCP-5 CPU aSTR DIAG 5757 5758 PRODUCT DATE: JANUARY 85 5759 5740 NAINTAZNER: OIAGNDSTIC ENGINEERING 5741 5742 5743 5/44 574 > THE nrORHATION IN THIS DOCUTCNT IS SUBJECT TO CHANGE WITHOUT NOTICE 574fc AND SHOULD NOT BE CONSTRUED AS A COftUTHENT BY DIGITAL CORPORATION. 574 7 DIGITAL EQUIPMENT CORPORATION ASSUMES NO RESPONSIBILITY FOR ANY ERRORS 5748 THAT HAY APPEAR IN THIS DOCUTCNT. b750 NO RESPONSIBILITY IS ASSUNEO FOR TtC USE OR RELIMILITY OF SOFTWARE ON S751 EOUIPNENT THAT IS NOT SUPPLIED BY DIGITAL OR ITS AFFILIATED COMPANIES. 57S2 57^3 COPYRIGHT (C): 1965.1985 BY DIGITAL EQUIPMENT CORPORATION 5754 5755 THE FOLLOWING ARE TRADEMARKS OF DIGITAL EQUIPMENT CORPORATION: 5756 5757 DIGITAL POP UNIBUS MASSBUS 5758 DEC DECUS DECTAPE OEC/Xll 5759 5760 5761 5762 5765 Ci CJKLSeO LCP 5 CPU CLSTR OIAG MACni 50(1046) 07 JAN 65 09:26 PAGE 2 1 CJKc58 Pll 07 JAN-BS 09:0S SEO OOO^ 5764 MISTORt 5765 5766 5767 5768 REVISION A FIRST RELEASE OF DIAGNOSTIC 5769 5770 REVISION B THIS REVISION WAS MADE TO CORRECT PROBLEMS 5771 ENCOUNTERED UHILE RUNNING UNDER APT nOOF 5772 FOR CHANGES. SEE i 00001 5773 5774 ni CJKcSeO lCP 5 CK' CLSTR OIAG riACril 30(1046 ) 07 JAN 85 09:28 PAGt ^ CJKLSe.Pll 07 jAN-eS 09:0S yLQ 0003 5776 5777 5778 TABLE or CONTENTS -

Guide to the Collection of Digital Equipment Corporation PDP-1 Computer Materials

Guide to the Collection of Digital Equipment Corporation PDP-1 Computer Materials Dates: 1960 – 1983 (bulk 1960 - 1976) Extent: 9 linear feet Collection number: X3602.2006 Accession number: 102660913 Processed by: Judith A. Strebel and Rebekah Kim, 2006 Collection of Digital Equipment Corporation PDP-1 Computer Materials X3602.2006 Abstract The Collection of Digital Equipment Corporation (DEC) PDP-1 Computer Materials is comprised of program listings, manuals, technical papers, promotional materials, design drawings and photographs regarding the PDP-1 digital computer spanning 1959 to 1983. Administrative Information Access Restrictions The collection is open for research. Publication Rights The Computer History Museum (CHM) can only claim physical ownership of the collection. Users are responsible for satisfying any claims of the copyright holder. Permission to copy or publish any portion of the Computer History Museum’s collection must be given by the Computer History Museum. Preferred Citation [Identification of Item], [Item Date], Collection of Digital Equipment Corporation PDP-1 Computer Materials, Lot X3602.2006, [Box #], [Folder #], Computer History Museum Processing Notes The processing of the Collection of DEC PDP-1 Computer Material was undertaken as a result of the restoration of a PDP-1 computer at the Computer History Museum and the subsequent online exhibit. The collection had partial archival processing at CHM before its full processing by Judy Strebel and Rebekah Kim during 2005 and 2006. No original order existed from the previous processing or from its acquisition by CHM. Provenance Notes The provenance is unknown for the Collection of DEC PDP-1 Computer Materials and most likely came from a variety of different sources. -

PROGRAM LIBRARY PDP-Ll CATALOG CATALOG

~ PROGRAM LIBRARY PDP-ll CATALOG CATALOG OICiITAl EQUIPMENT COMPUTER USERS SOCIETY AUGUST 1978 DECUS PROGRAM LIBRARY PDP-11 CATALOG Cl DICiITAL EQUIPMENT COMPUTER USERS SOCIETY AUGUST 1978 This is a complete PDP-ll DECUS Library CATALOG. It includes a complete listing of PDP-II and RSTSjE DECUS programs. First Edition February 1974 Updated August 1974 Updated February 1975 Updated July 1975 Updated October 1975 Updated July 1976 Combined and Reprinted September 1976 Combined, ltpdated, and revised September 1977 Updated and revised August 1978 Copyright @ 1978, Digital Equipment Corporation Maynard, Massachusetts The DECUS Program Library is a clearing house only; it does not sell, generate or test programs. All programs and information are provided "AS IS". DIGITAL EQUIP MENT COMPUTER USERS SOCIETY, DIGITAL EQUIPMENT CORPORATION AND THE CONTRIBUTOR DISCLAIM ALL WARRANTIES ON THE PRO GRAMS AND ANY MEDIA ON WHICH THE PROGRAMS ARE PROVIDED, INCLUDING WITHOUT LIMITATION, ALL IMPLIED WARRANTIES OF MERCHANTABILI1Y AND FITNESS. The descriptions, service charges, exchange rates, and availability of software available from the DECUS Library are subject to change without notice. The following are trademarks of Digital Equipment Corporation: COMPUTER LABS DECtape INDAC RSTS COMTEX DECUS LAB-8 RSX DDT DIBOl MASSBUS TYPESET-8 DEC DIGITAL OMNIBUS TYPESET-11 DECCOMM EDUSYSTEM 0S-8 UNIBUS DECsystem-10 FLIP CHIP PDP DECSYSTEM-20 FOCAL PHA Contents Section 1 General Information 1.1 How to Use this Catalog ................................................................. v 1.1.1 General Catalog Information ................................................. v 1.2 DECUS Contacts .......................................................................... v 1.2.1 United States and Canada .................................................... v 1.2.2 Outside the United States and Canada ..................................... vi 1.3 Payment ....................................................................................