Carry Look Ahead Addition

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Disability Classification System

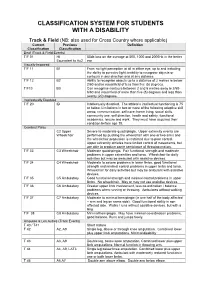

CLASSIFICATION SYSTEM FOR STUDENTS WITH A DISABILITY Track & Field (NB: also used for Cross Country where applicable) Current Previous Definition Classification Classification Deaf (Track & Field Events) T/F 01 HI 55db loss on the average at 500, 1000 and 2000Hz in the better Equivalent to Au2 ear Visually Impaired T/F 11 B1 From no light perception at all in either eye, up to and including the ability to perceive light; inability to recognise objects or contours in any direction and at any distance. T/F 12 B2 Ability to recognise objects up to a distance of 2 metres ie below 2/60 and/or visual field of less than five (5) degrees. T/F13 B3 Can recognise contours between 2 and 6 metres away ie 2/60- 6/60 and visual field of more than five (5) degrees and less than twenty (20) degrees. Intellectually Disabled T/F 20 ID Intellectually disabled. The athlete’s intellectual functioning is 75 or below. Limitations in two or more of the following adaptive skill areas; communication, self-care; home living, social skills, community use, self direction, health and safety, functional academics, leisure and work. They must have acquired their condition before age 18. Cerebral Palsy C2 Upper Severe to moderate quadriplegia. Upper extremity events are Wheelchair performed by pushing the wheelchair with one or two arms and the wheelchair propulsion is restricted due to poor control. Upper extremity athletes have limited control of movements, but are able to produce some semblance of throwing motion. T/F 33 C3 Wheelchair Moderate quadriplegia. Fair functional strength and moderate problems in upper extremities and torso. -

Ifds Functional Classification System & Procedures

IFDS FUNCTIONAL CLASSIFICATION SYSTEM & PROCEDURES MANUAL 2009 - 2012 Effective – 1 January 2009 Originally Published – March 2009 IFDS, C/o ISAF UK Ltd, Ariadne House, Town Quay, Southampton, Hampshire, SO14 2AQ, GREAT BRITAIN Tel. +44 2380 635111 Fax. +44 2380 635789 Email: [email protected] Web: www.sailing.org/disabled 1 Contents Page Introduction 5 Part A – Functional Classification System Rules for Sailors A1 General Overview and Sailor Evaluation 6 A1.1 Purpose 6 A1.2 Sailing Functions 6 A1.3 Ranking of Functional Limitations 6 A1.4 Eligibility for Competition 6 A1.5 Minimum Disability 7 A2 IFDS Class and Status 8 A2.1 Class 8 A2.2 Class Status 8 A2.3 Master List 10 A3 Classification Procedure 10 A3.0 Classification Administration Fee 10 A3.1 Personal Assistive Devices 10 A3.2 Medical Documentation 11 A3.3 Sailors’ Responsibility for Classification Evaluation 11 A3.4 Sailor Presentation for Classification Evaluation 12 A3.5 Method of Assessment 12 A3.6 Deciding the Class 14 A4 Failure to attend/Non Co-operation/Misrepresentation 16 A4.1 Sailor Failure to Attend Evaluation 16 A4.2 Non Co-operation during Evaluation 16 A4.3 International Misrepresentation of Skills and/or Abilities 17 A4.4 Consequences for Sailor Support Personnel 18 A4.5 Consequences for Teams 18 A5 Specific Rules for Boat Classes 18 A5.1 Paralympic Boat Classes 18 A5.2 Non-Paralympic Boat Classes 19 Part B – Protest and Appeals B1 Protest 20 B1.1 General Principles 20 B1.2 Class Status and Protest Opportunities 21 B1.3 Parties who may submit a Classification Protest -

Presenting the Paralympics: Affective Nationalism and the 'Able-Disabled'

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Bournemouth University Research Online (Re-)presenting the Paralympics: Affective Nationalism and the 'able-disabled' Emma Pullen, Daniel Jackson and Michael Silk Communication & Sport (2019, in press) *To cite this article: Pullen, E., Jackson, D., and Silk, M. (2019). (Re-)presenting the Paralympics: Affective Nationalism and the 'able-disabled'. Communication & Sport Corresponding author: [email protected] Abstract The relationship between media, sport, nations and nationalism is well established, yet, there is an absence of these discussions at the intersection of communication, Paralympics and disability studies. This omission is particularly significant considering the rapid commodification of the Paralympic spectacle, exacerbated by the entry of Channel 4 (C4) as the UK Paralympic rights holders, that has seen the games become an important site of disability (re-)presentation. In this article, we focus on the construction of national, normative, disabled bodies in Paralympic representation drawn from an analysis of three integrated datasets from Channel 4’s broadcasting of the Rio 2016 Paralympics: interviews with C4 production and editorial staff; quantitative content analysis, and qualitative moving image analysis. We highlight the strategic approach taken by C4 to focus on successful medal winning athletes; the implications this has on the sports and disability classifications given media coverage; and the role of affective high-value production practices. We also reveal the commercial tensions and editorial decisions that broadcasters face with respect to which disabilities / bodies are made hyper-visible - and thereby those which are marginalized - as national disability sport icons that inculcate preferred notions of disability and the (re)imagined nation. -

Grade Conversion Tables for Study Abroad

Grade conversion tables for study abroad NB These tables should only be used to convert grades FROM study abroad TO University of Glasgow grades. They should NOT be used to indicate the equivalence of University of Glasgow Grades to those from other institutions. Translation of Grades Working Group – November 2020 [minor updates – August 2021] Revised March 2019 Minor correction November 2019 Argentina Argentina Glasgow Grade 10 A1 9 A4 8 B1 7 B3 6 C2 5 D1 4 D3 3 E2 2 F2 1 G2 Rationale The table is based on the current partnership with Universidad del Salvador. Subjects with Partners in Argentina: University-wide Australia Australia Glasgow Grade 90-100% A1 85-89 A3 80-84 A5 75-79 B1 70-74 B2 65-69 B3 60-64 C1 55-59 C3 50-54 D2 44-49 E1 39-43 E2 34-38 E3 29-33 F1 24-28 F2 19-23 F3 14-18 G1 9-13 G2 0-8 H 2 University of Queensland Grade Glasgow Grade 7 (High Distinction) A2 6 (Distinction) A4 5 (Credit) B2 4 (Pass) C2 3 (Limited Pass) D2 2 (Fail) E2 1 (Fail) F2 Queensland University of Technology Grade Glasgow Grade 7 (85-100%) A1 6 (80-84%) A4 6 (75-79%) B1 5 (70-74%) B2 5 (65-69%) B3 4 (60-64%) C1 4 (50-59%) C3 3 (47-49%) D2 2 (35-46%) E2 2 (25-34%) F2 1 (0-24%) G1 Rationale The University of Queensland uses a different scale which precludes it from the national table above. -

VMAA-Performance-Sta

Revised June 18, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

The Impact of Lower-Limb Prosthetic Limb Use in International C4 Track Para-Cycling

The impact of lower-limb prosthetic limb use in international C4 track para-cycling An investigation was undertaken to ascertain any impact or significance of athletes within the C4 paracycling classification between those who use a lower- limb prostheses and those who do not. A statistical evaluation of event completion time was undertaken to assess C4 cyclists when competing at the World Championships and the Paralympic Games in the 1km track time trial. The C4 athletes who utilise a prostheses consistently outperformed non-amputees in the C4 classification from 2011-2016 on a competition-to-competition basis. However, when the participations were grouped as a whole together and an identified outlier athlete was removed, it was then demonstrated that there was no statistical significance between those who required the use of a lower-limb prostheses to those that did not when either evaluated on a competition-by- competition or on an amputee and non-amputee group-by-group basis (P=>0.05). As a result, this study proposes that those requiring the use of lower-limb prostheses are neither advantaged nor disadvantaged in the C4 classification category when competing in the 1km time trial at this time. Implications for Rehabilitation • This analysis indicates that at this time, there is no evidence to suggest that use of such technology is advantageous in this category or should be seen as controversial. • The design of lower-limb prosthetic limb technology in cycling should continue to be developed and optimized unabated. • This study begins to address the cited lack of peer reviewed information regarding paracycling with limb absence available to practitioners. -

U.S. Department of Veterans Affairs (VA)

U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent Team USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

The Use of Fire Classification in the Nordic Countries – Proposals

The use of fi re classifi cation in the Nordic countries – Proposals for harmonisation Per Thureson, Björn Sundström, Esko Mikkola, Dan Bluhme, Anne Steen Hansen and Björn Karlsson SP Technical Research Institute of Sweden SP Technical SP Fire Technology SP REPORT 2008:29 The use of fire classification in the Nordic countries - Proposals for harmonisation Per Thureson, Björn Sundström, Esko Mikkola, Dan Bluhme, Anne Steen Hansen and Björn Karlsson 2 Key words: harmonisation, fire classification, construction products, building regulations, reaction to fire, fire resistance SP Sveriges Tekniska SP Technical Research Institute of Forskningsinstitut Sweden SP Rapport 2008:29 SP Report 2008:29 ISBN 978-91-85829-46-0 ISSN 0284-5172 Borås 2008 Postal address: Box 857, SE-501 15 BORÅS, Sweden Telephone: +46 33 16 50 00 Telefax: +46 33 13 55 02 E-mail: [email protected] 3 Contents Contents 3 Preface 5 Summary 6 1 Nordic harmonisation of building regulations – earlier work 9 1.1 NKB 9 2 Building regulations in the Nordic countries 10 2.1 Levels of regulatory tools 10 2.2 Performance-based design and Fire Safety Engineering (FSE) 12 2.2.1 Fire safety and performance-based building codes 12 2.2.2 Verification 13 2.2.3 Fundamental principles of deterministic Fire Safety Engineering 15 2.3 The Construction Products Directive – CPD 16 3 Implementation of the CPD in the Nordic countries – present situation and proposals 18 3.1 Materials 18 3.2 Internal surfaces 22 3.3 External surfaces 24 3.4 Facades 26 3.5 Floorings 28 3.6 Insulation products 30 3.7 Linear -

Cryptanalysis of Boyen's Attribute-Based Encryption Scheme

Cryptanalysis of Boyen’s Attribute-Based Encryption Scheme in TCC 2013 Shweta Agrawal1, Rajarshi Biswas1, Ryo Nishimaki2, Keita Xagawa2, Xiang Xie3, and Shota Yamada4 1 IIT Madras, Chennai, India [email protected], [email protected] 2 NTT Secure Platform Laboratories, Tokyo, Japan [ryo.nishimaki.zk,keita.xagawa.zv]@hco.ntt.co.jp 3 Shanghai Key Laboratory of Privacy-Preserving Computation, China [email protected] 4 National Institute of Advanced Industrial Science and Technology (AIST), Tokyo [email protected] Abstract. In TCC 2013, Boyen suggested the first lattice based con- struction of attribute based encryption (ABE) for the circuit class NC1. Unfortunately, soon after, a flaw was found in the security proof of the scheme. However, it remained unclear whether the scheme is actually insecure, and if so, whether it can be repaired. Meanwhile, the construc- tion has been heavily cited and continues to be extensively studied due to its technical novelty. In particular, this is the first lattice based ABE which uses linear secret sharing schemes (LSSS) as a crucial tool to en- force access control. In this work, we show that the scheme is in fact insecure. To do so, we provide a polynomial-time attack that completely breaks the security of the scheme. We suggest a route to fix the security of the scheme, via the notion of admissible linear secret sharing schemes (LSSS) and instantiate these for the class of DNFs. Subsequent to our work, Datta, Komargodski and Waters (Eurocrypt 2021) provided a construction of admissible LSSS for NC1 and resurrected Boyen’s claimed result. -

United States Olympic Committee and U.S. Department of Veterans Affairs

SELECTION STANDARDS United States Olympic Committee and U.S. Department of Veterans Affairs Veteran Monthly Assistance Allowance Program The U.S. Olympic Committee supports Paralympic-eligible military veterans in their efforts to represent the USA at the Paralympic Games and other international sport competitions. Veterans who demonstrate exceptional sport skills and the commitment necessary to pursue elite-level competition are given guidance on securing the training, support, and coaching needed to qualify for Team USA and achieve their Paralympic dreams. Through a partnership between the United States Department of Veterans Affairs and the USOC, the VA National Veterans Sports Programs & Special Events Office provides a monthly assistance allowance for disabled Veterans of the Armed Forces training in a Paralympic sport, as authorized by 38 U.S.C. § 322(d) and section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program the VA will pay a monthly allowance to a Veteran with a service-connected or non-service-connected disability if the Veteran meets the minimum VA Monthly Assistance Allowance (VMAA) Standard in his/her respective sport and sport class at a recognized competition. Athletes must have established training and competition plans and are responsible for turning in monthly and/or quarterly forms and reports in order to continue receiving the monthly assistance allowance. Additionally, an athlete must be U.S. citizen OR permanent resident to be eligible. Lastly, in order to be eligible for the VMAA athletes must undergo either national or international classification evaluation (and be found Paralympic sport eligible) within six months of being placed on the allowance pay list. -

Use Class A1, A2, A3, A4 and A5 Shops, High

Use Class A1, A2, A3, A4 and A5 Shops, High Street Offices, Restaurants, Drinking Establishments and Takeaways Car Parking Cycle parking Car Parking Car Parking Standards Location Standards Servicing Requirements Threshold levels standards (minimum) Standards (minimum) (other requirements) (maximum) City Centre Primary Staff: One covered and Allocated parking is not Allocated parking Not applicable Servicing may be possible Retail Area secure cycle parking permitted is not permitted from the street for smaller space per 100m2 stores (under 2000m2) but Travel Plan 1,000m2 Customers: Where many areas have (or may Travel Information possible, the provision become) time restricted Plan 200m2 of one cycle space per access and existing off Transport Statement 50m2 within the street servicing should be - 1,000 m2 Primary City Centre retained. Developments over Transport Retail Area will 2000m2 will normally require Assessment- normally be required. off street service bays unlikely to be The TS or TA should capable of handling likely required inform the level of service vehicle generation, provision on larger including provision for developments articulated vehicles. Elsewhere in the City Staff: One covered and Allocated parking is not Allocated parking Car parking will only be Servicing may be permitted Centre Parking Area secure cycle parking permitted is not permitted permitted where this replaces on street where safe and space per 100m2 pro-rata identified public practicable. Otherwise a bay Customers: One cycle parking spaces in the city capable of holding a rigid 2 space per 50m2 centre and is available for use 11m vehicle required. Travel Plan 1,000m 2 Travel Information adjacent to principal by the general public consistent Developments over 1,000m 2 entrances or nearby if with the requirements of Policy will normally require off Plan 200m Transport Statement on highway DM29 street service bays capable 2 The TS or TA should of handling likely service - 1,000 m inform the level of 5% of total. -

A1 A2 A3 A4 A5

GUIDE TO USE CLASSES ORDER IN ENGLAND IN FORCE 6 APRIL 2016 The table below is intended as general guidance only. Reference needs to be made to the Town and Country Planning (Use Classes) Order 1987 (as amended) and The Town and Country Planning (General Permitted Development) Order 2015 (as amended), for limitations (e.g floorspace maxima), restrictions, conditions and details of any requirements for any application for determination as to whether the prior approval of the local planning authority will be required, (which may include the prior approval of building operations). USE CLASS USE PERMITTED CHANGE Shops, retail warehouses, post Permitted change to or from a mixed use as A1 or A2 & up to 2 flats offices, ticket and travel Temporary permitted change (2 years) for up to 150 sqm to A2, A3, B1 (interchangeable agencies, sale of cold food for with notification) consumption off premises, A1 Permitted change of A1 or mixed A1 and dwellinghouse to C3 (subject to prior approval) hairdressers, funeral directors, SHOPS hire shops, dry cleaners, internet Permitted change to A2 cafés Permitted change to A3 (inclusive of buildings and other operations subject to prior approval) Permitted change to D2 (subject to prior approval) Banks, building societies, estate Permitted change to A1 where there is a display window at ground floor level. and employment agencies, Permitted change to or from a mixed use for any purpose within A2 and up to 2 flats and professional services (not health for A1 and up to 2 flats, where there is a display window