Concordia: Distributed Shared Memory with In-Network Cache

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Parallel Computer Architecture

Parallel Computer Architecture Introduction to Parallel Computing CIS 410/510 Department of Computer and Information Science Lecture 2 – Parallel Architecture Outline q Parallel architecture types q Instruction-level parallelism q Vector processing q SIMD q Shared memory ❍ Memory organization: UMA, NUMA ❍ Coherency: CC-UMA, CC-NUMA q Interconnection networks q Distributed memory q Clusters q Clusters of SMPs q Heterogeneous clusters of SMPs Introduction to Parallel Computing, University of Oregon, IPCC Lecture 2 – Parallel Architecture 2 Parallel Architecture Types • Uniprocessor • Shared Memory – Scalar processor Multiprocessor (SMP) processor – Shared memory address space – Bus-based memory system memory processor … processor – Vector processor bus processor vector memory memory – Interconnection network – Single Instruction Multiple processor … processor Data (SIMD) network processor … … memory memory Introduction to Parallel Computing, University of Oregon, IPCC Lecture 2 – Parallel Architecture 3 Parallel Architecture Types (2) • Distributed Memory • Cluster of SMPs Multiprocessor – Shared memory addressing – Message passing within SMP node between nodes – Message passing between SMP memory memory nodes … M M processor processor … … P … P P P interconnec2on network network interface interconnec2on network processor processor … P … P P … P memory memory … M M – Massively Parallel Processor (MPP) – Can also be regarded as MPP if • Many, many processors processor number is large Introduction to Parallel Computing, University of Oregon, -

Reducing Cache Coherence Traffic with a NUMA-Aware Runtime Approach

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPDS.2017.2787123, IEEE Transactions on Parallel and Distributed Systems IEEE TRANSACTIONS ON PARALLEL AND DISTRIBUTED SYSTEMS, VOL. XX, NO. X, MONTH YEAR 1 Reducing Cache Coherence Traffic with a NUMA-Aware Runtime Approach Paul Caheny, Lluc Alvarez, Said Derradji, Mateo Valero, Fellow, IEEE, Miquel Moreto,´ Marc Casas Abstract—Cache Coherent NUMA (ccNUMA) architectures are a widespread paradigm due to the benefits they provide for scaling core count and memory capacity. Also, the flat memory address space they offer considerably improves programmability. However, ccNUMA architectures require sophisticated and expensive cache coherence protocols to enforce correctness during parallel executions, which trigger a significant amount of on- and off-chip traffic in the system. This paper analyses how coherence traffic may be best constrained in a large, real ccNUMA platform comprising 288 cores through the use of a joint hardware/software approach. For several benchmarks, we study coherence traffic in detail under the influence of an added hierarchical cache layer in the directory protocol combined with runtime managed NUMA-aware scheduling and data allocation techniques to make most efficient use of the added hardware. The effectiveness of this joint approach is demonstrated by speedups of 3.14x to 9.97x and coherence traffic reductions of up to 99% in comparison to NUMA-oblivious scheduling and data allocation. Index Terms—Cache Coherence, NUMA, Task-based programming models F 1 INTRODUCTION HE ccNUMA approach to memory system architecture the data is allocated within the NUMA regions of the system T has become a ubiquitous choice in the design-space [10], [28]. -

Thread-Level Parallelism – Part 1

Chapter 5: Thread-Level Parallelism – Part 1 Introduction What is a parallel or multiprocessor system? Why parallel architecture? Performance potential Flynn classification Communication models Architectures Centralized shared-memory Distributed shared-memory Parallel programming Synchronization Memory consistency models What is a parallel or multiprocessor system? Multiple processor units working together to solve the same problem Key architectural issue: Communication model Why parallel architectures? Absolute performance Technology and architecture trends Dennard scaling, ILP wall, Moore’s law Multicore chips Connect multicore together for even more parallelism Performance Potential Amdahl's Law is pessimistic Let s be the serial part Let p be the part that can be parallelized n ways Serial: SSPPPPPP 6 processors: SSP P P P P P Speedup = 8/3 = 2.67 1 T(n) = s+p/n As n → , T(n) → 1 s Pessimistic Performance Potential (Cont.) Gustafson's Corollary Amdahl's law holds if run same problem size on larger machines But in practice, we run larger problems and ''wait'' the same time Performance Potential (Cont.) Gustafson's Corollary (Cont.) Assume for larger problem sizes Serial time fixed (at s) Parallel time proportional to problem size (truth more complicated) Old Serial: SSPPPPPP 6 processors: SSPPPPPP PPPPPP PPPPPP PPPPPP PPPPPP PPPPPP Hypothetical Serial: SSPPPPPP PPPPPP PPPPPP PPPPPP PPPPPP PPPPPP Speedup = (8+5*6)/8 = 4.75 T'(n) = s + n*p; T'() → !!!! How does your algorithm ''scale up''? Flynn classification Single-Instruction Single-Data -

Efficient Synchronization Mechanisms for Scalable GPU Architectures

Efficient Synchronization Mechanisms for Scalable GPU Architectures by Xiaowei Ren M.Sc., Xi’an Jiaotong University, 2015 B.Sc., Xi’an Jiaotong University, 2012 a thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the faculty of graduate and postdoctoral studies (Electrical and Computer Engineering) The University of British Columbia (Vancouver) October 2020 © Xiaowei Ren, 2020 The following individuals certify that they have read, and recommend to the Faculty of Graduate and Postdoctoral Studies for acceptance, the dissertation entitled: Efficient Synchronization Mechanisms for Scalable GPU Architectures submitted by Xiaowei Ren in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering. Examining Committee: Mieszko Lis, Electrical and Computer Engineering Supervisor Steve Wilton, Electrical and Computer Engineering Supervisory Committee Member Konrad Walus, Electrical and Computer Engineering University Examiner Ivan Beschastnikh, Computer Science University Examiner Vijay Nagarajan, School of Informatics, University of Edinburgh External Examiner Additional Supervisory Committee Members: Tor Aamodt, Electrical and Computer Engineering Supervisory Committee Member ii Abstract The Graphics Processing Unit (GPU) has become a mainstream computing platform for a wide range of applications. Unlike latency-critical Central Processing Units (CPUs), throughput-oriented GPUs provide high performance by exploiting massive application parallelism. -

CIS 501 Computer Architecture This Unit: Shared Memory

This Unit: Shared Memory Multiprocessors App App App • Thread-level parallelism (TLP) System software • Shared memory model • Multiplexed uniprocessor CIS 501 Mem CPUCPU I/O CPUCPU • Hardware multihreading CPUCPU Computer Architecture • Multiprocessing • Synchronization • Lock implementation Unit 9: Multicore • Locking gotchas (Shared Memory Multiprocessors) • Cache coherence Slides originally developed by Amir Roth with contributions by Milo Martin • Bus-based protocols at University of Pennsylvania with sources that included University of • Directory protocols Wisconsin slides by Mark Hill, Guri Sohi, Jim Smith, and David Wood. • Memory consistency models CIS 501 (Martin): Multicore 1 CIS 501 (Martin): Multicore 2 Readings Beyond Implicit Parallelism • Textbook (MA:FSPTCM) • Consider “daxpy”: • Sections 7.0, 7.1.3, 7.2-7.4 daxpy(double *x, double *y, double *z, double a): for (i = 0; i < SIZE; i++) • Section 8.2 Z[i] = a*x[i] + y[i]; • Lots of instruction-level parallelism (ILP) • Great! • But how much can we really exploit? 4 wide? 8 wide? • Limits to (efficient) super-scalar execution • But, if SIZE is 10,000, the loop has 10,000-way parallelism! • How do we exploit it? CIS 501 (Martin): Multicore 3 CIS 501 (Martin): Multicore 4 Explicit Parallelism Multiplying Performance • Consider “daxpy”: • A single processor can only be so fast daxpy(double *x, double *y, double *z, double a): • Limited clock frequency for (i = 0; i < SIZE; i++) • Limited instruction-level parallelism Z[i] = a*x[i] + y[i]; • Limited cache hierarchy • Break it -

Shared-Memory Multiprocessors Gates & Transistors

This Unit: Shared Memory Multiprocessors Application • Three issues OS • Cache coherence Compiler Firmware CIS 501 • Synchronization • Memory consistency Introduction To Computer Architecture CPU I/O Memory • Two cache coherence approaches • “Snooping” (SMPs): < 16 processors Digital Circuits • “Directory”/Scalable: lots of processors Unit 11: Shared-Memory Multiprocessors Gates & Transistors CIS 501 (Martin/Roth): Shared Memory Multiprocessors 1 CIS 501 (Martin/Roth): Shared Memory Multiprocessors 2 Readings Thread-Level Parallelism struct acct_t { int bal; }; • H+P shared struct acct_t accts[MAX_ACCT]; • Chapter 6 int id,amt; 0: addi r1,accts,r3 if (accts[id].bal >= amt) 1: ld 0(r3),r4 { 2: blt r4,r2,6 accts[id].bal -= amt; 3: sub r4,r2,r4 spew_cash(); 4: st r4,0(r3) } 5: call spew_cash • Thread-level parallelism (TLP) • Collection of asynchronous tasks: not started and stopped together • Data shared loosely, dynamically • Example: database/web server (each query is a thread) • accts is shared, can’t register allocate even if it were scalar • id and amt are private variables, register allocated to r1, r2 • Focus on this CIS 501 (Martin/Roth): Shared Memory Multiprocessors 3 CIS 501 (Martin/Roth): Shared Memory Multiprocessors 4 Shared Memory Shared-Memory Multiprocessors • Shared memory • Provide a shared-memory abstraction • Multiple execution contexts sharing a single address space • Familiar and efficient for programmers • Multiple programs (MIMD) • Or more frequently: multiple copies of one program (SPMD) P1 P2 P3 P4 • Implicit (automatic) communication via loads and stores + Simple software • No need for messages, communication happens naturally – Maybe too naturally • Supports irregular, dynamic communication patterns Memory System • Both DLP and TLP – Complex hardware • Must create a uniform view of memory • Several aspects to this as we will see CIS 501 (Martin/Roth): Shared Memory Multiprocessors 5 CIS 501 (Martin/Roth): Shared Memory Multiprocessors 6 Shared-Memory Multiprocessors Paired vs. -

Tardis: Time Traveling Coherence Algorithm for Distributed Shared Memory

Tardis: Time Traveling Coherence Algorithm for Distributed Shared Memory Xiangyao Yu Srinivas Devadas CSAIL, MIT CSAIL, MIT Cambridge, MA, USA Cambridge, MA, USA [email protected] [email protected] Abstract—A new memory coherence protocol, Tardis, is pro- requiring a globally synchronized clock unlike prior timestamp posed. Tardis uses timestamp counters representing logical time coherence schemes (e.g., [9], [10]), and without requiring as well as physical time to order memory operations and enforce multicast/broadcast support unlike prior directory coherence sequential consistency in any type of shared memory system. Tardis is unique in that as compared to the widely-adopted schemes (e.g., [11], [12]). In Tardis, only the timestamps directory coherence protocol, and its variants, it completely and the owner ID need to be stored for each address for a avoids multicasting and only requires O(log N) storage per O(log N) cost where N is the number of processors or cores; cache block for an N-core system rather than O(N) sharer the O(N) sharer information of common directory protocols information. Tardis is simpler and easier to reason about, yet is not required. The requirement of storing sharers is avoided achieves similar performance to directory protocols on a wide range of benchmarks run on 16, 64 and 256 cores. partly through the novel insight that a writer can instantly jump 1 Index Terms—coherence; timestamp; scalability; sequential ahead to a time when the sharer copies have expired and consistency; immediately perform the write without violating sequential consistency. A formal proof that Tardis satisfies sequential I. -

Gpgpu & Accelerators

Bimalee Salpitikorala Thilina Gunarathne GPGPU & ACCELERATORS CPU . Optimized for sequential performance . Extracting Instruction level parallelism is difficult Control hardware to check for dependencies, out-of-order execution, prediction logic etc . Control hardware dominates CPU Complex, difficult to build and verify . Does not do actual computation but consumes power . Pollack’s Rule Performance ~ sqrt(area) To increase sequential performance 2 times, area 4 times Increase performance using 2 cores, area only 2 times GPU . High-performance many-core processors . Data Parallelized Machine -SIMD Architecture . Less control hardware . High computational performance GPU vs CPU GFLOPS graph http://courses.ece.illinois.edu/ece498/al/textbook/Chapter1-Introduction.pdf GPU - Accelerator? No, not this .... Accelerator? . Speed up some aspect of the computing workload . Implemented as a coprocessor to the host- Its own instruction set Its own memory (usually but not always). To the hardware - another IO unit . To the software – another computer . Today's accelerators Sony/Toshiba/IBM Cell Broadband Engine GPUs How the GPU Fits into the Overall Computer System Graphics pipeline GPU Architecture http://http.download.nvidia.com/developer/GPU_Gems_2/GPU_Gems2_ch30.pdf GPU Pipeline . CPU to GPU data transfer . Vertex processing . Cull / Clip /Set up . Rasterization . Texture & Fragment processing . Compare & blend CPU to GPU data transfer . Through a graphics connector PCI Express AGP slot on the motherboard . Graphics connector transfers properties at the end points (vertices) or control points of the geometric primitives ( lines and triangles). The type of properties provided per vertex x-y-z coordinates RGB values Texture Reflectivity etc.. Vertex processing Vertex processor/vertex shaders http://http.download.nvidia.com/developer/GPU_Gems_2/GPU_Gems2_ch30.pdf Cull/ Clip/ Set up . -

CIS 501 Computer Architecture This Unit: Shared Memory Multiprocessors Readings Multiplying Performance

This Unit: Shared Memory Multiprocessors App App App •! Thread-level parallelism (TLP) System software •! Shared memory model •! Multiplexed uniprocessor CIS 501 Mem CPUCPU I/O CPUCPU •! Hardware multihreading CPUCPU Computer Architecture •! Multiprocessing •! Synchronization •! Lock implementation Unit 9: Multicore •! Locking gotchas (Shared Memory Multiprocessors) •! Cache coherence •! Bus-based protocols •! Directory protocols •! Memory consistency models CIS 501 (Martin/Roth): Multicore 1 CIS 501 (Martin/Roth): Multicore 2 Readings Multiplying Performance •! H+P •! A single processor can only be so fast •! Chapter 4 •! Limited clock frequency •! Limited instruction-level parallelism •! Limited cache hierarchy •! What if we need even more computing power? •! Use multiple processors! •! But how? •! High-end example: Sun Ultra Enterprise 25k •! 72 UltraSPARC IV+ processors, 1.5Ghz •! 1024 GBs of memory •! Niche: large database servers •! $$$ CIS 501 (Martin/Roth): Multicore 3 CIS 501 (Martin/Roth): Multicore 4 Multicore: Mainstream Multiprocessors Application Domains for Multiprocessors •! Multicore chips •! Scientific computing/supercomputing •! IBM Power5 •! Examples: weather simulation, aerodynamics, protein folding Core 1 Core 2 •! Two 2+GHz PowerPC cores •! Large grids, integrating changes over time •! Shared 1.5 MB L2, L3 tags •! Each processor computes for a part of the grid •! AMD Quad Phenom •! Server workloads •! Four 2+ GHz cores •! Example: airline reservation database 1.5MB L2 •! Per-core 512KB L2 cache •! Many concurrent -

Snooping Cache Coherence I

Lecture 10: Cache Coherence: Part I CMU 15-418: Parallel Computer Architecture and Programming (Spring 2012) Shared memory multi-processor ▪ Processors read and write to shared variables - More precisely: processors issues load and store instructions ▪ Intuitively... reading value at address should return the last value written at the address by any processor Processor Processor Processor Processor Interconnect Memory I/O (CMU 15-418, Spring 2012) The cache coherence problem Modern processors replicate contents of memory in local caches Result of writes: processors can have different values for the same memory location Processor Processor Processor Processor Cache Cache Cache Cache Interconnect Memory I/O int foo; (stored at address X) Action P1 $ P2 $ P3 $ P4 $ mem[X] 0 P1 load X 0 miss 0 P2 load X 0 0 miss 0 P1 store X 1 0 0 Chart shows value of foo (variable stored P3 load X 1 0 0 miss 0 at address X) stored in main memory and in P3 store X 1 0 2 0 each processor’s cache ** P2 load X 1 0 hit 2 0 ** Assumes write-back cache behavior P1 load Y 0 2 1 (say this load causes eviction of foo) (CMU 15-418, Spring 2012) The cache coherence problem ▪ Reading value at address X should return the last value written at address X by any processor. ▪ Coherence problem exists because there is both global state (main memory) and local state (contents of private processor caches). (CMU 15-418, Spring 2012) Cache hierarchy of Intel Core i7 64 byte cache line size L3: (per chip) Review: key terms Shared L3 Cache 8 MB, inclusive 16-way set associative (One bank per core) 32B / clock per bank - cache line 26-31 cycle latency - write back vs. -

Memory Coherence in Shared Virtual Systems

Memory Coherence in Shared Virtual Memory Systems 1 Kai Li and Paul Hudak Department of Computer Science Yale University New Haven, CT 06520 Abstract The shared virtual memory that we will describe not only "pages" data between physical memories and disks, This paper studies the memory coherence problem in de- as in a conventional virtual memory system, but it also signing and implementing a shared virtual memory on loosely- "pages" data between the physical memories of the individ- coupled multiprocessors. Two classes of algorithms for solv- ual processors. Thus data can naturally migrate between ing the problem are presented. A prototype shared virtual processors on demand. Furthermore, just as a conventional memory on an Apollo ring has been implemented based v irtual memory also pages processes, so does the shared vir- on these algorithms. Both theoretical and practical results tual memory. Thus our approach provides a very natural show that the memory coherence problem can indeed be and efficient form of process migration between processors solved efficiently on a loosely-coupled multiprocessor. in a distributed system, normally a very difficult feature to implement well (and in effect subsuming the notion of 1 Introduction remote procedure call). The benefits of a virtual memory go without saying, and almost every high-performance sequential computer in ex- l CPU 1 CPU 2 CPU N / istence today incorporates one. Virtual memories are so useful that it is hard to believe that parallel architectures Memory 1 Memory 2 Memory N would not also benefit from them. Indeed, one can easily imagine how virtual memory would be incorporated into a I " / / shared-memory parallel machine, since the memory hierar- \ x \ I , \ / r chy need not be much different from that of a sequential N \ / / machine. -

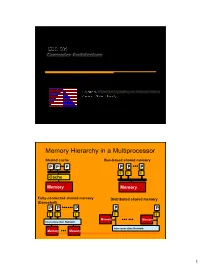

Introduction and Cache Coherency

EEC 581 Computer Architecture Multiprocessor and Memory Coherence Department of Electrical Engineering and Computer Science Cleveland State University Memory Hierarchy in a Multiprocessor Shared cache Bus-based shared memory P P P P P P $ $ $ Cache Memory Memory Fully-connected shared memory Distributed shared memory (Dancehall) P P P P P $ $ $ $ $ Memory Memory Interconnection Network Interconnection Network Memory Memory 2 1 Cache Coherency Closest cache level is private Multiple copies of cache line can be present across different processor nodes Local updates Lead to incoherent state Problem exhibits in both write-through and writeback caches Bus-based globally visible Point-to-point interconnect visible only to communicated processor nodes 3 Example (Writeback Cache) P P P Rd? Rd? Cache Cache Cache X= -100 X= -100 X=X= - 100505 X= -100 Memory 4 2 Example (Write-through Cache) P P P Rd? Cache Cache Cache X= -100 X= 505 X=X= - 100505 X=X= -505100 Memory 5 Defining Coherence An MP is coherent if the results of any execution of a program can be reconstructed by a hypothetical serial order Implicit definition of coherence Write propagation Writes are visible to other processes Write serialization All writes to the same location are seen in the same order by all processes (to “all” locations called write atomicity) E.g., w1 followed by w2 seen by a read from P1, will be seen in the same order by all reads by other processors Pi 6 3 Sounds Easy? A=0 B=0 P0 P1 P2 P3 T1 A=1 B=2 T2 A=1 A=1 B=2 B=2 T3 A=1 A=1 B=2 B=2 B=2 A=1