Suppressing Voltage Spikes of MOSFET in H-Bridge Inverter Circuit

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

EMP Information and a Site That You Can Research to Find More Information on Faraday Cages, Which Most of You Guys and Gals Have Heard About Already

This is a good read with lots of information bout EMP related information. I got this information of this link and just consolidated it without all the pictures. http://www.bioprepper.com/2015/07/11/emp-101everything-you-need-to-know-about-emphemp-and- how-to-guard-against-it/ LENGTHENED LIST OF ITEMS IN PREPARATION OF AN E.M.P. SCENARIO EMPAUGUST 6, 2014BY BIO PREPPER Items may be added to this list at later times. Be sure to check back for future add-ons. Necessities and Consumables -food supply for a year (including food for any livestock or house animals) -water supply for three months, one gallon per person per day, for washing and cooking as well as drinking -gasoline for all vehicles that would still work and for the gas powered electrical generator -large quantities of iodized salt -large quantities of chlorine tablets and bleach for purifying water -batteries for any electronics that may still work -a year supply of bar soap and shampoo (if you are dirty for too long you can catch/spread disease) -a tooth brush and as much toothpaste as you can get Tools -an ax with a strong handle (not wooden) -a hammer and nails -hand saw -lumber for various repairs and home defense needs (trees will also work, sorry tree huggers) -multiple cheap flashlights -One good flashlight (such as a Mag-lite or Mag-LED) -if possible, an old radio that uses vacuum tubes and batteries -multiple lighters -gas/dynamo powered electrical generators (do NOT leave these plugged in) Weapons -small handgun (preferred .45 caliber) -shotgun (12 or 20 gauge) -bolt action or semi-automatic rifle with a scope (preferred .223 for semi-auto or 30-06 for bolt action) -as much ammunition for each weapon as you can get -a knife with a 6-8 inch blade with a belt sheath -a bow or crossbow with reusable arrows or bolts Commodities -if you can afford it, an All-terrain vehicle that seats four people and has room for storage, like a small truck bed in the back -a pretty good amount of cash, not only for the initial start of an E.M.P. -

Power Quality Issues and It's Mitigation Techniques

Tejashree G. More et al. Int. Journal of Engineering Research and Applications www.ijera.com ISSN : 2248-9622, Vol. 4, Issue 4( Version 4), April 2014, pp.170-177 RESEARCH ARTICLE OPEN ACCESS Power Quality Issues and It’s Mitigation Techniques Tejashree G. More*, Pooja R. Asabe**,Prof. Sandeep Chawda*** *(Department of Electrical Engineering, Bhivarabai Sawant Institude Of Technology and Research(w), Wagholi, Pune, India) ** (Department of Electrical Engineering, Bhivarabai Sawant Institude Of Technology and Research(w), Wagholi, Pune, India) ***(Department of Electrical Engineering, Bhivarabai Sawant Institude Of Technology and Research(w), Wagholi, Pune, India) ABSTRACT In this paper the main power quality (PQ) problems are presented with there associated causes and consequences. The economic impact associated with PQ are characterized. Also this paper tries to give the solution for reducing the losses produced because of harmonics and increasing the quality of power at consumers’ side. Keywords –Flywheel, Harmonics, Power Quality, Power Quality Cost, Supercapacitors. I. INTRODUCTION Nowadays, reliability and quality of electric customer perspective, a PQ problem is defined as any power is one of the most discuss topics in power power problem manifested in voltage, current, or industry. There are numerous types of Quality issues frequency deviations that result in power failure or and problems and each of them might have varying misoperation of customer of equipment. Fig. 1 and diverse causes. The types of Power Quality describe the demarcation of the various PQ issues problems that a customer may encounter classified defined by IEEE Std. 1159-1995. depending on how the voltage waveform is being Fig 1. -

Emergency Management Plan to Increase Resilience in Transportation Sector Vehicles to an EMP Attack

Department of Fire Science and Emergency Management Emergency Management Plan to Increase Resilience in Transportation Sector Vehicles to an EMP Attack Thesis Submitted in partial fulfillment of the requirements for the degree of Master of Science in Emergency Management By Julian A. LoRusso University of New Haven West Haven, Connecticut November 04, 2020 1 APPROVALS I am sincerely grateful for the valuable comments from my advisor, the committee members, and the department chairperson in completion of this document. Their contributions were clearly an asset in the achievement of the goals of this Study. Thesis Advisor Approval: Mariama Yakubu Mariama Yakubu (Nov 15, 2020 06:50 EST) Mariama Yakubu, Ph.D. - Lecturer (UNH Fire Science & Emergency Management Department) Committee Member Approvals: JEFFREY TREISTMAN JEFFREY TREISTMAN (Nov 15, 2020 17:39 EST) Jeff Triestman, Ph. D. – Assistant Professor (UNH National Security Department, Graduate Program Director) Edward M. Goldberg, DM Edward M. Goldberg, DM (Nov 15, 2020 20:16 EST) Ed Goldberg, Ph. D. – Manager, retired (Eversource, Inc., Business Continuity, Disaster Recovery and Threat Assessment Dept.) Matt Van Benschoten Matt Van Benschoten (Nov 15, 2020 22:11 EST) Mr. Matt Van Benschoten - Vice President (Roush Industries, Inc., Advanced Engineering) University Approvals: Wayne Sandford Wayne Sandford (Nov 16, 2020 08:00 EST) Mr. Wayne Sandford – Lecturer, Emergency Management Program Coordinator (Fire Sciences & Emergency Management Department) David A. Schroeder, Ph. D. - Dean (Henry C. Lee College of Criminal Justice and Forensic Sciences) Mario Thomas Gaboury Mario Thomas Gaboury (Nov 17, 2020 16:59 EST) Mario Thomas Gaboury, J.D., Ph.D. – Provost (University of New Haven) 2 ACKNOWLEDGEMENTS In addition to input from the committee members, I would also like to acknowledge the help from the following individuals for their input in the completion of this report: • Mr. -

The X-Chapters 9X.6 Transformer + Rectifier + Capacitor = Giant Spikes!

Art of Electronics – The x-Chapters abruptly (V = LdI/dt again), and respond by increasing the voltage to maintain continuity of current. In this case that means a negative voltage spike at the transformer sec- 9x.6 Transformer + Rectifier + Capacitor = ondary. Giant Spikes! The effect can be quite large. Fig. 9x.24 shows mea- sured waveforms for a 10 V unregulated half-wave rectifier circuit. We used a Signal Transformer Co. “split bobbin” type, designed for good isolation (low inter-winding ca- pacitance, high breakdown voltage), whose reduced wind- Most designers don’t realize that a simple linear un- ing coupling results in significant leakage inductance. The regulated dc supply can (and often does) generate large diode was a 1N4001 (1 A conventional rectifier), the fil- microsecond-scale spikes, at the powerline frequency; ter capacitor was 3,300 μF electrolytic, and the load was these generate a buzzing sound in low-level audio circuits, a20Ω resistor. You can see the flattening of transformer and generally create havoc. They’re easily tamed, once you output (with its series L and winding resistance), and the know about them. L diode current causing capacitor charging; the mischievous spike occurs when the current goes to zero. The expanded trace (Fig. 9x.24B) shows that the diode current goes neg- 120Vac + C I in RLOAD L ative for about 8 μs before abruptly ceasing (or trying to, anyway!), at which point the spike erupts. t L V ℓ Rsec Lℓ 9x.6.2 Calculations and cures V sec Cwinding For low-voltage unregulated supplies you can use Schot- nsec = Vpri × tky rectifiers to prevent this effect. -

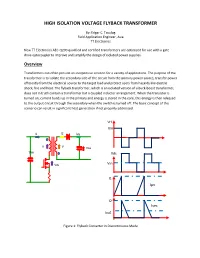

High Isolation Flyback Transformer Technical Article

HIGH ISOLATION VOLTAGE FLYBACK TRANSFORMER By: Edgar C. Taculog Field Application Engineer, Asia TT Electronics New TT Electronics AEC-Q200 qualified and certified transformers are optimized for use with a gate- drive optocoupler to improve and simplify the design of isolated power supplies. Overview Transformers can often provide an inexpensive solution for a variety of applications. The purpose of the transformer is to isolate the secondary side of the circuit from the primary power source, transfer power efficiently from the electrical source to the target load and protect users from hazards like electric shock, fire and heat. The flyback transformer, which is an isolated version of a buck-boost transformer, does not in truth contain a transformer but a coupled inductor arrangement. When the transistor is turned on, current builds up in the primary and energy is stored in the core, this energy is then released to the output circuit through the secondary when the switch is turned off. The basic concept of this scenario can result in significant heat generation if not properly addressed. V1 Vin I1 I2 Iou t V V Vou 1 2 Vin t Vds Vds Vin I1 Ipri I2 Isec Iout Figure 1: Flyback Converter in Discontinuous Mode The HA00-10043ALFTR and HA00-14013LFTR line of transformers are designed specifically for use with Avago’s ACPL-32JT and ACPL-302J optocoupler ICs for automotive and industrial application respectively. The Avago devices are specifically used in a wide variety of applications that require high galvanic isolation so in designing these transformers materials that can meet the necessary creepage and clearance distances between conductors were taken into consideration. -

AUMOV® & LV Ultramov™ Varistor Design Guide for DC & Automotive Applications

AUMOV® & LV UltraMOV™ Varistor Design Guide for DC & Automotive Applications High Surge Current Varistors Design Guide for Automotive AUMOV® Varistor & LV UltraMOV™ Varistor Series Table of Contents Page About the AUMOV® Varistor Series 3-4 About the LV UltraMOV™ Series Varistor 5-6 Varistor Basic 6 Terminology Used in Varistor Specifications 7 Automotive MOV Background and Application Examples 8-10 LV UltraMOV™ Varistor Application Examples 11- 12 How to Select a Low Voltage DC MOV 13-15 Transient Suppression Techniques 16-17 Introduction to Metal Oxide Varistors (MOVs) 18 Series and Parallel Operation of Varistors 19-20 AUMOV® Varistor Series Specifications and Part Number Cross-References 21-22 LV UltraMOV™ Series Specifications and Part Number Cross-References 23-26 Legal Disclaimers 27 © 2015 Littelfuse, Inc. Specifications descriptions and illustrative material in this literature are as accurate as known at the time of publication, but are subject to changes without notice. Visit littelfuse.com for more information. DC Application Varistor Design Guide About the AUMOV® Varistor Series About the AUMOV® Varistor Series The AUMOV® Varistor Series is designed for circuit protection in low voltage (12VDC, 24VDC and 42VDC) automotive systems. This series is available in five disc sizes with radial leads with a choice of epoxy or phenolic coatings. The Automotive MOV Varistor is AEC-Q200 (Table 10) compliant. It offers robust load dump, jump start, and peak surge current ratings, as well as high energy absorption capabilities. These devices -

(12) Patent Application Publication (10) Pub. No.: US 2016/0120075 A1 Logan Et Al

US 2016O1 20075A1 (19) United States (12) Patent Application Publication (10) Pub. No.: US 2016/0120075 A1 Logan et al. (43) Pub. Date: Apr. 28, 2016 (54) ELECTROMAGNETIC PULSE PROTECTED Publication Classification HARD DRIVE (51) Int. C. (71) Applicant: Twin Harbor Labs, LLC, Plano, TX H05K 9/00 (2006.01) (US) GIIB 33/14 (2006.01) (52) U.S. C. (72) Inventors: James D. Logan, Candia, NH (US); CPC .......... H05K 9/0007 (2013.01); GII B33/1493 Garrett Malagodi, Durham, NH (US); (2013.01) Richard A. Baker, JR., West Newbury, MA (US); David Lentini, North Berwick, ME (US) (57) ABSTRACT (73) Assignee: TWIN HARBORLABS, LLC, Plano, TX (US) A computer storage system protected from electromagnetic Appl. No.: 14/880,760 pulses is described. The storage system utilizes either a hard (21) drive or a solid state drive to hold the data. The device uses (22) Filed: Oct. 12, 2015 fiber optics to transfer data and is powered by either a Power over Fiber system or by a switched battery system. The device Related U.S. Application Data protects against radiation, magnetic pulses, and electronic (60) Provisional application No. 62/062.999, filed on Oct. pulses using an enclosure that incorporates a faraday cage, a 13, 2014. radiation shield, and/or a magnetic shield. N EMP Detonation SS S. S S.S S S. SSsanxss S. s s s Ne s Earth Patent Application Publication Apr. 28, 2016 Sheet 1 of 4 US 2016/01 2007S A1 5. S:S : S: S : S: S3S S 3 S : S : S S : S: S SS. -

How to Select a Surge Diode

Application Report SLVAE37–January 2019 How to select a Surge Diode Alec Forbes ABSTRACT For systems in harsh industrial environments, one of the most important parts of system protection is the input TVS diode selection. The input TVS diode is designed to protect fragile system inputs from large transient spikes that are caused by nearby machinery, lightning strikes, or power surges. These surges are modeled and regulated by IEC 61000-4-5, which standardizes the protection requirements systems must meet in order to ensure that they will not see failures when exposed to these transients. However, passing these standards is not trivial, especially to a designer who is unfamiliar with protection diodes and the specifications. This document will provide an introduction to TVS diodes, comparing them to other transient protection solutions, discussing some of the key specifications and then providing a system example. An understanding of these specifications will allow a designer to have a more solid fundamental understanding of how to select a TVS diode for surge protection, which will directly translate to a more robust system. Contents 1 Types of Transient Suppression Components ........................................................................... 1 2 TVS Diode Specifications................................................................................................... 2 3 Example: Selecting a TVS for a PLC 4/20 mA Input.................................................................... 6 4 Conclusion ................................................................................................................... -

AC Line Voltage Transients and Their Suppression

AC Line Voltage Transients and Their Suppression Application Note January 1998 AN9308.2 Introduction 1. 103 The increasing usage of sensitive solid state devices in HIGH EXPOSURE modem electrical systems, particularly computers, 102 communications systems and military equipment, has given MEDIUM [ /Title rise to concerns about system reliability. These concerns EXPOSURE stem from the fact that the solid state devices are very 101 (AN93 susceptible to stray electrical transients which may be 08) present in the distribution system. /Sub- 1 The initial use of semiconductor devices resulted in a (SEE NOTE) SPARKOVER OF CLEARANCES ject number of unexplained failures. Investigation into these 10-1 (AC failures revealed that they were caused by transients, which SURGE CREST OF ABSCISSA LOW Line were present In many different forms in the system. EXPOSURE -2 Volt- Transients in an electrical circuit result from tile sudden YEAR EXCEEDING NUMBER OF SURGES PER 10 release of previously stored energy. The severity of, and 0.3 0.5 1 2 5 10 20 age SURGE CREST (kV) Tran- hence the damage caused by transients depends on their frequency of occurrence, the peak transient currents and NOTE: In some locations, sparkover of clearances may limit the sients voltages present and their waveshapes. overvoltages. and In order to adequately protect sensitive electrical systems, FIGURE 1. RATE OF SURGE OCCURRENCES vs VOLTAGE Their LEVEL AT UNPROTECTED LOCATIONS thereby assuring reliable operation, transient voltage Sup- suppression must be part of the initial design process and pres- not simply included as an afterthought. To ensure effective The low exposure portion of the graph Is derived from data sion) transient suppression, the device chosen must have the collected in geographical areas known for low lightning /Autho capability to dissipate the impulse energy of the transient at activity, with little load switching activity. -

Understanding Electrical Terms

Understanding Electrical Terms ® Understanding Electrical Terms In today’s computer-intensive work environments, a critical issue is clean, reliable power. Haworth is the industry leader in furniture-based power solutions. The ability to handle any power requirement is an important component in Haworth’s mission to completely satisfy customers’ needs. This booklet is designed to help you become familiar with electrical terms commonly used in the contract furniture industry. You’ll find descriptions of specific Haworth electrical products as well. Having a working knowledge of these terms and descrip- tions will help you understand Haworth’s furniture-based power capabilities. Remember, Haworth field sales engineers are also always ready and available to answer specific customer inquiries. Use this booklet to become conversant in the language of power, and as a companion to the other Haworth booklets on electrical topics: “Using the 6-Circuit Power Base,” “Complying with Electrical Standards,” and “Interfacing with Building Power.” Table of Contents Industry-Common Electrical Terms . 2-15 Access Flooring Floor Duct Power Zone Ampacity Floor Monument/Floor Access Receptacle Outlet Amperage, Ampere, Amp Ground Conductor Separate Neutral Balancing, Load Balancing Harmonic Currents, Harmonics Shared Neutral Ballast Hot Conductor Short Circuit Branch Circuit Inspector Surge Protector, Spike Protector Circuit Isolated Ground Terminal Circuit Breaker(s) Junction Box Three-Phase Power Clean Power Load 3+D Circuit Configuration Codes, Local Electrical -

Transient Suppression Products Catalog

Transient Suppression Products 022221-1 IMPORTANT INFORMATION/DISCLAIMER All product specifications, statements, information and data (collectively, the “Information”) in this datasheet or made available on the website are subject to change. The customer is responsible for checking and verifying the extent to which the Information contained in this publication is applicable to an order at the time the order is placed. All Information given herein is believed to be accurate and reliable, but it is presented without guarantee, warranty, or responsibility of any kind, expressed or implied. Statements of suitability for certain applications are based on AVX’s knowledge of typical operating conditions for such applications, but are not intended to constitute and AVX specifically disclaims any warranty concerning suitability for a specific customer application or use. ANY USE OF PRODUCT OUTSIDE OF SPECIFICATIONS OR ANY STORAGE OR INSTALLATION INCONSISTENT WITH PRODUCT GUIDANCE VOIDS ANY WARRANTY. The Information is intended for use only by customers who have the requisite experience and capability to determine the correct products for their application. Any technical advice inferred from this Information or otherwise provided by AVX with reference to the use of AVX’s products is given without regard, and AVX assumes no obligation or liability for the advice given or results obtained. Although AVX designs and manufactures its products to the most stringent quality and safety standards, given the current state of the art, isolated component failures may still occur. Accordingly, customer applications which require a high degree of reliability or safety should employ suitable designs or other safeguards (such as installation of protective circuitry or redundancies) in order to ensure that the failure of an electrical component does not result in a risk of personal injury or property damage. -

Electromagnetic Compatibility Testing for Conducted Susceptibility Along Interconnecting Signal Lines

NUREG/CR-5609 ORNL/TM-13705 Electromagnetic Compatibility Testing for Conducted Susceptibility Along Interconnecting Signal Lines Final Report Oak Ridge National Laboratory U.S. Nuclear Regulatory Commission Office of Nuclear Regulatory Research Washington, DC 20555-0001 NUREG/CR-5609 ORNL/TM-13705 Electromagnetic Compatibility Testing for Conducted Susceptibility Along Interconnecting Signal Lines Final Report Manuscript Completed: May 2003 Date Published: August 2003 Prepared by P.D. Ewing, R.T. Wood, K. Korsah, A.A. Shourbaji, T.L. Wilson, B.M. Beets Oak Ridge National Laboratory Managed by UT-Battelle, LLC Oak Ridge, TN 37831-6010 C. E. Antonescu, NRC Project Manager Prepared for Division of Engineering Technology Office of Nuclear Regulatory Research U.S. Nuclear Regulatory Commission Washington, DC 20555-0001 NRC Job Code Y6272 ABSTRACT This document presents recommendations and the associated technical basis for addressing the effects of conducted electromagnetic interference (EMI) and radio-frequency interference (RFI) along interconnecting signal lines in safety-related instrumentation and control (I&C) systems. Oak Ridge National Laboratory has been engaged in assisting the U.S. Nuclear Regulatory Commission Office of Nuclear Regulatory Research in developing the technical basis for regulatory guidance on EMI/RFI immunity and power surge withstand capability (SWC). Previous research efforts have provided recommendations on (1) electromagnetic compatibility design and installation practices, (2) the endorsement of EMI/RFI and SWC test criteria and test methods, (3) the determination of ambient electromagnetic conditions at nuclear power plants, and (4) the development of recommended electromagnetic operating envelopes applicable to locations where safety-related I&C systems will be installed. The current research focuses on the susceptibility of I&C systems to conducted EMI/RFI along interconnecting signal lines.